# Synthesis and Verification of Digital Circuits using Functional Simulation and Boolean Satisfiability

by

Stephen M. Plaza

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science and Engineering) in The University of Michigan 2008

**Doctoral Committee:**

Associate Professor Igor L. Markov, Co-Chair Assistant Professor Valeria M. Bertacco, Co-Chair Professor John P. Hayes Professor Karem A. Sakallah Associate Professor Dennis M. Sylvester

To my family, friends, and country

### ACKNOWLEDGEMENTS

I would like to thank my advisers, Professor Igor Markov and Professor Valeria Bertacco, for inspiring me to consider various fields of research and providing feedback on my projects and papers. I also want to thank my defense committee for their comments and insights: Professor John Hayes, Professor Karem Sakallah, and Professor Dennis Sylvester. I would like to thank Professor David Kieras for enhancing my knowledge and appreciation for computer programming and providing invaluable advice.

Over the years, I have been fortunate to know and work with several wonderful students. I have collaborated extensively with Kai-hui Chang and Smita Krishnaswamy and have enjoyed numerous research discussions with them and have benefited from their insights. I would like to thank Ian Kountanis and Zaher Andraus for our many fun discussions on parallel SAT. I also appreciate the time spent collaborating with Kypros Constantinides and Jason Blome. Although I have not formally collaborated with Ilya Wagner, I have enjoyed numerous discussions with him during my doctoral studies. I also thank my office mates Jarrod Roy, Jin Hu, and Hector Garcia.

Without my family and friends I would never have come this far. I would like to thank Geoff Blake and Smita Krishnaswamy, who have been both good friends and colleagues and who have talked to me often when the stress at work was overwhelming. I also want to thank Geoff for his patience being my roommate for so many years. I am blessed to also have several good friends outside of the department who have provided me a lot of support: Steve Kibit (Steve<sup>2</sup> representin'), Rob Denis, and Jen Pileri.

Most of all, I would like to thank my family who has been an emotional crutch for me. My mom, dad, and brother Mark have all been supportive of my decision to go for a PhD and have continuously encouraged me to strive for excellence.

### PREFACE

The semiconductor industry has long relied on the steady trend of transistor scaling, that is, the shrinking of the dimensions of silicon transistor devices, as a way to improve the cost and performance of electronic devices. However, several design challenges have emerged as transistors have become smaller. For instance, wires are not scaling as fast as transistors, and delay associated with wires is becoming more significant. Moreover, in the design flow for integrated circuits, accurate modeling of wire-related delay is available only toward the end of the design process, when the physical placement of logic units is known. Consequently, one can only know whether timing performance objectives are satisfied, *i.e.*, if timing closure is achieved, after several design optimizations. Unless timing closure is achieved, time-consuming design-flow iterations are required. Given the challenges arising from increasingly complex designs, failing to quickly achieve timing closure threatens the ability of designers to produce high-performance chips that can match continually growing consumer demands.

In this dissertation, we introduce powerful constraint-guided synthesis optimizations that take into account upcoming timing closure challenges and eliminate expensive design iterations. In particular, we use logic simulation to approximate the behavior of increasingly complex designs leveraging a recently proposed concept, called *bit signatures*, which allows us to represent a large fraction of a complex circuit's behavior in a com-

pact data structure. By manipulating these signatures, we can efficiently discover a greater set of valid logic transformations than was previously possible and, as a result, enhance timing optimization. Based on the abstractions enabled through signatures, we propose a comprehensive suite of novel techniques: (1) a fast computation of circuit don't-cares that increases restructuring opportunities, (2) a verification methodology to prove the correctness of speculative optimizations that efficiently utilizes the computational power of modern multi-core systems, and (3) a physical synthesis strategy using signatures that re-implements sections of a critical path while minimizing perturbations to the existing placement. Our results indicate that logic simulation is effective in approximating the behavior of complex designs and enables a broader family of optimizations than previous synthesis approaches.

### TABLE OF CONTENTS

| DEDICATION            | ii                                    |

|-----------------------|---------------------------------------|

| ACKNOWLEDGEMENTS      |                                       |

| <b>PREFACE</b>        | • • • • • • • • • • • • • • • • • • • |

| LIST OF FIGURES       | xi                                    |

| LIST OF TABLES        |                                       |

| LIST OF ABBREVIATIONS |                                       |

| PART                  |                                       |

| Ι | Introdu | ection and Background                                                | 1  |

|---|---------|----------------------------------------------------------------------|----|

|   | Chapte  | r I. Introduction: Overcoming Challenges in Nanometer Design         | 1  |

|   | 1.1     | Trends in the Electronics and EDA Industries                         | 1  |

|   | 1.2     | Challenges in High-Performance Integrated Circuit Design             | 3  |

|   | 1.3     | Bridging the Gap between Logic and Physical Optimizations            | 7  |

|   | 1.4     | Using Simulation-based Abstractions for Circuit Optimizations        | 8  |

|   | 1.5     | Components of Our Simulation-based Framework                         | 10 |

|   | 1.6     | Organization of the Dissertation                                     | 11 |

|   | Chante  | r II. Synergies between Synthesis, Verification, and Functional Sim- |    |

|   | -       |                                                                      | 14 |

|   | 2.1     | Scalable Verification                                                | 15 |

|   |         | 2.1.1 Satisfiability                                                 | 16 |

|   |         | 2.1.2 Previous Parallel SAT Approaches                               | 20 |

|   | 2.2     | Scalable Logic Synthesis                                             | 23 |

|   |         | 2.2.1 Don't Care Analysis                                            | 23 |

|     |        | 2.2.2 Logic Rewriting                                                | 25 |

|-----|--------|----------------------------------------------------------------------|----|

|     | • •    | 2.2.3 Physically-aware Synthesis                                     | 26 |

|     | 2.3    | Logic Simulation and Bit Signatures                                  | 27 |

|     | 2.4    | Summary                                                              | 28 |

|     | Chapte | r III. Challenges to Achieving Design Closure                        | 29 |

|     | 3.1    | Physical Synthesis                                                   | 31 |

|     | 3.2    | Advances in Integrated Circuit Design                                | 35 |

|     | 3.3    | Limitations of Current Industry Solutions                            | 38 |

|     | 3.4    | Contributions of the Dissertation                                    | 39 |

| II  | Impro  | ving the Quality of Functional Simulation                            | 41 |

|     | Chapte | r IV. High-coverage Functional Simulation                            | 42 |

|     | 4.1    | Improving Verification Coverage through Automated Constrained-Random | m  |

|     |        | Simulation                                                           | 44 |

|     | 4.2    | Finding Inactive Parts of a Circuit                                  | 46 |

|     |        | 4.2.1 Toggle Activity of a Signal                                    | 46 |

|     |        | 4.2.2 Toggle Activity of Multiple Bits                               | 48 |

|     | 4.3    | Targeted Re-simulation                                               | 52 |

|     |        | 4.3.1 Random Simulation with SAT                                     | 52 |

|     |        | 4.3.2 Partition-Targeted Simulation                                  | 56 |

|     | 4.4    | Empirical Validation                                                 | 59 |

|     | 4.5    | Concluding Remarks                                                   | 63 |

|     | Chapte | r V. Enhancing Simulation-based Abstractions with Don't Cares .      | 64 |

|     | 5.1    | Encoding Don't Cares in Signatures                                   | 65 |

|     | 5.2    | Global ODC Analysis                                                  | 67 |

|     |        | 5.2.1 Approximate ODC Simulator                                      | 67 |

|     |        | 5.2.2 False Positives and False Negatives                            | 69 |

|     |        | 5.2.3 Analysis and Approximation of ODCs                             | 70 |

|     |        | 5.2.4 Performance of Approximate Simulator                           | 73 |

|     | 5.3    | Concluding Remarks                                                   | 75 |

| III | Impro  | oving the Efficiency of Formal Equivalence Checking                  | 76 |

|     | Chapte | r VI. Incremental Verification with Don't Cares                      | 77 |

|     | 6.1    | Verifying Signature Abstractions                                     | 78 |

| 6.2      | Incremental Equivalence Checking up to Don't Cares                | 81  |

|----------|-------------------------------------------------------------------|-----|

|          | 6.2.1 Moving-dominator Equivalence Checker                        | 81  |

|          | 6.2.2 Verification Algorithm                                      | 82  |

|          | 6.2.3 Calculating Dominators                                      | 84  |

| 6.3      | Concluding Remarks                                                | 85  |

| Chapter  | r VII. Multi-threaded SAT Solving                                 | 87  |

| 7.1      | Parallel-processing Methodologies in EDA                          | 87  |

| 7.2      | Runtime Variability in SAT Solving                                | 91  |

| 7.3      | Scheduling SAT Instances of Varying Difficulty                    | 93  |

| 7.4      | Current Parallel SAT Solvers                                      | 96  |

| 7.5      | Solving Individual Hard Instances in Parallel                     | 97  |

|          | 7.5.1 Search Space Partitioning                                   | 98  |

|          | 7.5.2 Lightweight Parallel SAT                                    | 100 |

| 7.6      | Empirical Validation                                              | 103 |

|          | 7.6.1 Effective Scheduling of SAT Instances                       | 103 |

|          | 7.6.2 Solving Individual Hard Problems                            | 105 |

|          | 7.6.3 Partitioning Strategies                                     | 108 |

|          | 7.6.4 Parallel Learning Strategies                                | 109 |

| 7.7      | Concluding Remarks                                                | 110 |

|          |                                                                   |     |

| iv impro | oving Logic and Physical Synthesis                                | 111 |

| Chapter  | r VIII. Signature-based Manipulations                             | 112 |

| 8.1      | Logic Transformations through Signature Manipulations             | 112 |

| 8.2      | ODC-enhanced Node Merging                                         | 113 |

|          | 8.2.1 Identifying ODC-based Node Mergers                          | 115 |

|          | 8.2.2 Empirical Validation                                        | 117 |

| 8.3      | Determining Logic Feasibility with Signatures                     | 125 |

| 8.4      | Concluding Remarks                                                | 134 |

| Chapter  | r IX. Path-based Physical Resynthesis using Functional Simulation | 136 |

| 9.1      | Logic Restructuring for Timing Applications                       | 138 |

| 9.2      | Identifying Non-monotone Paths                                    | 139 |

|          | 9.2.1 Path Monotonicity                                           | 139 |

|          | 9.2.2 Calculating Non-monotone Factors                            | 141 |

| 9.3      | Physically-aware Logic Restructuring                              | 145 |

| 2.0      | 9.3.1 Subcircuit Extraction                                       | 145 |

|          | 9.3.2 Physically-guided Topology Construction                     | 146 |

| 9.4      | Enhancing Resynthesis through Global Signature Matching | 149 |

|----------|---------------------------------------------------------|-----|

| 9.5      | Empirical Validation                                    | 150 |

|          | 9.5.1 Prevalence of Non-monotonic Interconnect          | 151 |

|          | 9.5.2 Physically-aware Restructuring                    | 152 |

|          | 9.5.3 Comparison with Redundancy Addition and Removal   | 155 |

| 9.6      | Concluding Remarks                                      | 157 |

| Chapter  | X. Conclusions                                          | 158 |

| 10.1     | Summary of Contributions                                | 159 |

| 10.2     | Directions for Future Research                          | 160 |

| INDEX .  |                                                         | 162 |

| BIBLIOGR | АРНУ                                                    | 165 |

### **LIST OF FIGURES**

### Figure

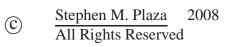

| 1.1 | Transistors manufactured on a single chip over several generations of Intel CPUs.                                                                                                                                                                                                                               | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

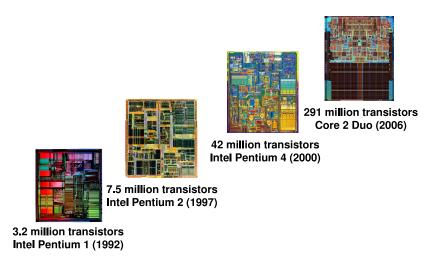

| 1.2 | Transistor scaling projected at future technology nodes                                                                                                                                                                                                                                                         | 4  |

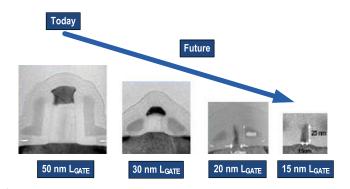

| 1.3 | Major components of multilayer interconnect: single-layer wire seg-<br>ments and inter-layer connectors (vias).                                                                                                                                                                                                 | 4  |

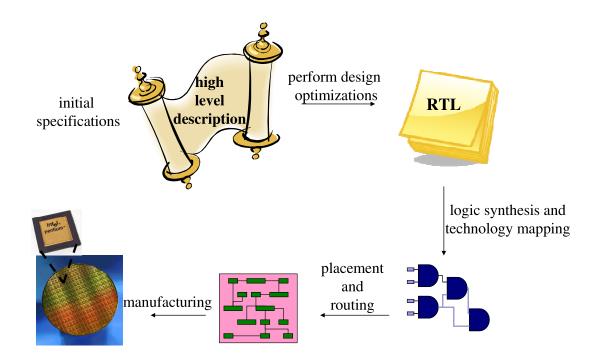

| 1.4 | Typical integrated circuit design flow. The design flow starts from an initial design specification. Several optimization steps are performed, and then a final chip is manufactured.                                                                                                                           | 6  |

| 2.1 | Pseudo-code of the search procedure used in DPLL-SAT. The procedure terminates when it either finds a satisfying assignment or proves that no such solution exists.                                                                                                                                             | 17 |

| 2.2 | An example conflict graph that is the result of the last two clauses in the list conflicting with the current assignment. We show two potential learnt clauses that can be derived from the illustrated cuts. The dotted line closest to the conflict represents the 1-UIP cut, and the other is the 2-UIP cut. | 20 |

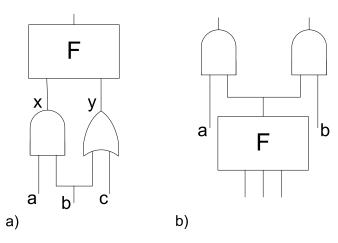

| 2.3 | Satisfiability don't-cares (SDCs) and observability don't-cares (ODCs).<br>a) An example of an SDC. b) An example of an ODC                                                                                                                                                                                     | 24 |

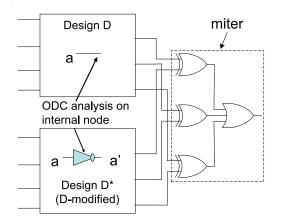

| 2.4 | ODCs are identified for an internal node $a$ in a netlist by creating a mod-<br>ified copy of the netlist where $a$ is inverted and then constructing a miter<br>for each corresponding output. The set of inputs for which the miter<br>evaluates to 1 corresponds to the care-set of that node                | 24 |

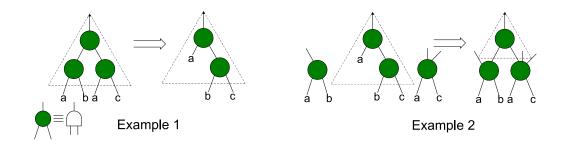

| 2.5 | Two examples of AIG rewriting. In the first example, rewriting results in<br>a subgraph with less nodes than the original. Through structural hashing,<br>external nodes are reused to reduce the size of the subgraph, as shown in<br>the second example.                                                                                                                                                                                           | 26 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

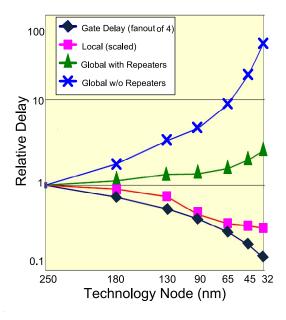

| 3.1 | Delay trends from ITRS 2005. As we approach the 32nm technology node, global and local interconnect delay become more significant compared to gate delay.                                                                                                                                                                                                                                                                                            | 30 |

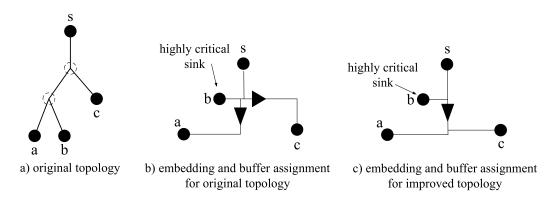

| 3.2 | Topology construction and buffer assignment [43]. Part a) shows the initial topology and part b) shows an embedding and buffer assignment for that topology that accounts for the time criticality of $b$ . In part c), a better topology is considered whose embedding and buffer assignment improves the delay for $b$ .                                                                                                                           | 32 |

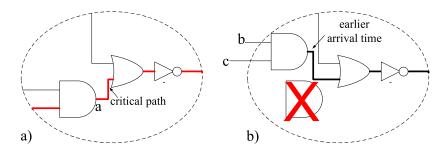

| 3.3 | Logic restructuring. The routing of signal $a$ with late arrival time shown<br>in part a) can be optimized by connecting $a$ to a substitute signal with<br>earlier arrival time as in part b). In this example, the output of the gate<br>AND(b,c) is a resynthesis of $a$                                                                                                                                                                          | 34 |

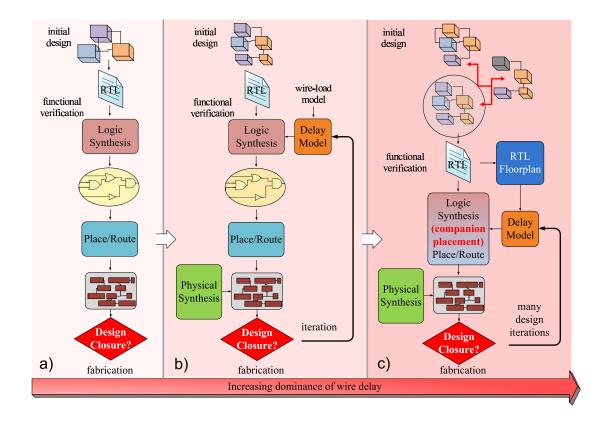

| 3.4 | Evolution of the digital design flow to address design closure challenges<br>due to the increasing dominance of wire delay. a) Design flow with<br>several discrete steps. b) Improved design flow using physical synthesis<br>and refined timing estimates to achieve timing closure more reliably. c)<br>Modern design flow where logic and physical optimization stages are<br>integrated to leverage better timing estimates earlier in the flow | 36 |

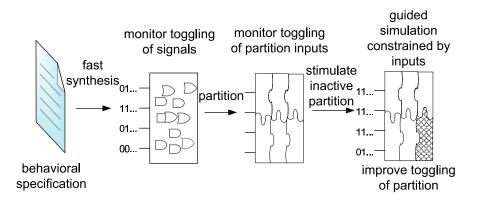

| 4.1 | Our Toggle framework automatically identifies the components of a cir-<br>cuit that are poorly stimulated by random simulation and generates input<br>vectors targeting them.                                                                                                                                                                                                                                                                        | 45 |

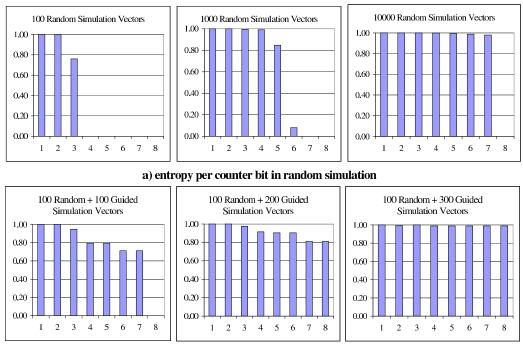

| 4.2 | The entropy of each bit for an 8-bit bidirectional counter after 100, 1000, and 10000 random simulation vectors are applied is shown in part a). Part b) shows the entropy achieved after 100, 200, and 300 guided vectors are applied after initially applying 100 random vectors.                                                                                                                                                                  | 48 |

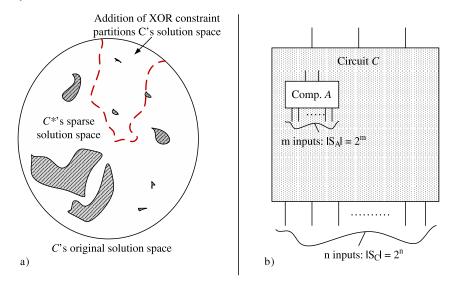

| 4.3 | a) XOR constraints are added to reduce the solution space of a SAT instance $C^*$ , which is sparser than the solution space of $C$ . b) Component $A$ is targeted for simulation, so that its $m$ inputs are evenly sensitized within circuit $C$ .                                                                                                                                                                                                 | 56 |

| 4.4 | Partition simulation algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                      | 58 |

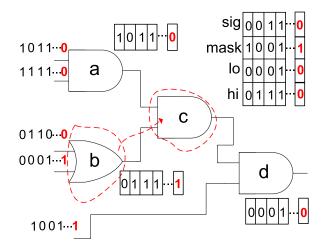

| 5.1 | Example of our ODC representation for a small circuit. For clarity, we only show ODC information for node $c$ (not shown is the downstream logic determining those don't-cares). For the other internal nodes, we report only their signature $S$ . When examining the first four simulation patterns, node $b$ is a candidate for merging with node $c$ up to ODCs. Further simulation indicates that an ODC-enabled merger is not possible. | 66  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2 | Efficiently generating ODC masks for each node                                                                                                                                                                                                                                                                                                                                                                                                | 68  |

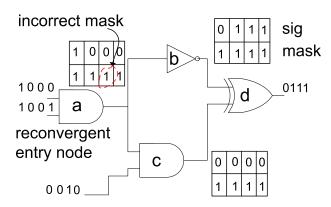

| 5.3 | Example of a false negative generated by our approximate ODC simulator due to reconvergence. $S^*$ and $S$ are shown for all internal nodes; only $S$ is shown for the primary inputs and outputs.                                                                                                                                                                                                                                            | 69  |

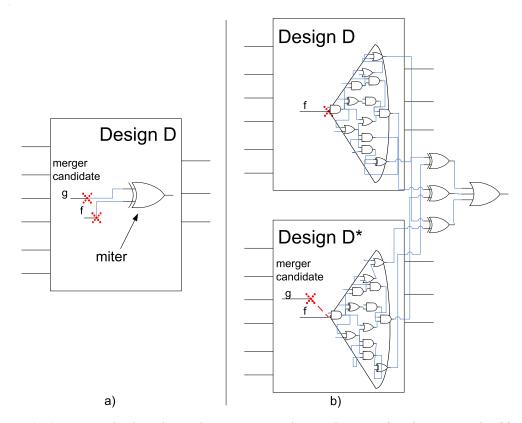

| 6.1 | An example that shows how to prove that node $g$ can implement node $f$ in the circuit. a) A miter is constructed between $f$ and $g$ to check for equivalence, but it does not account for ODCs because the logic in the fanout cone of $f$ is not considered. b) A dominator set can be formed in the fanout cone of $f$ and miters can be placed across the dominators to account for ODCs.                                                | 83  |

| 6.2 | Determining whether two nodes are equivalent up to ODCs                                                                                                                                                                                                                                                                                                                                                                                       | 84  |

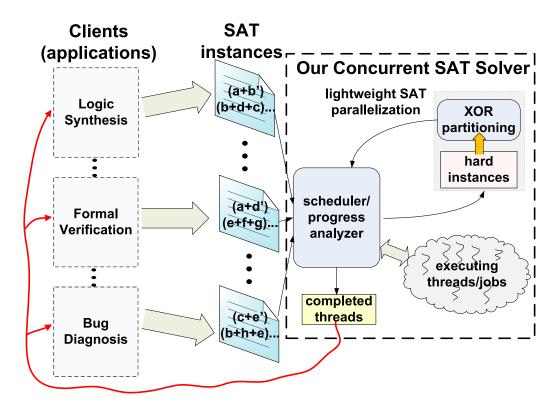

| 7.1 | High-level flow of our concurrent SAT methodology. We introduce a scheduler for completing a batch of SAT instances of varying complexity and a lightweight parallel strategy for handling the most complex instances.                                                                                                                                                                                                                        | 88  |

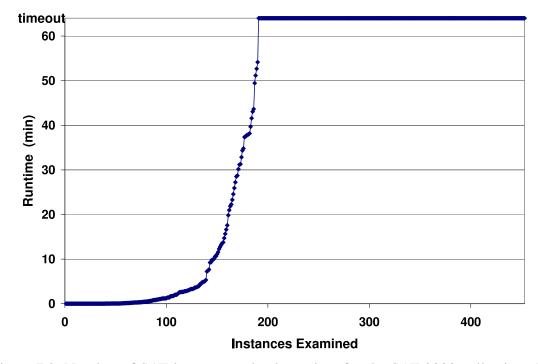

| 7.2 | Number of SAT instances solved vs. time for the SAT 2003 collection.<br>The timeout is 64 minutes.                                                                                                                                                                                                                                                                                                                                            | 94  |

| 7.3 | Percentage of total restarts for each minute of execution for a random sample of instances from the SAT 2003 collection.                                                                                                                                                                                                                                                                                                                      | 95  |

| 7.4 | Parallel SAT Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                        | 102 |

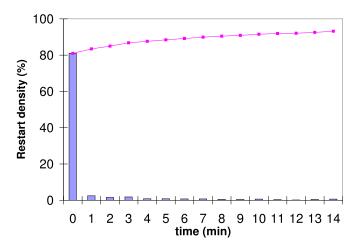

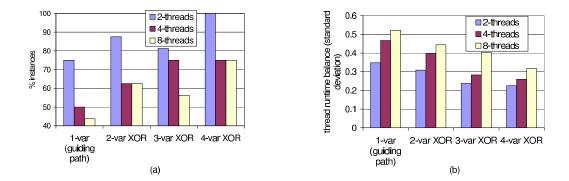

| 7.5 | The number of SAT instances solved (within the time allowed) by con-<br>sidering three different scheduling schemes for an 8-threaded machine.<br>Our priority scheme gives the best average latency, which is 20% better<br>than batch mode and 29% better than time-slice mode 1                                                                                                                                                            | 105 |

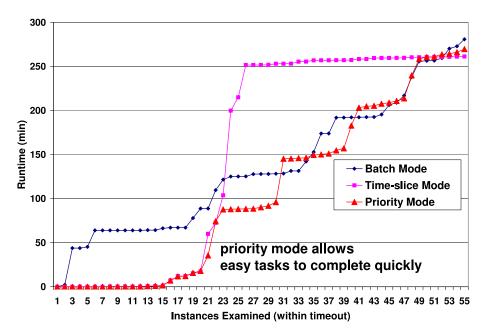

| 7.6 | a) The percentage of satisfiable instances where the first thread that com-<br>pletes finds a satisfying assignment. b) The standard deviation of run-<br>time between threads. Using XOR constraints as opposed to splitting<br>one variable can significantly improve load balance and more evenly dis-<br>tribute solutions among threads.                                                                                                                                           | 107 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.7 | The effectiveness of sharing learnt clauses by choosing the most active learnt clauses compared to the smallest learnt clauses                                                                                                                                                                                                                                                                                                                                                          | 109 |

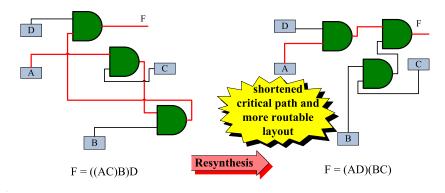

| 9.1 | The resynthesis of a non-monotone path can produce much shorter critical paths and improve routability.                                                                                                                                                                                                                                                                                                                                                                                 | 137 |

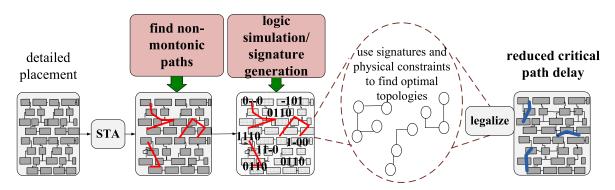

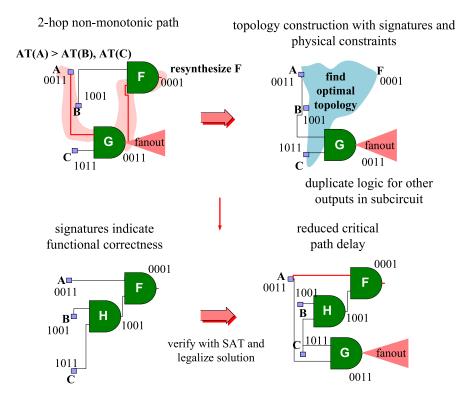

| 9.2 | Improving delay through logic restructuring. In our solution, we first identify the most promising regions for improvements, and then we restructure them to improve delay. Such netlist transformations include gate cloning, but are also substantially more general. They do not require for the transformed subcircuits to be equivalent to the original one. Instead, they use simulation and satisfiability to ensure that the entire circuit remains equivalent to the original. | 138 |

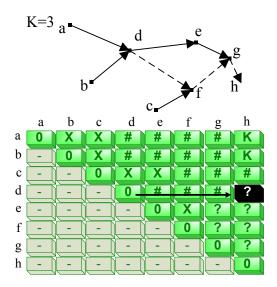

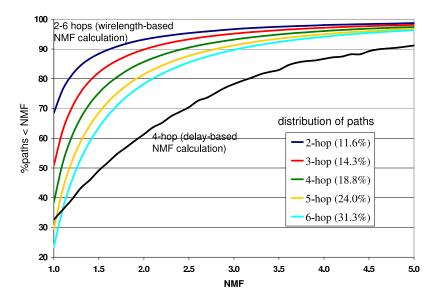

| 9.3 | Computing the non-monotone factor for <i>k</i> -hop paths                                                                                                                                                                                                                                                                                                                                                                                                                               | 140 |

| 9.4 | Calculating the non-monotone factor for path $\{d,h\}$ . The matrix shows sub-computations that are performed while executing the algorithm in Figure 9.3.                                                                                                                                                                                                                                                                                                                              | 140 |

| 9.5 | Our flow for restructuring non-monotone interconnect. We extract a sub-<br>circuit selected by our non-monotone metric and search for alternative<br>equivalent topologies using simulation. The new implementations are<br>then considered based on the improvement they bring and verified to be<br>equivalent with an incremental SAT solver.                                                                                                                                        | 142 |

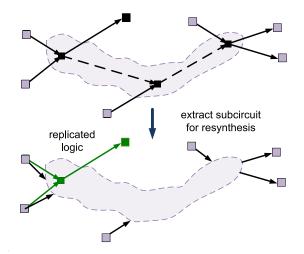

| 9.6 | Extracting a subcircuit for resynthesis from a non-monotone path                                                                                                                                                                                                                                                                                                                                                                                                                        | 143 |

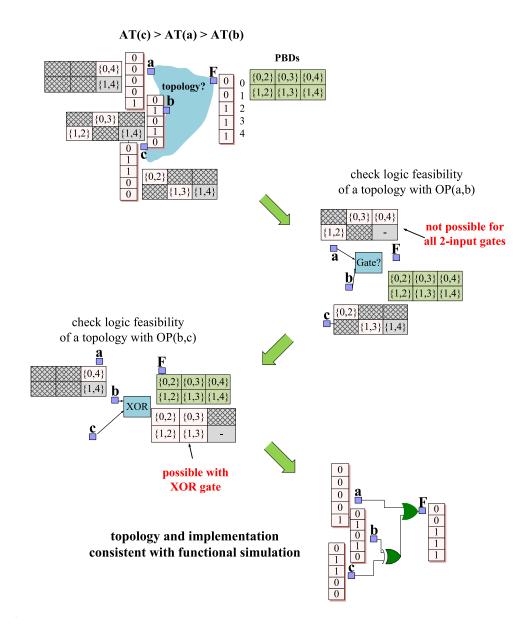

| 9.7 | Signatures and topology constraints guide logic restructuring to improve critical path delay. The figure shows the signatures for the inputs and output of the topology to be derived. Each table represents the PBDs of the output $F$ that are distinguished. The topology that connects $a$ and $b$ directly with a gate is infeasible because it does not preserve essential PBDs of $a$ and $b$ . A feasible topology uses $b$ and $c$ , followed by $a$                           | 144 |

| 9.8 | Restructuring non-monotone interconnect.                                                                                                                                                                                                                                                                                                                                                                                                                                                | 147 |

| 9.9  | The graph plots the percentage of paths whose NMF is below the corresponding value indicated on the x-axis. Notice that longer paths tend to be non-monotone and at least 1% of paths are $> 5$ times the ideal minimal length.                                                                             | 151 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

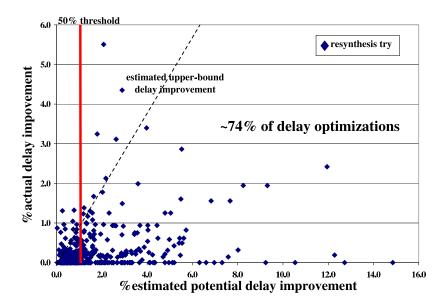

| 9.10 | The graph above illustrates that the largest <i>actual</i> delay improvements occur at portions of the critical path with the largest <i>estimated</i> gain using our metric. The data points are accumulated gains achieved by 400 different resynthesis attempts when optimizing the circuits in Table 1. | 156 |

## LIST OF TABLES

### **Table**

| 4.1 | Generating even stimuli through random XOR constraints for the 14 inputs of <i>alu</i> 4. We normalize the entropy seen along the inputs by $\log_2(\#simvectors)$ , so that 1.0 is the highest entropy possible | 60  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2 | Entropy analysis on partitioned circuits, the number of new input com-<br>binations found and the percentage of entropy increase after adding 32<br>guided input vectors versus 32 random ones                   | 61  |

| 4.3 | Comparing SAT-based re-simulation with random re-simulation over a partition for generating 32 vectors. The time-out is 10000 seconds                                                                            | 62  |

| 5.1 | Comparisons between related techniques to expose circuit don't-cares.<br>Our solution can efficiently derive both global SDCs and ODCs                                                                           | 65  |

| 5.2 | Efficiency of the approximate ODC simulator                                                                                                                                                                      | 74  |

| 5.3 | Runtime comparison between techniques from [95] and our global simulation.                                                                                                                                       | 74  |

| 7.1 | MiniSAT 2 results on the SAT 2003 benchmark suite                                                                                                                                                                | 103 |

| 7.2 | Running MiniSAT on a set of benchmarks of similar complexity using a varying number of threads.                                                                                                                  | 104 |

| 7.3 | Hard SAT instances solved using 8 threads of computation with a port-<br>folio of solvers.                                                                                                                       | 106 |

| 7.4 | Hard SAT instances solved using 4 threads of computation with a port-<br>folio of solvers.                                                                                                                       | 106 |

| 8.1 | Evaluation of our approximate ODC simulator in finding node merger candidates: we show the total number of candidates after generating 2048 random input patterns and report the percentage of false positives and negatives.                                               | 116 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.2 | Area reductions achieved by applying the ODC merging algorithm after ABC's synthesis optimization [62]. The time-out for the algorithm was set to 5000 seconds.                                                                                                             | 119 |

| 8.3 | Gate reductions and performance cost of the ODC-enhanced node-merging algorithm when applied to circuits synthesized with DesignCompiler [104] in high-effort mode. The merging algorithm runtime is bound to $\frac{1}{3}$ of the corresponding runtime in DesignCompiler. | 121 |

| 8.4 | Percentage of mergers that can be detected by considering only K levels of logic, for various K.                                                                                                                                                                            | 122 |

| 8.5 | Comparison with circuit unrolling. Percentage of total mergers exposed by the local ODC algorithm (K=5) for varying unrolling depths                                                                                                                                        | 122 |

| 8.6 | Statistics for the ODC merging algorithm on unsynthesized circuits. The table reports the SAT success rate in validating merger candidates and the number of SAT calls that could be avoided because of the use of dynamic simulation vectors.                              | 124 |

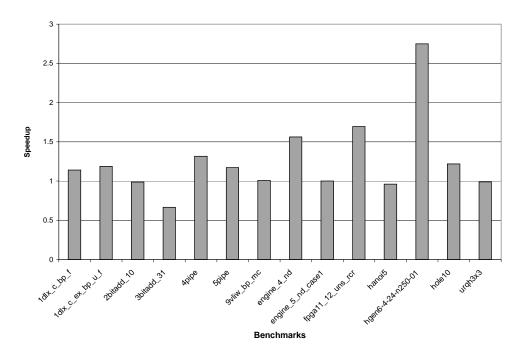

| 9.1 | Significant delay improvement is achieved using our path-based logic restructuring. Delay improvement is typically accompanied by only a small wirelength increase.                                                                                                         | 153 |

| 9.2 | Effectiveness of our approach compared to RAR                                                                                                                                                                                                                               | 155 |

### LIST OF ABBREVIATIONS

| 2-SAT | 2-SATisfiability (Satisfiability instance where each clause has at most two literals) |

|-------|---------------------------------------------------------------------------------------|

| ABC   | Software package for logic synthesis and verification                                 |

| 4 T   | from UC Berkeley                                                                      |

| AI    | Artificial Intelligence                                                               |

| AIG   | And-Inverter Graph                                                                    |

| AMD   | Advanced Micro Devices                                                                |

| AT    | Arrival Time                                                                          |

| ATPG  | Automatic Test Pattern Generation                                                     |

| BCP   | Boolean Constraint Propagation                                                        |

| BDD   | Binary Decision Diagram                                                               |

| C(b)  | Care set of <i>b</i>                                                                  |

| CAD   | Computer Aided Design                                                                 |

| CNF   | Conjunctive Normal Form                                                               |

| CODC  | Compatible Observability Don't Care                                                   |

| CPU   | Central Processing Unit                                                               |

| D2M   | Delay with 2 Moments                                                                  |

| DC    | Design Compiler (Synopsys synthesis tool) or                                          |

|       | Don't Care                                                                            |

| DC(b) | Don't Care set of <i>b</i>                                                            |

| DPLL  | Davis-Putnam-Logemann-Loveland (satisfiability                                        |

|       | algorithm)                                                                            |

| EDA   | Electronic Design Automation                                                          |

| FLUTE | A software package from Iowa State University                                         |

|       | implementing fast RSMT construction. It is based                                      |

|       | on lookup tables.                                                                     |

| FPGA  | Field-Programmable Gate Array                                                         |

| GB    | GigaByte                                                                              |

| GHz   | GigaHertz                                                                             |

| GSRC  | Gigascale Systems Research Center                                                     |

| GTECH | Generic TECHnology library (Synopsys)                                                 |

| HPWL  | Half-Perimeter WireLength                                                             |

| IC    | Integrated Circuit                                                                    |

| ITRS  | International Technology Roadmap for Semiconductors                                   |

|       | international reenhorogy reducing for senheonauctors                                  |

| IWLS      | International Workshop on Logic and Synthesis      |

|-----------|----------------------------------------------------|

| MOSFET    | Metal-Oxide-Semiconductor Field-Effect Transistor  |

| MUX       | MUltipleXer                                        |

| NMF       | Non-Monotonic Factor                               |

| ODC       | Observability Don't Care                           |

| OFFSET(b) | Set of input combinations where $b = 0$            |

| ONSET(b)  | Set of input combinations where $b = 1$            |

| OS        | Operating System                                   |

| PBD       | Pairs of Bits to be Distinguished                  |

| RAR       | Redundancy Addition and Removal                    |

| RSMT      | Rectilinear Steiner Minimal Tree                   |

| RTL       | Register Transfer Level                            |

| SAT       | SATisfiability (problem) or SATisfiable (solution) |

| SDC       | Satisfiability Don't Care                          |

| SMP       | Symmetric MultiProcessing                          |

| SPFDs     | Sets of Pairs of Functions to be Distinguished     |

| SSF       | Single-Stuck-at Fault                              |

| STA       | Static Timing Analysis                             |

| UIP       | Unique Implication Point                           |

| UNSAT     | UNSATisfiable                                      |

| U-SAT     | Unique-SATisfiable problem (only one solution)     |

| VSIDS     | Variable State Independent Decaying Sum            |

# Part I

# **Introduction and Background**

### **CHAPTER I**

## Introduction: Overcoming Challenges in Nanometer Design

### **1.1** Trends in the Electronics and EDA Industries

The performance capabilities of computer chips continue to increase rapidly. This, in turn, is driving the technology evolution in many different application domains, such as gaming and scientific computing. A major impetus for this growth is consumer demand, which seeks the smallest, fastest, and coolest devices. Consumer demand guides performance objectives and pressures computer companies to meet time-to-market expectations. Failure to meet these expectations can result in the loss of competitive advantage. For example, in 2006 Sony postponed the release date of the PlayStation 3 console by six months due to technical problems, exposing Sony's gaming market share to competing consoles by Microsoft and Nintendo.

Many applications depend on the predictability of improvements to integrated circuits.

Figure 1.1: Transistors manufactured on a single chip over several generations of Intel CPUs.

As shown in Figure 1.1, the number of transistors on a chip has been steadily increasing during the past 40 years. As a result, the Core 2 Duo CPU has almost one hundred times more transistors than the Pentium CPU 14 years ago. These scaling (and performance) trends have been made possible by advances in device manufacturing, which have resulted in the fabrication of smaller transistors. Transistor sizes are determined by the minimum size of a geometrical feature (usually a rectangle) that can be manufactured at a given technology node. Figure 1.2 illustrates the decreasing transistor size, where the physical length  $L_{GATE}$  of the transistor's gate is currently at 50nm and expected to shrink to 15nm as manufacturing techniques continue to improve. This scaling trend was observed by Gordon Moore in 1965, when he projected that the number of transistors that fit in an integrated circuit would double every two years [64], corresponding to an exponential growth. With more transistors, entire systems that were once implemented across a computer board, now fit on a single chip. More recently, this trend has made it possible to pack multiple processors in the same chip, so-called multi-core processors. Multi-core processors are now

mainstream in the mass-market desktop computing domain, unlocking the performance wall that single core microprocessors had reached, and allowing multiple applications to run in parallel on the same desktop system.

#### **1.2** Challenges in High-Performance Integrated Circuit Design

Ensuring continued performance improvements has become more challenging as transistors reach the nanometer scale. First, the complexity of integrated circuits has already exceeded the capability of designers to optimize<sup>1</sup> and verify their functionality. In design processes, verifying design correctness is a major component that affects time-to-market. Also, buggy designs released to the consumer market can significantly impact revenue as evidenced by Intel's floating-point division bug [100] and, more recently, by a bug in AMD's quad-core Phenom processor [99]. Second, the miniaturization of transistors to the atomic scale poses several challenges in terms of the variability in the manufacturing process, which leads to unpredictable performance. Third, the scaling of wire interconnect is not as pronounced as that of transistors. As transistors get faster and smaller, the width of wires decreases at a slower rate, and the per-unit resistance of wires may increase. Therefore, the advantages of having shorter wires are mitigated by the increase in time that it takes to propagate a signal. Consequently, an increasing percentage of chip area is necessary for wires, and the maximum clock frequency is primarily determined by wire lengths, rather than transistor switching time. Figure 1.3 illustrates the prevalence of interconnect on multiple metal layers on a chip. In this figure, two metal layers are shown with several wires and interlayer connectors called vias. This interconnect overshadows

<sup>&</sup>lt;sup>1</sup>In this dissertation, *optimize* is often used to mean performing operations that improve some performance characteristic.

the polysilicon gates, which are a component of MOSFETs (transistors).

Figure 1.2: Transistor scaling projected at future technology nodes.

Figure 1.3: Major components of multilayer interconnect: single-layer wire segments and inter-layer connectors (vias).

Traditionally, a computer chip design entails a series of steps from high-level conceptualization to final chip fabrication. It is this design flow (shown in Figure 1.4) that must be able to address technology scaling. Starting from the top left of Figure 1.4, a design team specifies the desired functionality of the chip. The design team identifies the chip's major components and designs each of them at a high level; this functionality may be expressed in a hardware description language, such as *SystemC*. Numerous optimizations are facilitated by the design team through the use of automated software tools. Eventually, the design description is translated into a register transfer level (RTL) description (top-right corner of Figure 1.4), which specifies a design in more detail. Through a process called *logic synthesis*, an RTL description is translated into a gate-level netlist as shown at the bottom right of the figure. In order to simplify transistor-level layout, multiple gates are mapped to pre-designed *standard cells*. This process is called *technology mapping*. At this point, an area estimate can be made based on the number of transistors required for the design. Also, one can estimate the fastest possible clock frequency for the chip based on transistor switching, since the number of cells that occur between the design's inputs and outputs is known. After a netlist is mapped to a set of cells, placement is performed. During *placement*, a physical location is given to each cell such that they do not overlap, and then wires connecting cells are routed. Finally, both wires and transistors are represented by polygons, and the resulting design description is sent for fabrication to obtain the final product, shown at the end of the flow in Figure 1.4.

Functional and physical verification are needed throughout the design flow. After performing RTL and netlist-level optimization, the design's outputs are checked against the expected behavior of the design. Physical verification ensures that *design rules* (such as maintaining minimum spacing between wires), as well as electrical and thermal constraints, are satisfied. Furthermore, at the end of the design flow before fabrication, the performance characteristics of the design are checked against desired goals and objectives. This process of meeting performance objectives is known as achieving design clo-

Figure 1.4: Typical integrated circuit design flow. The design flow starts from an initial design specification. Several optimization steps are performed, and then a final chip is manufactured.

sure. The process of ensuring that the circuit timing (delay) constraints are met is known as achieving *timing closure*.

Physical information about the design, such as cell locations and wire routes, is known only at the end of the flow. As previously noted, delay associated with wires is becoming more prominent, hence accurate timing estimates are known only when wire lengths are determined after the routing phase. However, most functional design optimizations are traditionally performed early at the RTL, as well as during logic synthesis and technology mapping. After several of these optimization steps, placement and routing might produce a modified design that no longer achieves timing closure. Hence, the inability to gather accurate timing and performance estimations early in the design flow leads to less flexibility in performing design optimizations. For instance, optimizing for a specific performance metric after placement and routing, such as timing, can negatively affect the quality of other performance metrics. To avoid this tension between various design goals, late design flow optimizations are normally limited. Hence more heavyweight optimizations may necessitate the re-iteration of earlier steps in the design flow. In some cases, the number of design iterations required to achieve timing closure is prohibitive. Multiple iterations increase the turn-around-time, development costs, and time-to-market, while also resulting in a design that might fail to meet original expectations.

#### **1.3 Bridging the Gap between Logic and Physical Optimizations**

This dissertation develops powerful and efficient logic transformations that are applied late in the design flow to achieve timing closure. The transformations overcome the limitations of current methodology by 1) extracting and exploiting more circuit flexibility to improve performance late in the design flow and 2) minimizing the negative impact to other performance metrics. The goal is to eliminate costly design iterations and enable efficient use of multi-core processors, to overcome increased design complexity and scaling challenges.

To enable these transformations, our work leverages the principle of *abstraction* by temporarily discarding all aspects of circuit behavior not observed during a fast bit-parallel simulation. Under this abstraction, we can handle complex designs, pinpoint potential logic transformations that may lead to improvements in the design, and assess the quality of a wide range of transformations. In the following section, we discuss our abstraction technique and its components in more detail.

#### **1.4 Using Simulation-based Abstractions for Circuit Optimizations**

Key to our approach is the use of logic simulation to approximate the behavior of each node in a circuit through information known as a *bit signature* [50]. The functionality of a node in a circuit is defined by its truth table that specifies the node's output for all input combinations. A signature is a partial truth table selected by a (usually small) subset of the possible input combinations. Such a partial truth table can be viewed as an abstracted representation that can be exponentially smaller than a complete truth table, yet can accurately guide optimizations as we show throughout this dissertation. Because of the efficiency of logic simulation, approximating circuit behavior scales linearly with the number of nodes in the circuit, and consequently it can tackle large circuits. While such signatures have already been used in the literature, these pre-existing techniques suffer from a number of limitations.

**Summary of related work.** The effectiveness of logic simulation has been demonstrated in terms of its ability to distinguish different nodes in a circuit [50, 59]. Consequently, signatures can be used in both logic optimization and verification. With respect to verification, the correctness of a design can be ascertained up to the abstraction by comparing its output signature to the corresponding output of a functionally correct design, also known as a *golden model*. Design optimizations are also enabled by signatures because equivalent nodes in a circuit can be merged to simplify the design [59]. Furthermore, the signature representation is amenable to simple transformations [18], that can generate new signatures and that, in turn, can be mapped to logic optimizations on the actual design.

**Key aspects and limitations of signature-based abstractions.** When signatures are used, optimization and verification are correct only with respect to the abstraction. A for-

mal proof mechanism is often required to verify the correctness of the abstraction. Formal proof engines, such as SAT solvers, invariably have exponential worst-case runtimes. This lack of scalability is particularly problematic as design complexity grows. Since formal proof mechanisms are typically based on hard-to-parallelize algorithms, it is difficult to efficiently utilize the resources offered by recent multi-core CPUs.

Generating high-quality signatures is paramount so as to avoid incorrect characterizations and to minimize the number of invocations of expensive proof mechanisms. The quality of a signature rests in its ability to capture both typical-case behaviors and important corner-behaviors, while being occasionally refined through formal techniques and additional simulation patterns. In [59], signatures are refined to improve their distinguishing capabilities in finding equivalent nodes in a design. Despite the efficiency of generating signatures, ensuring their high *quality* in very large designs with complex hierarchical components is a major challenge. In this scenario, if a signature abstraction is desired for a component far from the primary inputs of a design, the limited *controllability* of this component undermines the quality of the signature generated and its ability to expose interesting behavior in that component. Furthermore, previous works do not consider a node's *downstream* logic information when characterizing its behavior with a signature, and therefore fail to exploit logic flexibilities present in large designs.

Finally, a general methodology *for performing design optimizations with signatures* has not yet been developed. As we show in this dissertation, signatures simplify the search for logic transformations and thus facilitate powerful gate-level optimizations that involve both logic and physical design aspects. Such optimizations are known as physical synthesis. However, conventional strategies for synthesis are inadequate in exploiting the runtime

savings and optimization potential of signature-based synthesis. This dissertation presents the first generalized solution achieving this goal.

### 1.5 Components of Our Simulation-based Framework

To enable complex transformations that can be applied late in the design flow to achieve timing closure, we introduce a series of improvements to signature-based abstractions that overcome previous limitations. The new elements of our simulation-based framework, developed throughout the dissertation, not only result in better optimizations, but improve the quality of verification efforts. We now outline our major contributions:

- A high-coverage verification engine for stimulating a component deep within a hierarchical design while satisfying constraints. Our strategy relies on a simulation engine for high performance, while improving the fidelity of signatures and verification coverage.

- An efficient linear-time *don't-care* analysis to extract potential flexibility in synthesizing each node of a circuit and to enhance the corresponding signatures.

- A technique to improve the efficiency of the formal proof mechanism in verifying the equivalence between a design and its abstraction enhanced by don't-cares.

- A strategy to improve the efficiency of verifying abstractions by exploiting parallel computing resources such as the increasingly prevalent multi-core systems. Harnessing these parallel resources is one mechanism to partially counteract the increasing costs of verification and to enable deployment of our signature-based optimizations on more complex designs.

- A goal-driven synthesis strategy that quickly evaluates different logic implementations leveraging signatures.

- A constraint-guided synthesis algorithm using signatures to improve physical performance metrics, such as timing.

### **1.6** Organization of the Dissertation

In this dissertation, we introduce several algorithmic components that enhance our signature-based abstraction. We then leverage these components in logic and physical synthesis to enable powerful optimizations, where traditional techniques perform poorly. Throughout the chapters of this dissertation, we gradually extend the scope and power of signature-based optimizations. In Part II, we propose techniques that enhance signatures by generating better simulation vectors that activate parts of the circuit in a design and by encoding information on logic flexibility in the signatures. In Part III, we develop verification strategies that mitigate the runtime costs of verifying the correctness of the abstraction. In Part IV, we utilize our enhanced signatures and verification strategies to enable design optimizations by manipulating these signatures. The rest of the dissertation is structured as follows:

- For the remainder of Part I, we provide background material necessary to navigate through this dissertation.

- Chapter II covers background in logic synthesis, verification, and logic simulation. We outline recently-discovered synergies between these tasks and explain how this dissertation builds upon these synergies.

- Chapter III describes the evolution of the design flow to address timing closure and to survey previous work in late design flow optimization.

- In Part II, we introduce strategies to improve the quality and strength of signatures.

- Chapter IV introduces the notion of entropy for identifying parts of a design that experience low simulation coverage. We then develop a strategy for improving simulation of these regions using a SAT solver. This approach is useful for stimulating internal components in complex hierarchies. In particular, it helps in exposing bugs in corner-case behaviors.

- Chapter V introduces a technique for the efficient extraction of global circuit don't-cares based on a linear-time analysis and encodes them in signatures.

- Part III introduces strategies to counteract the complexity of verifying signaturebased abstractions in increasingly large designs.

- Chapter VI describes an incremental approach to verify a given abstraction up to the derived don't-cares and to refine it by generating additional signatures.

- Chapter VII introduces techniques to address the growing complexity of formal verification by exploiting the increasing availability of multi-core systems which can execute several threads simultaneously. We develop a parallel-SAT solving methodology that consists of a priority-based scheduler for handling multiple problem instances of varying complexity in parallel and a lightweight strategy for handling single instances of high complexity.

- Part IV introduces techniques for performing logic manipulations using signatures.

- Chapter VIII describes how signatures can be exploited to enable powerful synthesis transformations. In particular, we show how node merging up to don't-cares can greatly simplify a circuit. Then, we introduce a new general approach for performing logic synthesis using signatures.

- Chapter IX proposes a path-based resynthesis algorithm that finds and shortens critical paths with wire bypasses. We apply our path-based resynthesis after placement, when better timing estimates are available, and we report significant improvements, indicating that current design flows still leave many optimization opportunities unexplored.

- The dissertation is concluded in Chapter X with a summary of contributions and an outline of future research directions.

### **CHAPTER II**

## Synergies between Synthesis, Verification, and Functional Simulation

In the traditional design flow for integrated circuits, logic synthesis and verification play a critical role in ensuring that integrated circuit parts released to the market are functionally correct and achieve the specified performance objectives. Logic synthesis generates circuit netlists and transforms them to improve area and delay characteristics. These transformations are carried forward by software used by circuit designers. To ensure the correctness of these transformations, along with custom-made optimizations, verification is typically performed over multiple steps in the design flow, where the actual behavior of the circuit is verified against the desired behavior. Traditionally, synthesis and verification are considered separate and independent tasks; however, recent research [59, 63, 95] has exposed a number of common traits and synergies between synthesis and verification. Functional verification often involves algorithms whose worst-case runtime complexity grows exponentially with design size. However, the design size can be reduced through synthesis optimizations, typically reducing the verification effort. Logic simulation has also been employed to improve verification, and more recently, to enable netlist simplifications [95].

A major contribution of this dissertation is its in-depth exploration of synergies be-

tween synthesis and verification, as well as the gains that can be derived by integrating the two tasks through simulation techniques. Our goal is to improve the quality of results and the scalability of both practices, which are continually challenged by increasing design complexity. In particular, we introduce speculative transformations that require verification, a major departure from traditional correct-by-synthesis techniques, typically employed today. In the remainder of this chapter, we discuss previous work in verification, synthesis and logic simulation, focusing on strategies to improve their scalability.

#### 2.1 Scalable Verification

Verifying the functional correctness of a design is a critical aspect of the design flow. Typically, comprehensive verification methodologies [96, 97] are employed and require a team of specialized verification engineers to construct test cases that exercise the functionality of the circuit. The output of this circuit is usually compared against an ideal *golden model*. To reduce the demands on the verification engineer in exposing interesting design behavior through test cases, input stimuli can be automatically refined or modified, leading to improvement in the verification coverage. For example, at the instruction level, Markov models can be used [83] to produce instruction sequences that effectively stimulate certain parts of the design. However, explicit monitors are necessary to guide this refinement, thus still requiring detailed understanding of the design. At the gate-level, simulation can also be refined [59] to help distinguish nodes, but this is primarily useful for equivalence checking. The goal of all these procedures is to generate test cases that can expose corner-case behavior in the circuit. In Chapter IV, we discuss how simulation coverage is improved automatically, without requiring any detailed understanding of the design.

Because generating exhaustive test cases is infeasible and releasing a buggy design

is undesirable, formal verification techniques can be used to achieve higher verification coverage. However, the limited scalability of formal techniques is a major bottleneck in handling increasingly complex designs. Therefore, a combination of intelligently chosen test suites and formal techniques on small components is often adopted to maximize verification coverage.

One prominent formal proof mechanism particularly relevant to this work is equivalence checking. In equivalence checking, the output response of a design is compared against a golden model for all legal input combinations. If the response is always the same, the designs are said to be equivalent. Often, binary decision diagrams (BDDs) can be used to check the equivalence between two combinational circuits. A BDD [14] is a data structure that can often efficiently represent a circuit in a canonical way, so that checking equivalence means building this canonical form for both designs. However, the number of nodes in a BDD can be exponential with respect to the number of inputs, thus limiting the scalability of the approach. Satisfiability-based equivalence checking techniques have been developed [13] as an alternative to BDDs. Despite having exponential worst-case runtime, SAT-based techniques typically have lower memory requirements and successfully extend to larger designs. Below we provide the background on satisfiability necessary to navigate this dissertation. Then we examine previous attempts to scale the performance of SAT solvers by exploiting multiple processing units concurrently.

#### 2.1.1 Satisfiability

The SAT problem entails choosing an assignment V for a set of variables that satisfies a Boolean equation or discovering that no such assignment exists [76]. The Boolean equation is expressed in conjunctive normal form (CNF), F = (a + b' + c)(d' + e).... – a conjunction of *clauses*, where a clause is a disjunction of literals. A literal is a Boolean variable or its complement. For instance, (a+b'+c) and (d'+e) are clauses, and a, b', c, d', e are literals.

#### A Framework for Solving SAT

A common approach to solving SAT is based on the branch-and-backtrack DPLL algorithm [24]. Several innovations, such as non-chronological backtracking, conflict-driven learning, and decision heuristics greatly improve upon this approach [65, 80, 88]. The essential procedural components of a SAT solver are outlined in the pseudo-code of Figure 2.1.

| search {                                     |

|----------------------------------------------|

| while(true) {                                |

| propagate();                                 |

| if(conflict) {                               |

| analyze_conflict();                          |

| <b>if</b> (top_level_conflict) return UNSAT; |

| backtrack();                                 |

| }                                            |

| else if(satisfied) return SAT;               |

| else decide();                               |

| }                                            |

| }                                            |

Figure 2.1: Pseudo-code of the search procedure used in DPLL-SAT. The procedure terminates when it either finds a satisfying assignment or proves that no such solution exists.

The search() function explores the decision tree until a satisfying assignment is found or the entire solution space is traversed without finding any such assignment. The decide() function selects the next variable for which a value is chosen. Many methods exist for selecting this "decision" variable, such as the VSIDS (Variable State Independent Decaying Sum) algorithm developed in Chaff [65]. VSIDS involves associating an activity counter with each literal. Whenever a new learnt clause is generated (see below) from conflict analysis, the counter of each literal in that clause is incremented while all other variables undergo a small decrease. The propagate() function performs Boolean Constant Propagation (BCP), *i.e.*, it identifies the clauses that are still unsatisfied and for which only one literal is still unassigned, and then assigns the literal to the only value that can satisfy the clause. If the decision assignment implies a contradiction or conflict, the analyze\_conflict() function produces a *learnt* clause, which records the cause of the conflict to prevent the same conflicting sets of assignments. The backtrack() function undoes the earlier assignments that contributed to the conflict. Periodically, the search() function is restarted: all current assignments are undone, and the search process starts anew using a random factor in restarting the decision process so that different parts of the search space are explored. Extensive empirical data shows the effectiveness of restarts in boosting the performance of SAT solvers by minimizing the exploration in computation-intensive search paths [9, 65].

#### Learning

In this part, we consider two types of learning performed to reduce SAT search space: preprocessing and conflict-driven learning.

**Preprocessing.** The goal of preprocessing a SAT instance is to simplify the instance by adding implied constraints that reduce propagation costs: by eliminating variables, by adding symmetry breaking clauses, or by removing clauses that are subsumed by others. Preprocessing has led to improved runtime in solving several instances, although the computational effort sometimes outweighs the benefit. A recent preprocessor, SatELite [28], achieves significant simplifications through the efficient implementations of variable elimination and subsumption.

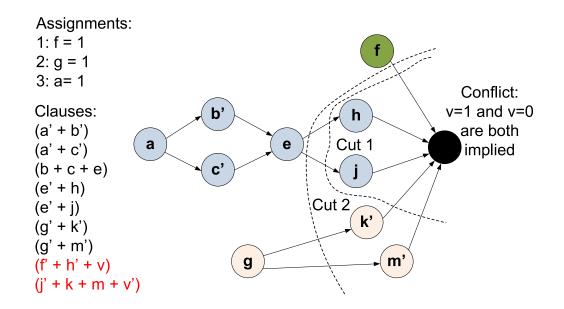

**Conflict-driven learning.** Dynamic learning is important to prevent repeated exploration in similar parts of the search space. When a set of assignments results in a conflict, the conflict analysis procedure in SAT determines the cause by analyzing a *conflict graph*. In Figure 2.2, we show an example of a SAT instance and a set of assignments that result in a conflicting assignment for variable *v*. Each decision (f = 1, g = 1, and a = 1) is depicted by a different leaf node, and *implications* of these decisions, are shown as internal nodes in the graph. An implication occurs when a set of variable decisions forces an unassigned variable to be assigned 0 or 1. A *decision level* is associated with each node (nodes at the same level are denoted by the same color in Figure 2.2), which is the set of variable assignments implied by a decision. For instance, the second decision level consists of the second decision (g = 1), and the implications k = 0 and m = 0.

A learnt clause can be derived in a conflict graph from a cut that crosses every path from the leaf decision values to the conflict exactly once. The nodes to the left of the cut are on the *reason side* and those on the right are on the *conflict side*. Cut 1 in the figure shows the *1-UIP* (first unique implication point) cut, *i.e.*, the cut closest to the conflict side. In this cut, the reason side contains one node of the last decision level (node *a*) that dominates all other nodes at the same decision level and on the same (reason) side. The assignment e = 1, f = 1, k = 0, m = 1 is determined to be in conflict and hence (e' + f' + k + m) can be added to the original CNF to prevent this assignment in the future. Cut 2 indicates the 2-UIP cut where the reason side contains one node in the previous decision level (level 2) that dominates every other node in that decision level. Here, the 2-UIP learnt clause (e' + f' + g') can be added.

Figure 2.2: An example conflict graph that is the result of the last two clauses in the list conflicting with the current assignment. We show two potential learnt clauses that can be derived from the illustrated cuts. The dotted line closest to the conflict represents the 1-UIP cut, and the other is the 2-UIP cut.

A learning strategy commonly employed adds only the 1-UIP learnt clause for every conflict. Despite the possibility of using smaller learnt clauses that technically prune larger parts of the search space, it has been empirically shown in [90] that 1-UIP learning is most effective. In [27], 1-UIP was shown to be more effective at pruning the search space because the corresponding backtracking more often satisfied learnt clauses generated by other UIP cuts.

#### 2.1.2 Previous Parallel SAT Approaches

To boost the performance of SAT solvers on increasingly prevalent parallel architectures, parallel SAT solving strategies have explored coarse-grain and fine-grain parallelization. Fine-grain parallelization strategies target Boolean Constraint Propagation (BCP) the runtime bottleneck for most SAT solvers. In BCP, each variable assignment is checked against all relevant clauses, and any implications are propagated. BCP can be parallelized by dividing the clause database among *n* different solvers so that BCP computation time of each solver is approximately  $\frac{1}{n}$  the original. Coarse-grain parallelization strategies typically involve assigning a SAT solver to different parts of the search space.

**Fine-grain parallelization.** The performance of fine-grain parallelization depends on the partitioning of clauses among the solvers, where an ideal partition ensures an even distribution of BCP costs while minimizing the implications that need to be communicated between each solver. This strategy also requires low-latency inter-solver communication to minimize contention for system locks on general microprocessors, which can exacerbate runtime performance. Therefore, fine-grain parallelization has been examined on specialized architectures [91] that can minimize communication bottlenecks. In [2, 92], significant parallelization was achieved by mapping a SAT instance to an FPGA and allowing BCP to evaluate several clauses simultaneously. However, the flexibility and scalability of this approach is limited, since each instance needs to be compiled to the specific FPGA architecture (a non-trivial task), and conflict-driven learning is difficult to implement effectively in hardware because it requires dynamic data structures.

**Coarse-grain parallelization.** The runtime of an individual problem can also be improved with parallel computation by using a solver portfolio [38], where multiple SAT heuristics are executed in parallel and the fastest heuristic determines the runtime for the problem. A solver portfolio also offers a way of countering the variability that backtrack-style SAT solvers experience on many practical SAT instances [39]. Because one heuristic may perform better than another on certain types of problems, one can reduce the risk of choosing the wrong heuristic by running both. Although parallelization here consists of

running multiple versions of the same problem simultaneously, if the runtime difference between these heuristics is significant, a solver portfolio can yield runtime improvements.

However, using a portfolio solver does not guarantee high resource utilization as each heuristic may perform similarly on any given instance or one heuristic may dominate the others. The primary limitation of solver portfolios is that there is no good mechanism to coordinate the efforts of these heuristics and the randomness inherent to them. Other approaches consider analyzing different parts of the search space in parallel [22, 55, 66, 89]. If the parts of the search space are disjoint, the solution to the problem can be determined through the processing of these parts in isolation. However, in practice, the similarities that often exist between different parts of the search space mean that redundant analysis is performed across the different parts. To counter this, the authors in [55] develop an approach to explore disjoint parts of the search space by relying on the shared memory of multi-core systems to transfer learned information between them. The approach considers dividing the problem instance using different variable assignments called *guiding paths*, as originally described in [89]. One major limitation of this type of search space partitioning is that poor partitions can produce complex sub-problems with widely varying structure and complexity.