SSAT.W <Rd>, #<immed>, <Rn>, {,<shift>}

SSAT.W R1, #16, R0

| Input (R0) | Output (R1) | Q Bit     |

|------------|-------------|-----------|

| 0x00020000 | 0x00007FFF  | Set       |

| 0x00008000 | 0x00007FFF  | Set       |

| 0x00007FFF | 0x00007FFF  | Unchanged |

| 0x00000000 | 0x00000000  | Unchanged |

| 0xFFFF8000 | 0xFFFF8000  | Unchanged |

| 0xFFFF8001 | 0xFFFF8000  | Set       |

| 0xFFFE0000 | 0xFFFF8000  | Set       |

#### From: The Definitive Guide to the ARM Cortex-M3

### Generalization of Interrupts

7

- Merriam-Webster: "to break the uniformity or continuity of"

- Informs a program of some external events

- Breaks execution flow

- Where do interrupts come from?

- How do we save state for later continuation?

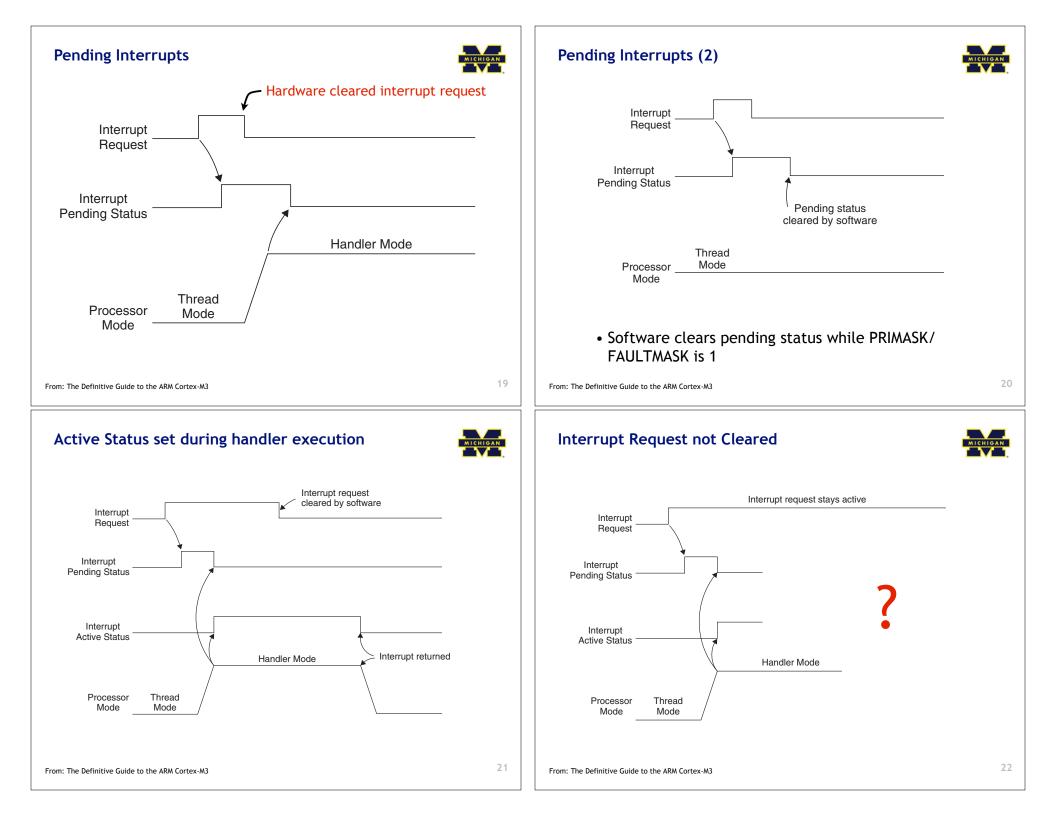

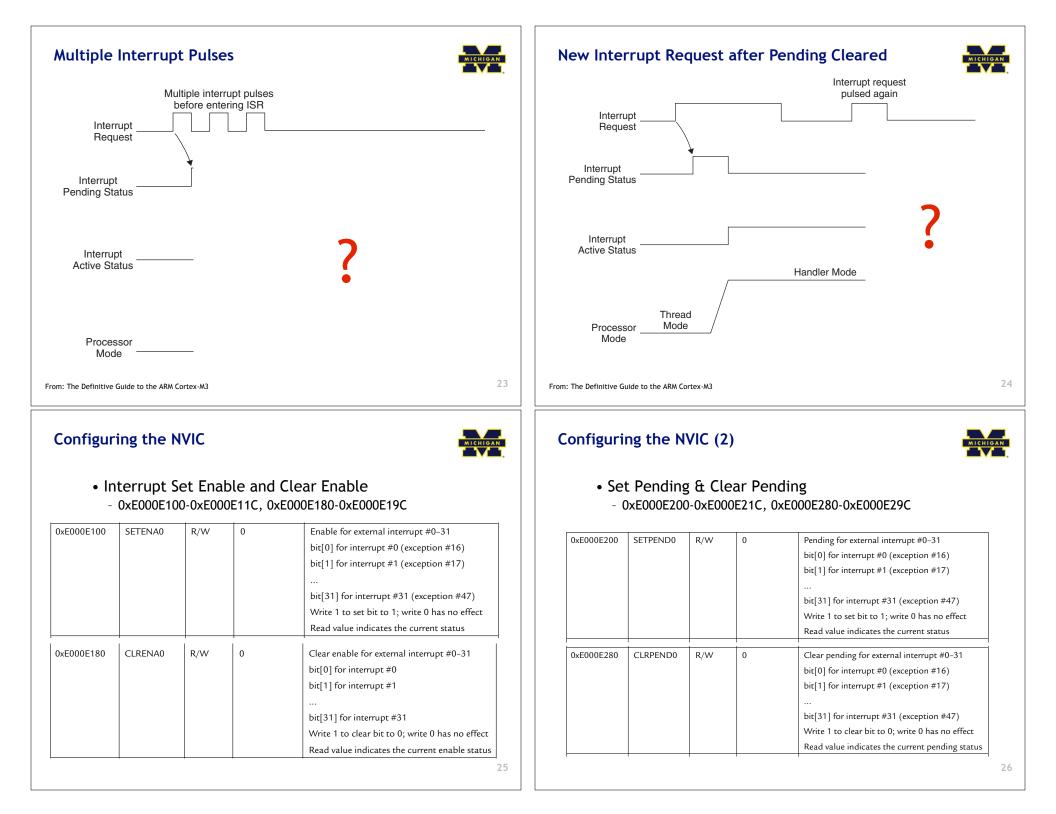

- How can we ignore interrupts?

- How can we prioritize interrupts?

- How can we share interrupts?

## Interrupts

8

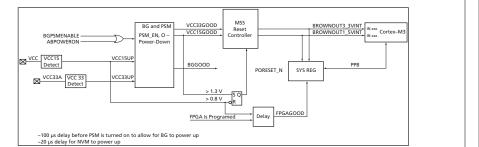

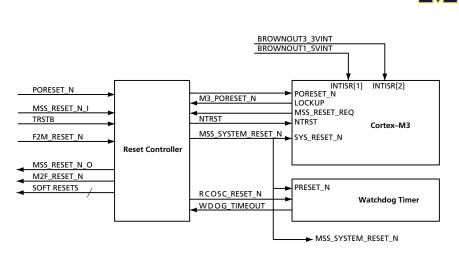

### How does an embedded system boot?

# The Reset Interrupt

### 1. No power

- 2. System is held in RESET as long as VCC15 < 0.8V

- a. In reset: registers forced to default

- b. RC-Osc begins to oscillate

- c. MSS\_CCC drives RC-Osc/4 into FSCK

- d. PORESET\_N is held low

- 3. Once VCC15GOOD, PORESET\_N goes high

- a. MSS reads from eNVM address 0x0 and 0x4

### Interrupt Handling

11

Source  $\rightarrow$  Controlle  $\rightarrow$  MPU

- On the Cortex-M3

- Source: Software, Peripheral

- Controller: Nested Vectored Interrupt Controller (NVIC)

- MPU: Cortex-M3 Core

• The Reset Interrupt is Non-Maskable!

### Sources of Interrupts

The Reset Interrupt (2)

### **Types of Interrupts**

- Physical interrupts

- Level-triggered

- Edge-triggered (positive, negative)

- Hybrid

- Look for edges, but signal must stay for a while

- Often used for non-maskable interrupts to avoid glitches

- Non-maskable interrupts

- Interrupt priorities

- Software interrupts

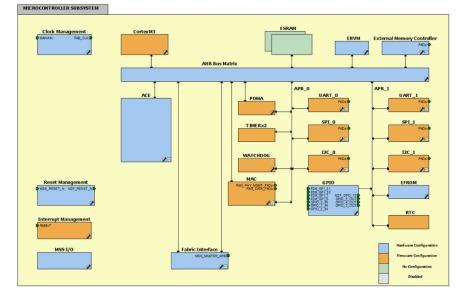

### The Nested Vectored Interrupt Controller (NVIC) on the Cortex-M3

- Control registers are memory mapped

- Contains control logic for interrupt processing

- Also contains MPU, SYSTICK Timer, and Debug

- 15 internal interrupts (defined by ARM)

- Supports up to 240 external interrupts (vendor specific)

- Accessed at 0xE000E000 on any Cortex-M3!

- Register definitions can be found at:

- ARM Cortex-M3 Technical Reference Manual v2.1, Chapter 6

TISR[67]

INTISR[71]

INTISR[72]

INTISR[73]

NTISR[74]

ITISR[75]

NTISR[78]

INTISR[79]

NTISR(80)

NTISR(81)

NTISR[82]

ISR[83]

risri87

risriari

risr[93]

risp[94]

- The Definitive Guide to the ARM Cortex-M3

- 15

17

### System Exceptions **NVIC Interrupts 1-15**

| Exception | Exception Type  | Priority     | Description                                                                                                                                                                                                    |

|-----------|-----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number    |                 |              |                                                                                                                                                                                                                |

| 1         | Reset           | -3 (Highest) | Reset                                                                                                                                                                                                          |

| 2         | NMI             | -2           | Nonmaskable interrupt (external NMI input)                                                                                                                                                                     |

| 3         | Hard Fault      | -1           | All fault conditions, if the corresponding fault handler is not enabled                                                                                                                                        |

| 4         | MemManage Fault | Programmable | Memory management fault; MPU violation or access to illegal locations                                                                                                                                          |

| 5         | Bus Fault       | Programmable | Bus error; occurs when AHB interface receives an<br>error response from a bus slave (also called <i>prefetch</i><br><i>abort</i> if it is an instruction fetch or <i>data abort</i> if it is a<br>data access) |

| 6         | Usage Fault     | Programmable | Exceptions due to program error or trying to access<br>coprocessor (the Cortex-M3 does not support a<br>coprocessor)                                                                                           |

| 7-10      | Reserved        | NA           | -                                                                                                                                                                                                              |

| 11        | SVCall          | Programmable | System Service call                                                                                                                                                                                            |

| 12        | Debug Monitor   | Programmable | Debug monitor (breakpoints, watchpoints, or external debug requests)                                                                                                                                           |

| 13        | Reserved        | NA           | -                                                                                                                                                                                                              |

| 14        | PendSV          | Programmable | Pendable request for system device                                                                                                                                                                             |

| 15        | SYSTICK         | Programmable | System Tick Timer                                                                                                                                                                                              |

### **Actel SmartFusion Interrupts**

| Cortex-M3 NVIC Input | IRQ Label          | IRQ Source       |

|----------------------|--------------------|------------------|

| NMI                  | WDOGTIMEOUT_IRQ    | WATCHDOG         |

| INTISR[0]            | WDOGWAKEUP_IRQ     | WATCHDOG         |

| INTISR[1]            | BROWNOUT1_5V_IRQ   | VR/PSM           |

| INTISR[2]            | BROWNOUT3_3V_IRQ   | VR/PSM           |

| INTISR[3]            | RTCMATCHEVENT_IRQ  | RTC              |

| INTISR[4]            | PU_N_IRQ           | RTC              |

| INTISR[5]            | EMAC_IRQ           | Ethernet MAC     |

| INTISR[6]            | M3_IAP_IRQ         | IAP              |

| INTISR[7]            | ENVM_0_IRQ         | ENVM Controller  |

| INTISR[8]            | ENVM_1_IRQ         | ENVM Controller  |

| INTISR[9]            | DMA_IRQ            | Peripheral DMA   |

| INTISR[10]           | UART_0_IRQ         | UART_0           |

| INTISR[11]           | UART_1_IRQ         | UART_1           |

| INTISR[12]           | SPI_0_IRQ          | SPI_0            |

| INTISR[13]           | SPI_1_IRQ          | SPI_1            |

| INTISR[14]           | 12C_0_IRQ          | 12C_0            |

| INTISR[15]           | I2C_0_SMBALERT_IRQ | 12C_0            |

| INTISR[16]           | I2C_0_SMBSUS_IRQ   | 12C_0            |

| INTISR[17]           | I2C_1_IRQ          | 12C_1            |

| INTISR[18]           | I2C_1_SMBALERT_IRQ | 12C_1            |

| INTISR[19]           | I2C_1_SMBSUS_IRQ   | 12C_1            |

| INTISR[20]           | TIMER_1_IRQ        | TIMER            |

| INTISR[21]           | TIMER_2_IRQ        | TIMER            |

| INTISR[22]           | PLLLOCK_IRQ        | MSS_CCC          |

| INTISR[23]           | PLLLOCKLOST_IRQ    | MSS_CCC          |

| INTISR[24]           | ABM_ERROR_IRQ      | AHB BUS MATRIX   |

| INTISR[25]           | Reserved           | Reserved         |

| INTISR[26]           | Reserved           | Reserved         |

| INTISR[27]           | Reserved           | Reserved         |

| INTISR[28]           | Reserved           | Reserved         |

| INTISR[29]           | Reserved           | Reserved         |

| INTISR[30]           | Reserved           | Reserved         |

| INTISR[31]           | FAB_IRQ            | FABRIC INTERFACE |

| INTISR[32]           | GPIO_0_IRQ         | GPIO             |

| INTISR[33]           | GPIO_1_IRQ         | GPIO             |

| INTISR[34]           | GPIO_2_IRQ         | GPIO             |

|     | MICHIGA                |

|-----|------------------------|

|     | $\mathbf{I}\mathbf{M}$ |

| ACE | İ                      |

| ACE | Ī                      |

| ACE |                        |

| ACE |                        |

| ACE |                        |

ACE

ACE ACE

ACE

ACE ACE ACE

ACE

ACE ACE

ACE

ACE

ACE

ACE

ACE

ACE ACE

ACE ACE

ACE

ACE

ACE

ACE

ACE PC0 ELAG1 IRO ACE PC0 FLAG2 IRO

ACE\_PC0\_FLAG3\_IRQ ACE PC1 FLAG0 IRO ACE\_PC1\_FLAG1\_IRC ACE\_PC1\_FLAG2\_IR

ACE PC1 FLAG3 IRO

ACE PC2 FLAG0 IRO

ACE PC2 FLAG1 IRO

ACE\_PC2\_FLAG2\_IRQ

ACE\_PC2\_FLAG3\_IRQ

ACE\_ADC2\_DATAVALID\_IR

ACE ADCO CALDONE IRC

ACE ADC1 CALDONE IRC

ACE ADC2 CALDONE IRC

ACE ADCO CALSTART IRC

ACE\_ADC1\_CALSTART\_IR

ACE\_ADC2\_CALSTART\_IR

ACE\_COMP0\_FALL\_IRC ACE COMPLEAU IRC

ACE COMP2 FALL IRC

ACE\_COMP3\_FALL\_IRC

ACE\_COMP4\_FALL\_IRC

ACE COMP5 FALL IRC

ACE\_COMP6\_FALL\_IRC

ACE\_COMP7\_FALL\_IRQ ACE\_COMP8\_FALL\_IRC

ACE\_COMP9\_FALL\_IRC

ACE COMP10 FALL IRO 54 more ACE specific interrupts

### GPIO\_3\_IRQ to GPIO\_31\_IRQ cut

### Configuring the NVIC (3)

• Interrupt Active Status Register - 0xE000E300-0xE000E31C

| Address    | Name    | Туре | Reset Value | Description                                 |

|------------|---------|------|-------------|---------------------------------------------|

| 0xE000E300 | ACTIVE0 | R    | 0           | Active status for external interrupt #0-31  |

|            |         |      |             | bit[0] for interrupt #0                     |

|            |         |      |             | bit[1] for interrupt #1                     |

|            |         |      |             |                                             |

|            |         |      |             | bit[31] for interrupt #31                   |

| 0xE000E304 | ACTIVE1 | R    | 0           | Active status for external interrupt #32-63 |

|            | -       | -    | -           | -                                           |

### **Interrupt Priority (2)**

27

Interrupt Priority Level Registers

- 0xE000E400-0xE000E4EF

| Address    | Name   | Туре | Reset Value | Description                           |

|------------|--------|------|-------------|---------------------------------------|

| 0xE000E400 | PRI_0  | R/W  | 0 (8-bit)   | Priority-level external interrupt #0  |

| 0xE000E401 | PRI_1  | R/W  | 0 (8-bit)   | Priority-level external interrupt #1  |

|            | -      | -    | -           | -                                     |

| 0xE000E41F | PRI_31 | R/W  | 0 (8-bit)   | Priority-level external interrupt #31 |

|            | -      | -    | -           | -                                     |

### **Interrupt Priority**

- What do we do if several interrupts arrive at the same time?

- NVIC allows to set priorities for (almost) every interrupt

- 3 fixed highest priorities, up to 256 programmable priorities

- 128 preemption levels

- Not all priorities have to be implemented by a vendor!

| Bit 7       | Bit 6 | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit O |

|-------------|-------|-------------------------------|-------|-------|-------|-------|-------|

| Implemented |       | Not implemented, read as zero |       |       |       |       |       |

- SmartFusion has 32 priority levels, i.e., 0x00, 0x08, ..., 0xF8

- Higher priority interrupts can pre-empt lower priorities

- Priority can be sub-divided into priority groups

- splits priority register into two halves, preempt priority and subpriority

- preempt priority: indicates if an interrupt can preempt another

- subpriority: used if two interrupts of same group arrive concurrently

### **Preemption Priority and Subpriority**

28

| Priority Group | Preempt Priority Field | Subpriority Field |

|----------------|------------------------|-------------------|

| 0              | Bit [7:1]              | Bit [0]           |

| 1              | Bit [7:2]              | Bit [1:0]         |

| 2              | Bit [7:3]              | Bit [2:0]         |

| 3              | Bit [7:4]              | Bit [3:0]         |

| 4              | Bit [7:5]              | Bit [4:0]         |

| 5              | Bit [7:6]              | Bit [5:0]         |

| 6              | Bit [7]                | Bit [6:0]         |

| 7              | None                   | Bit [7:0]         |

### Application Interrupt and Reset Control Register (Address 0xE000ED0C)

| Bits  | Name          | Туре | Reset<br>Value | Description                                                                                                                                                                 |

|-------|---------------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | VECTKEY       | R/W  | -              | Access key; 0x05FA must be written to this field to write<br>to this register, otherwise the write will be ignored; the<br>read-back value of the upper half word is 0xFA05 |

| 15    | ENDIANNESS    | R    | -              | Indicates endianness for data: 1 for big endian (BE8)<br>and 0 for little endian; this can only change after a reset                                                        |

| 10:8  | PRIGROUP      | R/W  | 0              | Priority group                                                                                                                                                              |

| 2     | SYSRESETREQ   | w    | -              | Requests chip control logic to generate a reset                                                                                                                             |

| 1     | VECTCLRACTIVE | w    | -              | Clears all active state information for exceptions;<br>typically used in debug or OS to allow system to recover<br>from system error (Reset is safer)                       |

| 0     | VECTRESET     | W    | -              | Resets the Cortex-M3 processor (except debug logic),<br>but this will not reset circuits outside the processor                                                              |

# Exercise: How many preemption priorities and subpriority levels do we get on the Smart Fusion if we set Priority Group to 5?

| -3<br>-2<br>-1 | Reset<br>NMI<br>Hard Fault | Preempt levels<br>with priority<br>group set to 5 | Subpriority<br>levels |    |

|----------------|----------------------------|---------------------------------------------------|-----------------------|----|

| 0x00 —         | Programmable<br>Exceptions |                                                   |                       | 31 |

### What exactly is an interrupt handler?

### PRIMASK, FAULTMASK, and BASEPRI

- What if we quickly want to disable all interrupts?

- Write 1 into PRIMASK to disable all interrupt except NMI MOV R0, #1

- MSR PRIMASK, RO

- Write 0 into PRIMASK to enable all interrupts

- FAULTMASK is the same as PRIMASK, but also blocks hard fault (priority -1)

- What if we want to disable all interrupts below a certain priority?

- Write priority into BASEPRI

- MOV R0, #0x60

- MSR BASEPRI, RO

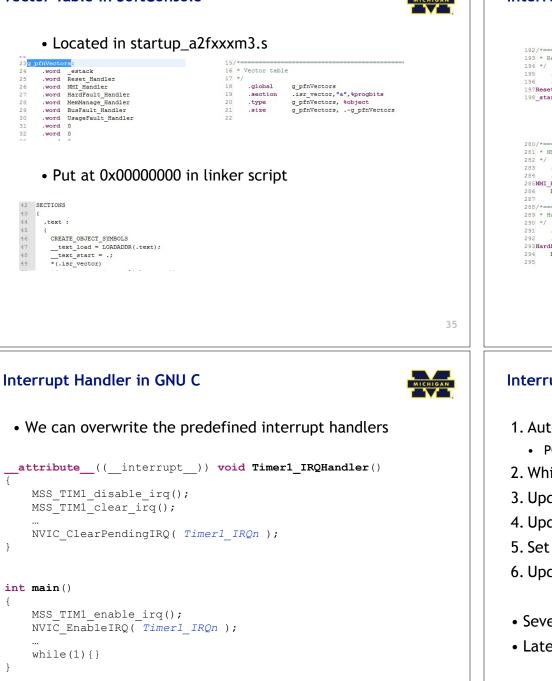

### **Vector Table**

32

- Upon an interrupt, the Cortex-M3 needs to know the address of the interrupt handler (function pointer)

- After powerup, vector table is located at 0x00000000

| Address    | Exception Number | Value (Word Size)                            |

|------------|------------------|----------------------------------------------|

| 0x0000000  | -                | MSP initial value                            |

| 0x00000004 | 1                | Reset vector (program counter initial value) |

| 0x0000008  | 2                | NMI handler starting address                 |

| 0x000000C  | 3                | Hard fault handler starting address          |

|            |                  | Other handler starting address               |

• Can be relocated to change interrupt handlers at runtime (vector table offset register)

### Vector Table in SoftConsole

### **Interrupt Handlers**

36

### **Interrupt Service Routines**

- 1. Automatic saving of registers upon exception

- PC, PSR, R0-R3, R12, LR pushed on the stack

- 2. While bus busy, fetch exception vector

- 3. Update SP to new location

- 4. Update IPSR (low part of PSR) with new exception number

- 5. Set PC to vector handler

- 6. Update LR to special value EXC\_RETURN

- Several other NVIC registers get updated

- Latency: as short as 12 cycles

### **Return from ISR**

### • 3 ways to return from an ISR

| <b>Return Instruction</b>  | Description                                                                                                                                                                                                                                                                      |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BX <reg></reg>             | If the EXC_RETURN value is still in LR, we can use the <i>BXLR</i> instruction to perform the interrupt return.                                                                                                                                                                  |

| POP {PC}, or<br>POP {, PC} | Very often the value of LR is pushed to the stack after entering the exception handler. We can use the POP instruction, either a single POP or multiple POPs, to put the EXC_RETURN value to the program counter. This will cause the processor to perform the interrupt return. |

| LDR, or LDM                | It is possible to produce an interrupt return using the LDR instruction with PC as the destination register.                                                                                                                                                                     |

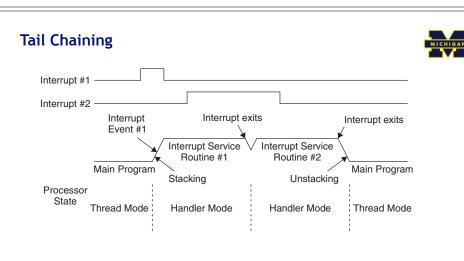

- Unstack and reset SP

- Update NVIC registers

- If first interrupt has same or higher priority

- Skip stacking/unstacking for efficiency

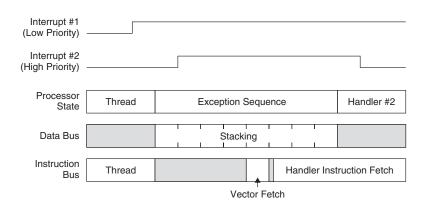

### **Nested Interrupts**

- Built into the Cortex-M3 (not every MCU has this)

- Make sure main stack is large enough!

- Two methods:

- Tail Chaining

- Late Arrival (preemption)

40

### Late Arrival (Preemption)

Main stack must be able to hold maximum number of preemptions!

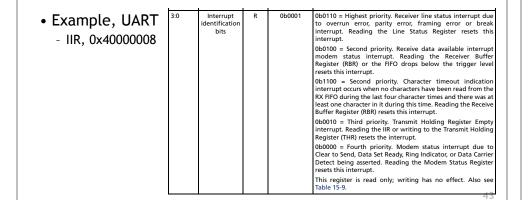

### **Different Concepts of Interrupt Sharing**

- Number of potential interrupts usually larger than interrupt lines availability on Core

- One peripheral often only has one interrupt

- Different types of events are stored in a status register

### **Common Problems and Pit-Falls**

- Too many interrupts

- Your core can't keep up with handling interrupts

- Concurrency issues

- One interrupt handler modifies global variables

- Can be avoided using atomic sections protected through PRIMASK

- Lost interrupts

- It can happen that an interrupt doesn't get treated by the Core

- State machine and peripheral has to be aware of this possibility

- Danger for deadlocks

### ISR Sharing, i.e., Callbacks in C

- There is only one interrupt handler

- Functions have to "subscribe" for events

- Callbacks

- Driver provides function to register a function pointer

- Driver stores function pointers in list

- Upon interrupt, each registered function gets called

typedef void (\*radioalarm\_handler\_t) (void); radioalarm\_handler\_t radio\_alarm\_fired;

void RadioAlarm\_init(radioalarm handler t handler)

radio\_alarm\_fired = handler;

#### attribute\_\_((\_\_interrupt\_\_)) void Timer1\_IRQHandler()

```

alarm_state = FREE;

MSS_TIM1_disable_irq();

MSS_TIM1_clear_irq();

NVIC_ClearPendingIRQ( Timer1_IRQn );

(*(radio_alarm_fired))(); // call the <u>callback</u> function

```

### Summary

- Overwrite default Interrupt Handler

- Initialization

- Enable interrupt in NVIC

- Enable interrupt in Peripheral

- Upon Interrupt

- Clear interrupt in Peripheral

- Clear pending bit in NVIC

- Potentially disable interrupts temporarely