# Augmentation of SPICE for Simulation of Circuits Containing Resonant Tunneling Diodes

Mayukh Bhattacharya and Pinaki Mazumder, Fellow, IEEE

*Abstract*—This paper describes the incorporation of an accurate physics-based model of the resonant tunneling diode (RTD) into Berkeley SPICE version 3F5 and addresses the related direct current (dc) and transient convergence problems caused by the negative differential resistance (NDR) and the exponential nature of the device characteristics. To circumvent the dc convergence problems, a new continuation technique using artificial parameter embedding and a current limiting algorithm are proposed. The studies made in this paper have shown that these techniques are superior to the in-built continuation methods of SPICE, such as Gmin-stepping and Source-stepping, for a large number of circuits of varying sizes. To improve transient convergence performance, the following three algorithms are added to SPICE: a modified forced-convergence algorithm, a new time-step adjustment algorithm, and a modified device voltage prediction algorithm.

*Index Terms*—Circuit simulation, convergence, Newton–Raphson, resonant tunneling diode, SPICE, tunnel diode.

#### I. INTRODUCTION

ESONANT tunneling diodes (RTDs) are the fastest Resulting semiconductor devices currently available in the commercial market. RTDs, in conjunction with high-speed three-terminal devices like high electron mobility transistors (HEMTs), heterojunction field effect transistors (HFETs), and heterojunction bipolar transistors (HBTs), etc., can be co-integrated to design a variety of compact and ultrafast digital circuits [1]. The simulation of RTD circuits requires the development of a RTD device model, which will not only accurately represent the input-output characteristics of the RTD, but will also be suitable for implementation in an existing circuit simulator, like SPICE. The main problem with resonant tunneling device models, incorporating quantum transportation of electrons through a double-barrier structure, has been that their current-voltage relationships have involved complex integrals, making them extremely unsuitable for circuit simulation [2]. As a result, NDR-SPICE [3]—one of the few circuit simulators with in-built RTD models-was based on a piecewise-linear RTD characteristic. The recent development of a physics-based analytical current-voltage equation for the RTD [4] has paved the way to the development of a more accurate simulator.

From the similarities between the nature of the I-V curves of tunnel diodes and RTDs, it can be concluded that if the tunnel

The authors are with the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109-2122 USA (e-mail: mayukh@umich.edu; mazum@umich.edu).

Publisher Item Identifier S 0278-0070(01)00350-5.

diode model was part of the device library of Berkeley SPICE, simulating RTD circuits using such a simulator would be quite simple. However, even though the invention of the tunnel diode by Esaki [5] predates the monolithic fabrication of integrated circuits (ICs), the most popular circuit simulation programs did not introduce any tunnel diode model in them. The main reason behind this is that the development of Berkeley SPICE [6] did not commence until the early 1970s, while the tunnel diode, which could not be monolithically fabricated along with other silicon devices, remained primarily a discrete device and was sparingly used in low-noise amplifier circuits [7].

In this paper, we discuss the incorporation of the physicsbased model of the RTD into the widely used circuit simulator SPICE 3F5, originally developed at the University of California at Berkeley [8]. We also present a few algorithms that have been demonstrated to substantially reduce the number of convergence problems that the basic circuit simulation procedure of SPICE 3F5 may face when simulating RTD circuits. The contributions of this paper include: 1) a new continuation technique (RTD-stepping); and 2) a modified current iteration method. These dc convergence programs are found to be more effective than the in-built continuation methods used in SPICE, namely Gmin-stepping and Source-stepping. Our contributions also include: 1) a modified forced-convergence technique; 2) a new time-step adjustment algorithm; and 3) a modified device voltage prediction algorithm, which is shown to be effective in minimizing transient convergence problems.

It is widely accepted that leading commercial simulators, such as PSPICE of MicroSim, HSPICE of Avant!, and SPECTRE of Cadence Design Systems, exhibit significantly better convergence performances compared to Berkeley SPICE [9]. Therefore, at the outset we must emphasize that numerous limitations of the SPICE program, some of which we have unraveled in this paper, may not be uniformly attributed to many of these commercial simulators. Unfortunately, due to the inaccessibility of their source codes, we are unable to test the behavior of these simulators with the RTD model as a part of their device libraries. On the other hand, thanks to the generous policy of the developers of Berkeley SPICE, the easy availability of its source code has enabled us to conduct extensive experimental studies with the RTD model using this simulator. It is to be noted that the work presented in this paper does not involve building a completely new circuit simulator for the purpose of simulating RTD circuits. However, we intend to show how to augment a circuit simulator such as Berkeley SPICE 3F5 by incorporating accurate and efficient convergence routines so that highly nonlinear circuits consisting of RTDs can be reliably simulated.

Manuscript received June 7, 1999; revised March 20, 2000. This work was supported by the National Science Foundation under Grant NSF-ECS-9618417. This paper was recommended by Associate Editor K. Mayaram.

The organization of the rest of the paper is as follows. In Section II, we present a brief survey of the state of the art in RTD circuit simulation. In Section III, the incorporation of the physics-based model of [4] into SPICE 3F5 is described. In Section IV, the potential dc convergence problems are identified and solutions are proposed. In Section V, the transient convergence problems are explored and ways to minimize them are proposed. In Section VI, the performance of the simulator, with and without the various algorithms proposed in this paper, is studied. Section VII concludes the work summarizing the contributions.

## **II. RTD CIRCUIT SIMULATION STATUS REVIEW**

Over the last decade or so, different device models have been adopted for simulating RTD circuits. The various models reported in the literature can be classified under two major categories: the *physics-based models* and the *nonphysics-based models*. The nonphysics-based models can be further classified into *piecewise-linear (PWL) models* and *non-PWL models* to facilitate further discussion.

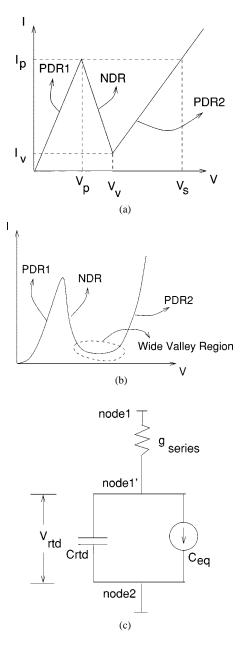

The nonlinear tunneling characteristic of a RTD can be approximated using the appropriate number of linear pieces. The simplest of the PWL models [3] consists of three linear pieces representing the first positive differential resistance (PDR1), negative differential resistance (NDR), and the second positive differential resistance (PDR2) regions, respectively, as shown in Fig. 1(a). Many real RTDs possess a nonlinear PDR1 region, which cannot be adequately modeled by a single linear I-V relationship. For such cases, a two-piece PDR1 has been used [10]. Also, many tunnel diodes and RTDs exhibit a wide valley region, as shown in Fig. 1(b), which cannot be merged with either the NDR or the PDR2 region and hence needs to be modeled by one or more linear I-V pieces [11]. With the exception of [3], all the other PWL approaches reported were not implemented as part of the internal device library of SPICE. These external device representations involve development of an RTD macromodel, combining several of the in-built devices available in the SPICE device library. The usual approach, [10] and [12], is to make use of the *switch* model of SPICE, which can be used to select, based on bias conditions, different current sources (along with resistance and capacitance) representing different linear pieces of the I-V curve of the RTD. Six switches, five resistors, one capacitor, four voltage sources, and one voltage-controlled current source have been used to build a macromodel for a single RTD consisting of four linear I-Vpieces [10]. A multicomponent PWL macromodel for tunnel diodes that does not use the switch model was proposed in [11] and can also be used for RTDs. This macromodel makes use of four diodes, five voltage sources, and five resistors to model a five piece I-V characteristic. A similar switchless PWL method was reported around the same time [13], which could be used for modeling multipeak RTDs using a lesser number of circuit elements than the model of [10].

Among the nonphysics-based approaches, several techniques have been reported that model the I-V curve of the RTD using non-PWL methods. A piecewise-nonlinear method using two diodes with different I-V characteristics—one for each PDR

Fig. 1. (a)–(b) I-V characteristics of the RTD. (a) Piecewise-linear I-V. (b) Typical I-V. The characteristics have a negative differential resistance (NDR) between two positive differential resistances (PDR1 and PDR2). (c) Model of the RTD as added to the device library of SPICE 3F5.

region—has been reported in [14]. A switch is utilized to select the diode corresponding to the PDR1 region only when the voltage across the RTD is less than its peak voltage. In [15], a network consisting of two JFETs, one diode, and a current source was used to model a tunnel diode fairly accurately and could also be used to model RTDs. Just as in the case of tunnel diodes in [16] and [17], RTDs have also been modeled using polynomial and trigonometric curve fitting method [18]. Polynomials of order less than five do not provide adequate accuracy for circuit simulation, even though quadratic and cubic functions can satisfactorily model portions of interest of the I-Vcurve. In this context, a double exponential function of the type  $I = AVe^{-aV} + B(e^{bV} - 1)$  was shown to be quite accurate in approximating the I-V curve of a tunnel diode [19] and is in essence very similar to the RTD macromodel implementation of [14]. In [20], a combination of Gaussian and exponential functions was proposed as an accurate way to model the I-V curve of the RTD. In [3], look-up table-based resonant tunneling device modeling is discussed. Such models can be very accurate and, at the same time, can save the effort involved in parameter extraction.

In recent times, device technology has matured to a point where a correlation is being sought between the device structure of the RTD and material properties on the one hand, and the performance of digital circuits using these devices on the other. This necessitated the development of a physics-based RTD model [4] and modifications thereof [21], [22].

With the exception of [3], all the above mentioned RTD circuit simulation approaches took advantage of the subcircuit definition option in SPICE to implement a multicomponent RTD model and then instantiated the RTD subcircuit at appropriate places in the main circuit netlist. Such ad-hoc implementations are quite cumbersome and can only be adopted while simulating small circuits. That is why the most complex circuit, whose simulation result (using this type of subcircuit approach) has been reported, is an A/D converter [10] consisting of only eight RTDs. Larger circuits have been simulated at the University of Michigan using an internal piecewise-linear model [3]. Models which use unrealistic switch type of devices and/or multiple diodes and resistors unnecessarily increase the number of nodes in the circuit and hence lead to slower simulation with larger memory usage. NDR in I-V characteristic of devices is known to cause convergence problems to circuit simulators employing Newton-Raphson algorithm. Also, exponential characteristics are specially dealt with by a variety of limiting algorithms. When a device is represented externally in the form of a subcircuit, such device-specific convergence aids cannot be easily activated.

As we continue to design larger and more complex RTD circuits, it will become necessary to be able to accurately and efficiently simulate these circuits using SPICE-like simulators. To this end, the physics-based model of the RTD has to be incorporated as an in-built device model and techniques need to be developed to ensure rapid convergence to dc and transient solutions. In this paper, we address these issues by paying attention to the number of iterations needed to solve the circuit nodal equations.

## III. PHYSICS-BASED MODEL OF THE RTD

The detailed derivation of the physics-based model of the RTD used in this paper can be found in [4]. Borrowing the notations from [4], the final simplified model equation can be written as

$$J(V) = J_1(V) + J_2(V) \tag{1}$$

$$J_1(V) = A \ln \left[ \frac{1 + e^{(N-1)(M-1)/M}}{1 + e^{(B-C-n_1V)q/kT}} \right]$$

$$\cdot \left[ \frac{\pi}{2} + \arctan\left(\frac{C-n_1V}{D}\right) \right]$$

(2)

$$J_2(V) = H\left(e^{n_2 q V/kT} - 1\right)$$

(3)

where  $A, B, C, D, n_1, H$ , and  $n_2$  are the seven device physicsrelated parameters which define the I-V characteristics of a particular RTD. The capacitance of the RTD is described by

$$C_{\rm RTD} = \frac{C_{j0}}{\left(1 + \frac{|V|}{V_{bi}}\right)^M} \tag{4}$$

where  $C_{j0}$ ,  $V_{bi}$ , and M are the model parameters.

We modify the basic diode model of SPICE 3F5 to represent an RTD [Fig. 1(c)]. The I-V relation according to (1)–(3) with V is replaced by |V| and J(V), taking negative values when Vis negative to account for the symmetric nature of the I-V relationship of the RTD. In order to avoid numerical instabilities, we have to incorporate a limiting algorithm (Section IV-A-2) for which we need to derive the appropriate V(I) relationships, given by (10) and (12), from the I-V equations. The conductance of the RTD is calculated from the I-V relation and found to be

$$g_{\rm rtd}(V) = \frac{Aqn_1}{kT} \left( \frac{\beta}{1+\beta} + \frac{\alpha}{1+\alpha} \right)$$

$$\cdot \left( \frac{\pi}{2} + \arctan\left(\frac{C-n_1V}{D}\right) \right)$$

$$+ \frac{An_1^2 \ln\left(\frac{1+\beta}{1+\alpha}\right)}{D^2 + (C-n_1V)^2} + \frac{qHn_2}{kT} e^{(qn_2V/kT)}$$

(5)

where

$$\alpha = e^{((B-C-n_1V)q/kT)}$$

$$\beta = e^{((B-C+n_1V)q/kT)}.$$

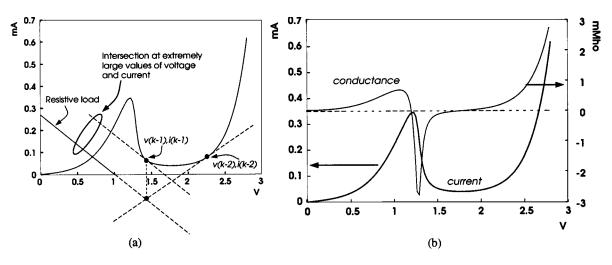

The first derivative (differential conductance) of the I-V curve of a real RTD is shown in Fig. 2(b). From this figure, we can see that even though the derivative is continuous, it does undergo sharp changes near the peak and in the NDR region. Compared to the conventional devices modeled in SPICE, such as BJT or MOSFET, this characteristic does exhibit significantly less smoothness.

#### **IV. DC CONVERGENCE PROBLEMS**

The basic iterative solution technique employed by SPICE to solve the nonlinear equations is based on the Newton–Raphson algorithm (also known as Newton's method) [23]. This algorithm solves equations of the form  $f(\hat{v}) = 0$  for  $\hat{v}$  by starting with an initial guess  $v^{(0)}$  and repeatedly solving the Newton–Raphson iteration equation

$\mathcal{J}\left(v^{(k)}\right)\left(v^{(k+1)}-v^{(k)}\right) = -f\left(v^{(k)}\right)$

or

r

$$v^{(k+1)} = v^{(k)} - \mathcal{J}^{-1}\left(v^{(k)}\right) f\left(v^{(k)}\right)$$

(7)

(6)

for  $v^{(k+1)}$  [the value of v on the (k+1)th iteration] until some convergence criteria are met.  $\mathcal{J}(v) = (d/dv)f(v)$  is called the Jacobian of f at v. Since both f(v) and v are N-dimensional vectors,  $\mathcal{J}(v)$  is an  $N \times N$  matrix. It represents the circuit linearized about v.

Fig. 2. (a) The numerical instability problem for RTD circuits shown with respect to realistic device characteristics. At any iteration, the solution is given by the intersection of the load lines linearized around the previous solution point. Numerical instability can be caused when the lines intersect at very high current values. (b) Conductance of the RTD as a function of the applied bias.

The popularity of Newton's method stems from the fact that it is simple to implement and is quadratically convergent. However, this type of method is only locally convergent. That is, the iterative process is guaranteed to converge to the correct solution only if the initial guess  $v^{(0)}$  is close enough to it. Problems such as oscillations around local minima or maxima of  $f(\hat{v})$  and false-convergence to an undesirable solution may occur if  $v^{(0)}$  is far from the correct one. In such cases, continuation techniques like Gmin-stepping and Source-stepping may have to be used. During Gmin-stepping, a conductance is added to the diagonal elements of the admittance matrix, which is initially set to a high value, virtually causing all nonlinearities to vanish from the circuit altogether. At each succeeding step, the conductance is reduced (usually by a factor of ten) until it becomes infinitesimally small. During source-stepping, all the voltage and current sources in the circuit are gradually stepped up from zero to their actual time-zero values. For further details on Gmin-stepping and Source-stepping techniques, please refer to [23] and [24]. It is well known that the above mentioned continuation techniques are not without limitations. In the last decade, researchers have sought to find robust methods for dc operating point simulation of nonlinear circuits. Sophisticated artificial parameter homotopy methods have been suggested [25]-[28] and used successfully for dc simulation when Gmin-stepping and Source-stepping have failed to converge. For a comprehensive treatment of the subject of homotopy methods for circuit analysis, please refer to [29] and the references therein.

## A. Solving the DC Convergence Problems

To speedup and improve the dc convergence performance of SPICE 3F5 specifically for simulating RTD circuits, we propose a modified limiting algorithm and a new continuation method and compare their performances.

1) Existing Techniques: Devices with exponential I-V characteristics, like diodes, Zener diodes and RTDs, can suffer from numerical instability problems during Newton–Raphson iterations if an intermediate voltage becomes such that the corresponding current through the device becomes unrealistically

large. If there are regions of positive and negative conductance values in the device characteristics, the chances of such conductances being close to the slope of the load line become high. If this happens, the solution of (7) will generate voltages and currents that are extremely high. In the case of RTDs, this is a very common problem that can cause Newton's method as well as simple continuation techniques like Gmin-stepping and Source-stepping to fail. By means of extensive simulation of RTD circuits of various sizes, we have observed that the above mentioned in-built continuation techniques of SPICE 3F5 can fail to converge to dc solutions of many RTD circuits even after a reasonably large number of iterations.

While incorporating a Zener diode model into SPICE2 [6], Laha and Smart [30] had proposed a limiting algorithm to facilitate convergence. Here, we propose a modified limiting algorithm suitable for RTD circuit simulation. From a typical RTD characteristic [see Fig. 2(b)], we can see that the RTD curve in the positive quadrant has a wide range of possible conductance values from large negative (NDR region) to large positive (near the peak in PDR1 and for large values of voltages in PDR2) values. As a result, it is very likely that during Newton–Raphson iterations, the conductance of the RTD for a particular value of its voltage may be very close and of opposite sign to that of the load. The solution of the corresponding linearized circuit will be a point having an unrealistically large absolute value of voltage and current, leading to numerical instability and indicated by SPICE as NaN (Not a Number) [Fig. 2(a)].

2) New Techniques: We propose two new techniques for handling the dc convergence problems of RTD circuits: 1) a limiting algorithm and 2) a continuation method which we shall refer to as *RTD-stepping*.

a) Limiting algorithm: Our limiting algorithm is capable of identifying situations that can give rise to numerical instability. By means of using current iterations instead of voltage iterations, it can circumvent the problem. It is similar to Coons' (Laha and Smart [30]) methods but had to be modified to account for the multivalued nature of the I-V curve of the RTD.

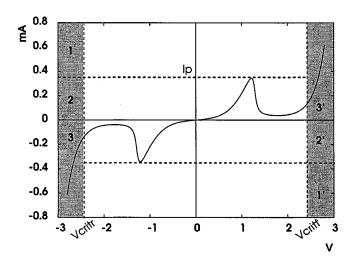

Let us consider Fig. 3 in order to understand the mechanism and conditions of application of our limiting algorithm. First of

Fig. 3. The limiting algorithm proposed in this paper requires dividing the I-V plane of the RTD into several regions as shown here with respect to a realistic device characteristic. The different regions are explained in Table I.

all, we need to find appropriate values of  $V_{\operatorname{crit} r}$  and  $V_{\operatorname{crit} f}$  such that when the RTD voltage during Newton-Raphson iterations goes beyond these values, current iteration, instead of voltage iteration, is used. Fig. 4 explains the difference between current and voltage iteration methods.  $v_{k-1}$  and  $i_{k-1}$  are the RTD voltage and current, respectively, at the (k - 1)th iteration. The solution of the linearized circuit corresponding to this iteration  $(\hat{v}_k, \hat{i}_k)$  are used as the starting point for the kth iteration. In the case of voltage iteration,  $\hat{v}_k$  is used as  $v_k$  and the device current  $i_k$  is computed from I-V relationship. On the other hand, during current iteration,  $i_k$  is used as  $i_k$  and  $v_k$  is calculated from V(I) equation. In the case of RTDs, V(I) can be multivalued, so we need to find approximate single-valued functions to facilitate calculations. In the case of diodes, usually  $V_{\text{crit } f}$  is taken to be the voltage corresponding to the point having minimum radius of curvature. For a simple exponential diode equation, it is easily calculated. However, if we use the complete RTD equation, it can become quite complex. Since that the PDR2 region is dominated by the diode current  $J_2(V)$ ,  $V_{\text{crit}r}$  and  $V_{\text{crit}f}$  can be approximately calculated from  $J_2(V)$  only. We get the following value:

$$V_{\text{crit}f} = -V_{\text{crit}r} = \frac{kT}{qn_2} \ln\left(\frac{kT}{qn_2H}\right).$$

(8)

If, during an iteration, the solution of the linearized circuit is such that the diode voltage-current pair has the value  $(\hat{V}_k, \hat{I}_k)$ and  $|\hat{V}_k| > V_{\text{crit}f}$ , then six different situations can occur depending on the value of  $\hat{I}_k$ . The corresponding zones in the I-Vplane are marked 1, 2, 3, 1', 2', and 3' and the conditions corresponding to each are explained in Table I.

When  $|\hat{V}_k| > V_{\text{crit}f}$ , we may have to resort to current iterations instead of voltage iterations, but we should also check if there was a substantial change in the voltages  $V_{k-1}$  and  $\hat{V}_k$ . This threshold is taken to be  $2kT/qn_2$  [30]. Thus, current iteration is performed if  $|\hat{V}_k| > V_{\text{crit}f}$  and  $|\hat{V}_k - V_{k-1}| > (2kT/qn_2)$ .

Due to the multivalued nature of the V(I) relationship of the RTD

$$V = J^{-1}(I) \tag{9}$$

we have to consider several possible situations depending on the values of  $\hat{V}_k$  and  $\hat{I}_k$  as compared to  $I_p$ , the peak current of the RTD, such that  $J^{-1}(I)$  can be made single-valued. For this purpose, we need to manipulate (1) to extract approximately: 1) the peak current of the RTD; 2) the analytical expression for PDR1 only; and 3) the analytical expression for PDR2 only. Now, 3) is easily approximated by  $J_2(V)$  given by (3) and we have

$$V = \frac{kT}{qn_2} \ln\left(\frac{I}{H} + 1\right). \tag{10}$$

The peak current 1) can be approximated from  $J_1(V)$  expression given by (2) as

$$T_p \approx A \arctan\left(\frac{C}{D} + \frac{\pi}{2}\right).$$

The PDR1 region 2) can be extracted from the expression of  $J_1(V)$  as:

$$I = I_p \ln \frac{1 + e^{(B - C + n_1 V)q/kT}}{1 + e^{(B - C - n_1 V)q/kT}}$$

(11)

from which we can derive

1

$$V = \frac{kT}{qn_1} \ln\left(\frac{e^{I/I_p} - 1}{2e^{(B-C)q/kT}} + \sqrt{\left(\frac{e^{I/I_p} - 1}{2e^{(B-C)q/kT}}\right)^2 + e^{I/I_p}}\right)$$

(12)

where I is the absolute value of the RTD current. If the RTD current is negative, then the corresponding voltage will also be negative. These equations are not exact but close enough to derive the approximate voltages, which are reasonably low-valued and from which Newton–Raphson can carry on iterations to find the correct dc solution.

## **Modified Limiting Algorithm**

}

$$\begin{split} & \text{if}(|\hat{v}_k| > v_{critf} \text{ and } |\hat{v}_k - v_{k-1}| > \epsilon) \{ \\ & i_k = \hat{i}_k; \\ & \text{if} \; (\hat{v}_k \cdot i_k > 0 \text{ or } (\hat{v}_k \cdot i_k < 0 \text{ and } |i_k| > I_p)) \{ \\ & v_k \text{ is given by (10) with } I \text{ replaced by } |i_k|; \\ \} \text{ else } \{ \\ & v_k \text{ is given by (12) with } I \text{ replaced by } |i_k|; \\ \} \\ & g_k \text{ is given by (5); } \\ & \text{if} \; (i_k < 0) \; v_k = -v_k; \end{split}$$

b) RTD-stepping: Due to the wide range of conductance values proffered by the neighborhood of the valley region of the RTD along with its exponential I-V, numerical instabilities can occur that can adversely affect dc convergence. Standard continuation techniques like Gmin-stepping and Source-stepping may be able to overcome such problems in some cases. Gmin-stepping effectively linearizes nonlinear devices and hence, during initial Gmin-steps when the NDR region is almost nonexistent, the possibility of having a RTD conductance that is almost parallel to a load line is remote. As Gmin-stepping progresses, the NDR regions of the RTDs in the circuit gradually reappear. Source-stepping can fail for certain RTD characteristics right

**Current Iteration:**

v(k),i(k)

(b)

λ=1

i(k) = i(k)

450

400

₹

v(k) = f(i(k))

Fig. 4. (a) Voltage and (b) current iteration techniques.

TABLE ICRITICAL REGIONS OF THE I-V PLANE AS SHOWN IN FIG. 4

Voltage Iteration:

$v(k) = \hat{v}(k)$

i(k) = f(v(k))

|                                       | $\hat{V}_k > V_{critf}$ | $\hat{V}_k < -V_{critr}$ |

|---------------------------------------|-------------------------|--------------------------|

| $\hat{l}_k > I_p$                     | 3'                      | 1                        |

| $0 < \hat{I}_k < I_p$                 | 3'                      | 2                        |

| $\left  -I_p < \hat{I}_k > 0 \right $ | 2'                      | 3                        |

| $\hat{I}_k < -I_p$                    | 1′                      | 3                        |

in the first step when all sources are zero. When RTD junction voltage is initialized to

$$V_s = \frac{kT}{qn_2} \ln\left(\frac{kT}{\sqrt{2}qn_2H}\right) \tag{13}$$

(a)

l=f(V)

v(k).i(k

û(k),i(k)

v(k-1),i(k-1)

R<sub>load</sub>

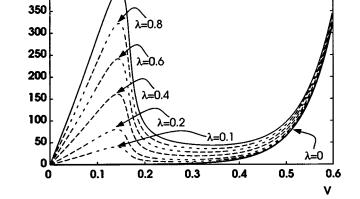

within the next few iterations, the RTD conductance can be very close to the load for certain RTD curves [for an explanation, please refer to Fig. 2(a)]. We have found that several circuits exist whose particular combination of device parameter values can cause nonconvergence (or convergence after large number of iterations) for both Gmin-stepping and Source-stepping, examples of which can be found in Section IV-A. Having discovered the inadequacies of the existing continuation techniques of SPICE 3F5, we investigated other types of artificial parameter homotopy methods [29] specifically for RTD circuits. Our experiments showed that a particular type of parameter embedding with the RTD current given by

$$J(V) = \lambda J_1(V) + J_2(V) \tag{14}$$

where  $\lambda$  is the continuation parameter, is quite effective and succeeded in finding dc operating points in all the difficult to simulate RTD test circuits. The value of  $\lambda$  is increased in small steps (e.g., 0.1), from zero to one. Basically, this type of embedding converts an RTD circuit to a simpler diode circuit and then gradually introduces the tunneling component into the device characteristics (Fig. 5). We refer to this convergence aid as RTD-stepping and, by means of a large number of simulation experiments, we have verified that this type of embedding is more effective than Gmin-stepping and Source-stepping in overcoming dc convergence problems. Unlike Gmin-stepping, RTD-stepping selectively modifies only the RTDs in the circuit. This results in the solution of the converted circuit to be quite close to that of the actual circuit and the solution trajectory (from that of the simplified circuit to that of the actual circuit) is minimized. Thus, chances of nonconvergence are reduced along with the total number of iterations.

/(k-1),i(k-1)

Rload

ŷ(k),i(k)

Fig. 5. The RTD-stepping technique. The NDR becomes prominent as continuation parameter  $(\lambda)$  is stepped up from zero to one.

While it can be argued that sophisticated arc-length tracing techniques [28] and [31] can be used to make the continuation technique more robust, we have intentionally kept RTD-stepping to be simple. This is because, first of all, our experiments with a large number of RTD circuits of varying sizes have shown that RTD-stepping is quite effective in dealing with almost all cases (we are yet to find a circuit where it fails to find a dc solution). Secondly, using advanced tracing algorithms, such as the ones in [25] and [31], we can significantly slow down the simulator (possibly by an order of magnitude [27]) or require the usage of additional commercial mathematical software packages, such as MATLAB [32] as suggested in [33]. The beauty and effectiveness of this simple technique lie in the fact that when  $\lambda = 0$ , the circuit is closer to the actual circuit ( $\lambda = 1$ ) compared to the situation that arises when Gmin-stepping is employed. By selectively modifying only the RTD characteristics, RTD-stepping increases the probability of finding a solution and does not need to invoke complicated solution-trajectory tracing procedures.

We would like to emphasize that RTD-stepping by no means constitutes the first implementation of a continuation or parameter-embedding technique in SPICE. In fact, it is only one in a long line of rich work in this area [29]. The novelty of RTD-stepping lies solely in the fact that it is a simple and effective method for handling dc convergence problems caused by the folded-back I-V characteristic of RTD. Circuits composed

of conventional devices, such as BJTs and MOSFETs (Schmitt trigger circuit or thyristor circuit modeled by back-to-back n-p-n-p-n-p BJTs), may also exhibit NDR in their terminal behavior [34] and can cause convergence problems to circuit simulators. Many of the techniques found in the literature (e.g., [25], [31], and [33]) can be used to solve these problems.

# V. TRANSIENT PROBLEMS

In the case of transient analysis of circuits, SPICE relies on time itself to be the continuation parameter and hence tries to overcome transient convergence problems simply by reducing the time-step until convergence is achieved. This works well for most conventional circuits-the only few known failures (giving the infamous time-step too small warning) are due to exceptionally fast switching occurring in the circuit and are very uncommon. As long as the solution waveforms are continuous, it should be possible to achieve convergence by taking a smaller time-step because, with small time-steps, the solution at one time-point becomes closer to the region of convergence for the solution at the next time-point. However, in the case of RTDs, extremely fast switching is very common and hence transient simulation often runs into trouble. We call this problem by its traditional name—the *time-step too small problem*. Unlike the above problem, where SPICE explicitly lets the user know that there is a transient convergence problem, we have discovered a different kind of transient convergence problem unique to RTD circuits. This is due to insufficiently small time-step that results in convergence to an undesirable solution; and there is no definite way of knowing that such a false convergence has occurred. We refer to this type of transient convergence problem as the coarse time-step problem and explain it below with a simplified example.

Unlike conventional circuits, the nodal equations of an RTD circuit can have more than one solution and this number can undergo a sudden change with time. Thus, the problem of tracing a single operating point gradually varying with time can often transform itself into one of finding multiple operating points and choosing the right one from them. Unfortunately, there is no known reliable method that can be used with the currently available commercial circuit simulators to find unexpected multiple operating points. In certain NDR circuit topologies, the nodal equations can take such shapes that the simulator can converge to an undesirable solution due to large time-step at critical time-points. We have observed that certain RTD circuits (e.g., monostable bistable transition logic elements (MOBILE) [35]) may exhibit this type of problem.

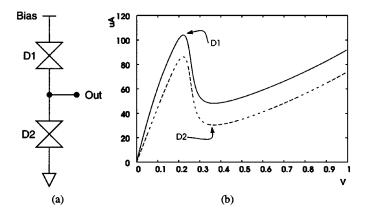

The circuit shown in Fig. 6(a) is a simplified form of a MO-BILE inverter without the control transistors. Even though this circuit will not operate as an inverter, it will help us demonstrate the simulation problems in a simple way. When  $V_{cc}$  is ramped up from 0 V, the output should switch from low to high since D1 has a higher peak current ( $I_{p1}$ ). However, for several different combinations of I-V curves of D1 and D2, with  $I_{p1} > I_{p2}$ , it has been observed that the simulation results do not show an output switch for a well designed MOBILE circuit. Here, we show what may cause such a problem. The circuit can be described by the simple nodal equation

$$f(v_0) = i_1(v_{\text{bias}} - v_0) - i_2(v_0) = 0.$$

(15)

Fig. 6. (a) A series RTD circuit. (b) RTD characteristics corresponding to the devices *D*1 and *D*2.

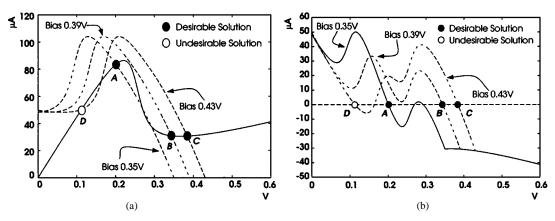

Fig. 7(b) shows  $f(v_0)$  for various values ( $V_{\text{bias}}$  is being ramped up from zero). Fig. 7(a) is the load-line diagram which explains the operation of the circuit of Fig. 6. The solid line represents the RTD D2 while the dashed lines represent the RTD D1, whose load-line is gradually moving to the right as the bias voltage is being increased. To demonstrate the switching event, we select three bias voltages—0.35, 0.39, and 0.43 V. Initially, when the bias voltage is 0 V, the only possible solution is at the origin of the plot in Fig. 7(b). With increasing bias, the solution moves such that it remains at the intersection point of the PDR1 regions of D1 and D2. For example, when the bias voltage is 0.35 V, the solution corresponds to point A in Fig. 7(b). When the bias voltage is 0.39 V, the two PDR1 regions do not intersect anymore, switching has already taken place, and the only possible solution is at B. When the bias is further increased to 0.43 V, it is not difficult to find the desirable solution point C if the starting seed was close to B. However, if it so happens that, due to increased time-step size, the scenario corresponding to bias voltage 0.39 V is skipped, then the simulator may converge to the solution point D instead of the desired point C, since D is closer to the starting solution A.

We can conclude that the sudden increase in the number of solutions for the nodal equations can cause false convergence if the solutions are closely spaced and the time-step is not small enough to detect the change.

## A. Solving the Transient Convergence Problems

1) Existing Techniques: For conventional circuits, the timestep too small problem is usually attributed to discontinuities in the device model and hence is treated more as a modeling problem than a simulation problem. Since an infinitely fast change of a node voltage is unrealistic for such circuits, usually connecting a small capacitor from the problematic node to the ground can slow down the transition and help the simulator. However, in the case of RTDs, it is not unrealistic to have extremely fast switching [36], primarily because tunneling is a fast mechanism that is not limited by drift transit time and does not have delay associated with minority charge storage [2]. Also, since the devices themselves have very low capacitances, adding an external one, however small, may result in affecting the true response of the circuit.

Fig. 7. The coarse time step problem demonstrated using the circuit of Fig. 6. (a) The load lines with varying bias. (b) Plots for (15).

Coarse time-step problems, in the case of conventional circuits, are usually handled by reducing the maximum time-step that the simulator is allowed to take. However, this cannot be a good solution for NDR circuit simulation. This is because, first of all, the simulation is going to become extremely slow. Secondly, the coarse time-step problem is not explicitly observed by the user because the simulator does converge, albeit to an undesirable solution.

# 2) New Techniques:

a) The time-step too small problem: This problem, in the case of RTD circuit simulation, was first addressed in [3] with respect to a piecewise-linear RTD model. A forced-convergence routine was proposed to overcome this problem. For piecewise-linear RTD models, it is very easy to detect this type of convergence problems and also to implement the forced-convergence algorithm since the entire RTD model had only three different conductance values corresponding to the three different linear pieces. Using the knowledge of the three different conductances and well-defined peak and valley voltages, one could easily detect a simulator oscillation between two adjacent pieces of the model and *force* the iterations to move to the third piece. For the physics-based model, implementation of the forced-convergence routine has to be a little different. In this case, the convergence problem is found to occur around the peak only because of its sharp nature, rather than around the valley which is usually wide.

The modified forced-convergence algorithm that we propose here is much the same in concept as the one proposed in [3] but with some modifications. First of all, since there is no well defined peak voltage in the physics-based model and since the oscillation usually occurs around a voltage that is in the NDR region, we need to define a peak *region* rather than a peak voltage. The peak region can be approximated by differentiating the tunneling current portion of the I-V characteristics of the RTD, equating it to zero, and solving for voltage. For the purpose of identifying proximity to the peak region, we use  $\pm 20\%$  of this approximate solution given by

$$V_{\text{peak}} \approx \frac{C - 0.577D}{n1}.$$

(16)

Once we detect that the operating point is within this region, we can detect a nonconvergence if the simulator's internal time-step comes too close to the minimum possible time-step. If both these conditions are met, we simply force the next iteration to begin from  $V_s$  given by (13) in the PDR2, which, as we have seen before, is a good choice for dc convergence—having a conductance approximately equal to  $1/\sqrt{2}$ .

# The Forced-Convergence Algorithm

```

if (current-step-size < 10× minimum-step-size

and current-operating-point is close to the RTDs peak) {

V_{RTD} = Given by (13);

I_{RTD} = Given by (1) with V replaced by |V_{RTD}|;

if (V_{RTD} < 0) I_{RTD} = -I_{RTD};

g_{RTD} = Given by (5) with V replaced by |V_{RTD}|;

}

```

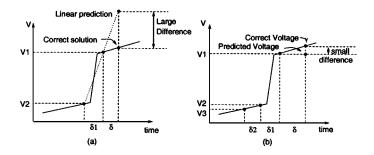

During transient analysis, in the case of diodes, SPICE uses a simple linear extrapolation technique to predict the initial seed to make finding the solution of the next time-point faster and easier. The voltage values of previous two time-points and the corresponding time-step sizes are used to determine approximately the voltage value of the current time-step, and then this value is refined iteratively to arrive at the accurate solution. This mechanism is very effective when the voltage changes smoothly. However, in the case of RTD circuits, abrupt switching of voltage across device can cause the linear extrapolation scheme to be a problem rather than an aid to efficient simulation-for it will cause the simulator to iterate for a significantly larger number of steps. This is illustrated in Fig. 8(a). To overcome this problem, we propose the following simple algorithm for voltage prediction. We check the rate of change of the voltage across the RTD for the last two time points and see if the last rate was significantly larger  $(10\times)$ than the previous one, in which case, instead of using a linearly extrapolated seed, we use the solution of the previous time point as the seed for the current one [see Fig. 8(b)].

## The Voltage Prediction Algorithm

$$\begin{split} & \text{if} \left( \left| \frac{V_1 - V_2}{\delta_1} \right| \geq 10 \times \left| \frac{V_2 - V_3}{\delta_2} \right| \right) \{ \\ & V_{RTD} = V_1; \end{split}$$

} else {

}

$$V_{RTD} = \left(1 + \frac{\delta}{\delta_1}\right) V_1 - \left(\frac{\delta}{\delta_1}\right) V_2;$$

Fig. 8. (a) Ordinary linear voltage prediction method. (b) The modified voltage prediction scheme.

It is to be noted that the linear prediction scheme can also fail during the time-step  $\delta 1$  [see Fig. 8(a)] since the predicted voltage would be close to  $V_2$  and the correct value will be  $V_1$ , which may result in a large error value as well. Obviously, the modified voltage prediction technique described above will not be of any help in this case. However, as will be discussed later in this section, we have implemented a mechanism to cut down the time-step when we detect that the voltage across a RTD is approaching its peak to minimize *the coarse time-step problem*. This has a secondary effect of minimizing the convergence problem that can occur during time-step  $\delta 1$ .

By default, SPICE chooses its time-steps by means of local truncation error (LTE) of its numerical integration routines. The time-step at time instance t + 1 is calculated based on the LTE values at time instance t and certain tolerance parameters which can be controlled by the user [9]. If the LTE at one time instance is large, the time-step for the next time instance is appropriately reduced. However, since RTDs can switch in picoseconds [36], LTE-based time-step calculation may not be able to adjust timesteps, particularly when the desired total transient simulation time is much longer than the device switching time. Purely LTEbased time-step calculation is known to be inadequate in certain cases since the time-steps are allowed to increase to a maximum value of 1/50th of the total simulation time (e.g., [9]), which may lead to undersampling. To avoid this problem, if the upper-limit of this maximum time-step is intentionally set to a small value by the user, simulation can become slow.

b) The coarse time-step problem: The coarse time-step problem can be handled by simply reducing the allowable time-step size in the .TRAN line of the SPICE input file. However, this can only be done if the user *knows* that such a problem can occur while simulating the circuit since the simulator will not be able to identify and report such a problem. Also, reducing time-step leads to increasing the simulation time since the circuit will now be simulated at a larger number of time-points.

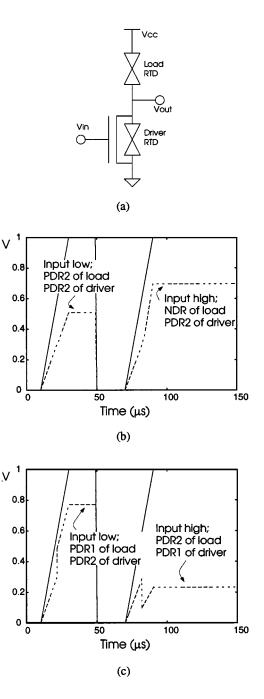

To solve this problem, we propose an algorithm by which the simulator can automatically adjust the time-step only when necessary. Our simple technique is as follows: we simply detect if the voltage across a RTD is approaching its peak or not. If it is approaching the peak, then we reduce the time-step. The customary time-step reduction factor used in SPICE is 1/8, which has been found to be sufficient for this purpose as well. This simple method has been found to be very effective in avoiding false-convergence problems at the cost of only a few extra time-steps. For instance, in the case of a particular

Fig. 9. (a) A MOBILE-type circuit. (b) Simulator fails to detect switch from high to low (without time-step adjustment). (c) Modified time-step adjustment method detects switch from high to low (with time-step adjustment). Solid lines represent  $V_{cc}$  while dashed lines represent the output voltage. Input changes from 0 to 5 V at 60  $\mu$ s.

circuit which consisted of two RTDs connected in a series [as in Fig. 9(a)], when the bias voltage is slowly ramped up from zero, the voltage at the common node of the two RTDs may exhibit convergence to an undesirable value [see Fig. 9(b)] if the user-defined time-step is larger than  $0.4 \,\mu s$ . When the time-step is set to  $0.4 \,\mu s$ , the simulator converges to the expected solution [see Fig. 9(c)] but does so using 406 time-steps. On the other hand, when the time-step adjustment scheme is employed, the user-defined time-step could be as coarse as  $1.8 \,\mu s$  (resulting in 139 time-steps) with no false convergence problems [see Fig. 9(c)].

TABLE II Nonlinear Dependent Current Source Circuits, Which SPICE 3F5 Fails to Simulate

| Rload | V <sub>su</sub> | D      | Iterations     |

|-------|-----------------|--------|----------------|

|       |                 |        | before failing |

| 5050  | 4.6             | 0.0055 | 509            |

| 2080  | 1               | 0.0064 | 459            |

| 5050  | 4.6             | 0.0058 | 474            |

| 5050  | 4.6             | 0.0064 | 503            |

| 6040  | 5.5             | 0.0052 | 504            |

| 7030  | 6.4             | 0.0058 | 464            |

| 8020  | 7.3             | 0.0049 | 433            |

## VI. RESULTS

## A. DC Operating Point Results

SPICE 3F5 fails to simulate a large number of RTD circuits in which the RTD models are nonlinear voltage dependent current sources defined externally as subcircuits. Here we present examples of such circuits for which the basic topology is the same-a voltage divider circuit consisting of a series-connected RTD and a resistor. We could find a large number of combinations of values of the supply voltage, load resistance, and the value of the parameter D of the RTD, which SPICE could not simulate using Newton's method combined with Gmin-stepping and Source-stepping techniques. All these circuits could be easily simulated using the in-built RTD model within 10-15 Newton's iterations. However, since the in-built model uses a different initial voltage, we cannot really compare the performances of the two implementations. These examples only help demonstrate the weakness of the externally represented nonlinear voltage dependent current source model. For the results presented in Table II, the basic RTD parameters were:  $A = 1 \times 10^{-4}, B =$ 0.0456, C = 0.0689, D =variable,  $n_1 = 0.430, n_2 = 0.4373,$ and  $H = 1.43 \times 10^{-8}$ . The series resistance of the RTD was taken to be  $20 \Omega$ .

In order to test our in-built RTD model of SPICE 3F5, we used a simple circuit consisting of a BJT driver and a series combination of two RTDs as the load. The two RTDs had area factors of 0.1 and 0.11, respectively, and had the following model parameter values:  $R_{\text{series}} =$  variable, A = variable, B = 0.035, C = 0.1472, D = variable,  $n_1 = 0.115$ , H = variable, and  $n_2 = 0.1201$ . The transistor used is the default npn BJT model of SPICE 3F5. When the four parameters ( $R_{\text{series}}$ , A, D, and H) were perturbed, we observed that in some cases, ordinary SPICE 3F5 had problems in finding the dc operating point. We found that simply applying RTD-stepping can improve the performance in many such cases. However, the limiting algorithm proved to be the most effective. The results are presented in Table III.

#### B. DC Convergence for Larger Circuits

We have applied the dc convergence methods proposed in this paper—RTD-stepping and the limiting algorithm—to a large number of RTD circuits and have obtained satisfactory results. For instance, while simulating the quantum-MOS (QMOS or RTD/CMOS) circuits of varying sizes, we have observed that

TABLE III Comparison of Performance of DC Convergence Algorithms (Number of Iterations Before Convergence or Failure). P = Plain Newton's Method; G = Gmin-Stepping; S = Source-Stepping; R = RTD-Stepping; PL = Plain Newton's Method with Limiting Algorithm

| <b>R</b> <sub>series</sub> | Α        | D      | H         | SPICE 3F5 | RTD-stepping | Limiting Algo. |

|----------------------------|----------|--------|-----------|-----------|--------------|----------------|

| 0                          | 8e-05    | 0.0055 | 1.011e-09 | P 93      | P 93         | PL 35          |

| 0                          | 8e-05    | 0.0046 | 2.211e-09 | P 87      | P 87         | PL 42          |

| 0                          | 8e-05    | 0.0043 | 4.110e-10 | PG 159    | PR 147       | PL 26          |

| 2                          | 9.2e-05  | 0.0043 | 6.110e-10 | PG 159    | PR 151       | PL 37          |

| 4                          | 1.12e-04 | 0.004  | 4.110e-10 | PG 158    | PR 152       | PL 39          |

| 0                          | 1.12e-04 | 0.0067 | 1.411e-09 | PGS 368   | PR 145       | PL 50          |

| 0                          | 1.16e-04 | 0.0052 | 2.211e-09 | PGS 368   | PR 145       | PL 19          |

| 2                          | 8e-05    | 0.0058 | 1.211e-09 | PGS 386   | PR 152       | PL 26          |

| 2                          | 8e-05    | 0.0064 | 1.211e-09 | PGS 434   | PR 152       | PL 32          |

| 4                          | 8.8e-05  | 0.0064 | 8.110e-10 | PGS 369   | PR 152       | PL 42          |

| 4                          | 1.08e-04 | 0.0043 | 1.211e-09 | PGS 380   | PR 152       | PL 36          |

| 4                          | 1.12e-04 | 0.0064 | 1.211e-09 | PGS 368   | PR 152       | PL 28          |

| 2                          | 1e-04    | 0.0061 | 2.211e-09 | Fail, 428 | PR 152       | PL 20          |

| 4                          | 1.04e-04 | 0.0046 | 1.011e-09 | Fail, 434 | PR 152       | PL 26          |

| 6                          | 1e-04    | 0.0055 | 1.411e-09 | Fail, 427 | PR 152       | PL 25          |

| 10                         | 1.04e-04 | 0.0046 | 1.211e-09 | Fail, 436 | PR 152       | PL 53          |

| 16                         | 9.6e-05  | 0.0052 | 1.411e-09 | Fail, 429 | PR 152       | PL 28          |

| 18                         | 8.8e-05  | 0.0055 | 1.011e-09 | Fail, 437 | PR 152       | PL 44          |

| 18                         | 8.8e-05  | 0.0058 | 1.011e-09 | Fail, 429 | PR 152       | PL 31          |

| 18                         | 9.2e-05  | 0.0061 | 1.211e-09 | Fail, 429 | PR 152       | PL 21          |

| 18                         | 1.12e-04 | 0.0046 | 1.011e-09 | Fail, 429 | PR 152       | PL 24          |

| 18                         | 1.12e-04 | 0.0058 | 2.211e-09 | Fail, 429 | PR 152       | PL 30          |

in-built continuation techniques in SPICE, like Gmin-stepping and Source-stepping, fail in a number of cases while our continuation method, RTD-stepping, succeeds in finding a dc solution in each of these cases. Some of these examples are presented in Table IV.

## C. Transient Analysis Results

In order to demonstrate the necessity as well as the performance of the modified forced-convergence and the voltage prediction algorithms, we simulated a simple RTD-resistor series pair circuit with the resistor as the load and with the voltage across the pair being swept from 0 to 2 V. We simulated the circuit for various values of the load resistor and different RTD curves. The RTD curves were generated from the following basic model values, with A and D being perturbed:  $R_{\text{series}} =$ 20, A = variable, B = 0.0456, C = 0.0689, D = variable, $n_1 = 0.43, H = 1.43 \times 10^{-8}$ , and  $n_2 = 0.4373$ . The results of the transient simulation of the RTD-resistor circuit are presented in Table V. The results show that the circuits, which cannot be simulated by simple SPICE 3F5 transient analysis procedure, can be simulated with the help of the forced-convergence (FC) routine and that the performance of the FC method can be improved by the modified Voltage Prediction Algorithm (Section V-A-2). It can also be seen that the circuits, which can be simulated ordinarily, can also be simulated by FC at no extra iteration cost. The default options settings of the simulator were used in each of the simulations.

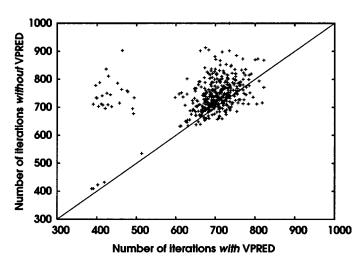

In order to verify the utility of the VPRED algorithm, we simulated a large number of RTD circuits, which exhibit switching, with and without VPRED and plotted the total number iterations required in the transient simulation in both the cases. Fig. 10 shows this plot from which it is clear that VPRED helps reduce the number of iterations on an average and hence makes the simulator more efficient.

49

TABLE IV

RTD CIRCUITS THAT COULD BE SIMULATED BY RTD-STEPPING BUT NOT BY GMIN/SOURCE-STEPPING. SIMULATIONS RUN ON A SUN ULTRA-2 WORKSTATION

Circuit

No. of devices

Type of Simulation

Iterations

CPU time

| Circuit                   | No. of devices      | Type of Simulation    | Iterations | CPU time |

|---------------------------|---------------------|-----------------------|------------|----------|

| QMOS inverter chain       | 90 RTDs, 90 MOSFETs | Operating point       | 169        | 0.49 s   |

| RTD-HBT inverter chain    | 3 RTDs, 3 HBTs      | Operating point       | 135        | 0.15 s   |

| QMOS bistable Carry chain | 3 RTDs, 21 MOSFETs  | Operating point       | 143        | 0.23 s   |

| QMOS bistable Adder       | 10 RTDs, 30 MOSFETs | Operating point       | 147        | 0.23 s   |

| QMOS static Carry         | 3 RTDs, 7 MOSFETs   | DC sweep (500 points) | 1361       | 0.97 s   |

TABLE V Performance of the Forced-Convergence (FC) and the Voltage Prediction (VPRED) Algorithms (Number of Iterations Before Success or Failure)

| Rload | Α        | D       | Without FC | With FC | With FC & VPRED |

|-------|----------|---------|------------|---------|-----------------|

| 2000  | 8.40e-05 | 6.1e-03 | 535        | 535     | 513             |

| 2000  | 8.80e-05 | 6.7e-03 | 409        | 409     | 387             |

| 2000  | 9.20e-05 | 6.7e-03 | 423        | 423     | 402             |

| 2000  | 9.60e-05 | 6.7e-03 | 409        | 409     | 391             |

| 2000  | 8.00e-05 | 4.0e-03 | Fail, 539  | 763     | 692             |

| 2000  | 8.00e-05 | 5.5e-03 | Fail, 576  | 792     | 661             |

| 2400  | 8.00e-05 | 5.8e-03 | Fail, 595  | 742     | 701             |

| 2400  | 1.04e-04 | 4.9e-03 | Fail, 545  | 735     | 708             |

| 2800  | 8.80e-05 | 5.5e-03 | Fail, 552  | 705     | 667             |

| 2800  | 1.04e-04 | 5.8e-03 | Fail, 707  | 779     | 736             |

| 3200  | 8.40e-05 | 4.9e-03 | Fail, 717  | 913     | 742             |

| 3200  | 8.40e-05 | 6.4e-03 | Fail, 672  | 786     | 737             |

| 3200  | 1.04e-04 | 6.1e-03 | Fail, 818  | 898     | 766             |

| 3200  | 1.12e-04 | 5.8e-03 | Fail, 757  | 841     | 709             |

Fig. 10. Effect of applying Voltage Prediction Algorithm (Forced-Convergence Algorithm is used in both cases).

# VII. CONCLUSION

RTDs are at the forefront of emerging technologies that are expected to play a significant role in continuing IC performance improvements beyond what may be possible by scaling alone [37]. Published results indicate that usage of RTDs in conjunction with HBTs or HEMTs in III–V compound materials like Gallium Arsenide (GaAs) or Indium Phosphide (InP) [1], [35], and [38] can lead to the realization of very compact high-performance circuits and systems. The inherent bistability of the device and its picosecond switching speed can be exploited to conceive novel circuit ideas that may find use in future-generation communication systems.

In order to design high-performance RTD circuits, the development of an accurate simulator for such circuits is of central importance. In this paper, we have presented a study of the convergence problems that SPICE-like simulators may face while simulating RTD circuits. We have also presented a suite of techniques that, when added to Berkeley SPICE, can lead to efficient simulation of these circuits. From the results obtained, we can draw several conclusions. First of all, the wide range of negative conductance values of the NDR region of the physics-based RTD curve increases the probability of causing numerical instabilities for the simulator. Second, the in-built continuation techniques of SPICE 3F5, namely Gmin-stepping and Source-stepping, may fail to simulate many RTD circuits. Third, an effective approach for dc convergence seems to be the application of the limiting algorithm of Section IV-A-2 backed up by the RTD-stepping technique. Fourth, during transient analysis, the time-step too small problem can be dealt with by a combination of a modified forcedconvergence algorithm and a voltage prediction scheme (Section V-A-2). Fifth, a time-step adjustment (Section V-A-2) algorithm may prevent convergence to undesirable solutions during transient simulation of certain types of RTD circuits.

The contributions of this paper include: 1) a survey of the various methods that have been employed to simulate RTD or tunnel diode circuits as of this work; 2) incorporation of a physics-based model of the RTD into Berkeley SPICE 3F5; 3) identification of the sources of dc convergence problems for RTD circuits; 4) a new continuation technique (RTD-stepping) and a modified current iteration method for improving dc convergence; 5) identification of different scenarios for transient convergence problems for high-speed RTD circuits; and 6) a modified forced-convergence technique, a new time-step adjustment algorithm, and a modified device voltage prediction algorithm for handling transient convergence problems.

#### ACKNOWLEDGMENT

The authors would like to thank the anonymous reviewers for meticulously reading the original manuscript and making numerous insightful recommendations that helped in improving the quality of the paper. They would also like to thank S. Kulkarni and A. González, University of Michigan, D. Chow and J. Schulman, Hughes Research Laboratories, A. Seabaugh and G. Frazier, Raytheon Systems, T. Baba and T. Uemura, NEC, Japan, and M. Yamamoto, NTT, Japan, for many conducive discussions regarding problems encountered in simulating various RTD circuits. The authors would also like to thank the creators of the SPICE simulator, Prof. D. Pederson and others at the University of California at Berkeley, who adopted a generous policy of distributing the source code of SPICE for further development and augmentation.

#### REFERENCES

- P. Mazumder, S. Kulkarni, M. Bhattacharya, J. P. Sun, and G. I. Haddad, "Digital circuit applications of resonant tunneling devices," *Proc. IEEE*, vol. 86, pp. 664–686, Apr. 1998.

- [2] H. Mizuta and T. Tanoue, *The Physics and Applications of Resonant Tunnelling Diodes*. Cambridge, U.K.: Cambridge Univ. Press, 1995.

- [3] S. Mohan, J. P. Sun, P. Mazumder, and G. I. Haddad, "Device and circuit simulation of quantum electronic devices," *IEEE Trans. Computer-Aided Design*, vol. 14, pp. 653–662, June 1995.

- [4] J. N. Schulman, H. J. D. L. Santos, and D. H. Chow, "Physics-based RTD current–voltage equation," *IEEE Electron Device Lett.*, vol. 17, pp. 220–222, May 1996.

- [5] L. Esaki, "New phenomenon in narrow germanium p-n junctions," *Phys. Rev.*, vol. 109, p. 603, 1958.

- [6] L. W. Nagel, "SPICE2: A computer program to simulate semiconductor circuits," Univ. California, Berkeley, Electron. Res. Lab., Tech. Rep. ERL-M520, May 1975.

- [7] R. G. Swartz, "In perspective: The tunnel diode," in *IEEE Int. Solid-State Circuits Conf.*, 1986, pp. 278–280.

- [8] D. O. Pederson and A. Sangiovanni-Vincentelli, "SPICE 3 Version 3F5 User's Manual," Dept. EECS, Univ. California, Berkeley, CA, Mar. 1994.

- [9] R. M. Kielkowski, *Inside SPICE*, 2nd ed. New York: McGraw-Hill, 1998.

- [10] T. H. Kuo, H. C. Lin, U. Anandakrishnan, R. C. Potter, and D. Shupe, "Large-signal resonant tunneling diode model for SPICE3 simulation," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, Dec. 1989, pp. 567–570.

- [11] R. P. Santoro, "Piecewise-linear modeling of *I–V* characteristics with SPICE," *IEEE Trans. Educ.*, vol. 38, pp. 107–117, May 1995.

- [12] Q.-H. Kuo, H. C. Lin, R. C. Potter, and D. Schupe, "Multiple-valued counter," *IEEE Trans. Comput.*, vol. 42, pp. 106–109, Jan. 1993.

- [13] C. Y. Huang, J. E. Morris, Y. K. Su, and T. H. Kuo, "New method of modeling a multipeak resonant tunneling diode," *Electron. Lett.*, vol. 30, pp. 1012–1013, June 1994.

- [14] D. Neculoiu and T. Tebeanu, "SPICE implementation of double barrier resonant tunnel diode model," in *Proc. Int. Semiconductor Conf.*, *CAS'96 Part 1*, vol. 1, 1996, pp. 181–184.

- [15] K. H. Muller, "RF/microwave analysis," *Intusoft Newslett.*, pp. 12–13, Nov. 1997.

- [16] K. Tarnay, "Approximation of tunnel diode characteristics," *Proc. IRE*, vol. 50, pp. 202–203, Feb. 1962.

- [17] W. F. Chow, Principles of Tunnel Diode Circuits. New York: Wiley, 1964.

- [18] C. E. Chang, P. M. Asbeck, K. C. Wang, and E. R. Brown, "Analysis of heterojunction bipolar transistor/resonant tunneling diode logic for low-power and high-speed digital applications," *IEEE Trans. Electron Devices*, vol. 40, pp. 685–691, Apr. 1993.

- [19] A. Ferendeci and W. H. Ko, "A two-term analytical approximation of tunnel diode static characteristics," *Proc. IRE*, vol. 50, p. 1852, 1962.

- [20] Z. Yan and M. J. Deen, "New RTD large-signal dc model suitable for PSPICE," *IEEE Trans. Computer-Aided Design*, vol. 14, pp. 167–172, Feb. 1995.

- [21] J. N. Schulman, "Extension of Tsu–Esaki model for effective mass effects in resonant tunneling," *Appl. Phys. Lett.*, vol. 72, pp. 2829–2831, June 1998.

- [22] T. P. E. Broekaert, "A monolithic 4-bit 2-Gsps resonant tunneling analog-to-digital converter," *IEEE J. Solid-State Circuits*, vol. 33, pp. 1342–1349, Sept. 1998.

- [23] K. S. Kundert, The Designer's Guide to SPICE and SPECTRE. Norwell, MA: Kluwer, 1995.

- [24] T. M. Najibi, "Continuation methods as applied to circuit simulation," *IEEE Circuits Devices Mag.*, vol. 5, pp. 48–49, Sept. 1989.

- [25] K. Yamamura, T. Sekiguchi, and Y. Inoue, "A fixed-point homotopy method for solving modified nodal equations," *IEEE Trans. Circuits Syst. I*, vol. 46, pp. 654–665, June 1999.

- [26] R. C. Melville, L. Trajković, S.-C. Fang, and L. T. Watson, "Artificial parameter homotopy methods for the dc operating point problem," *IEEE Trans. Computer-Aided Design*, vol. 12, pp. 861–877, June 1993.

- [27] J. S. Roychowdhury and R. C. Melville, "Homotopy techniques for obtaining a dc solution of large-scale MOS circuits," in 33rd Design Automation Conf., June 1996, pp. 286–291.

- [28] L. T. Watson, S. C. Billups, and A. P. Morgan, "Algorithm 652: HOM-PACK: A suite of codes for globally convergent homotopy algorithms," *ACM Trans. Math. Softw.*, vol. 13, pp. 281–310, Sept. 1987.

- [29] L. Trajković, "Homotopy methods for computing dc-operating points," in Wiley Encyclopedia of Electrical and Electronics Engineering, J. G. Webster, Ed. New York: Wiley, 1999, vol. 9, pp. 171–176.

- [30] A. K. Laha and D. W. Smart, "A zener diode model with application to SPICE2," *IEEE J. Solid-State Circuits*, vol. SC-16, pp. 21–22, Feb. 1981.

- [31] L. Trajković, E. Fung, and S. Sanders, "HomSPICE: Simulator with homotopy algorithms for finding dc and steady-state solutions of nonlinear circuits," in *Proc. 1998 IEEE Int. Symp. Circuits Syst.*, vol. 6, pp. 227–231.

- [32] MathWorks Inc., MATLAB: The Language of Technical Computing: Using MATLAB, 1999.

- [33] A. Dyes, E. Chan, H. Hofmann, W. Horia, and L. Trajković, "Simple implementations of homotopy algorithms for finding dc solutions of nonlinear circuits," in *Proc. 1999 IEEE Int. Symp. Circuits Syst.*, vol. 6, pp. 290–293.

- [34] L. O. Chua, J. Yu, and Y. Yu, "Bipolar-JFET-MOSFET negative resistance devices," *IEEE Trans. Circuits Syst.*, vol. CAS-32, pp. 46–61, Jan. 1985.

- [35] K. Maezawa, H. Matsuzaki, K. Arai, T. Otsuji, and M. Yamamoto, "High-speed operation of resonant tunneling flip-flop circuit employing a MOBILE (monostable-bistable transition logic element)," in *Dig.* 55th IEEE Annu. Device Res. Conf., Fort Collins, CO, 1997, pp. 94–95.

- [36] T. C. L. G. Sollner, W. D. Goodhue, P. E. Tannenwald, C. D. Parker, D. D. Peck, and H. Q. Le, "Resonant tunneling through quantum wells up to 2.5 THz," in *Conf. Dig. 8th Int. Conf. Infrared Millimeter Waves*, 1983, pp. T5.1/1–2.

- [37] A. Seabaugh, R. Lake, B. Brar, R. Wallace, and G. Wilk, "Beyond-the-roadmap technology: Silicon heterojunctions, optoelectronics, and quantum devices," in *Proc. 1997 MRS Symp.*, vol. 486, pp. 67–77.

- [38] M. Yamamoto, "Resonant tunneling diode and HEMT integrated devices and circuits," in *Proc. 21st Workshop Compound Semiconductor De*vices Integrated Circuits, Scheveningen, The Netherlands, May 1997, pp. 71–76.

Mayukh Bhattacharya received the B.Tech. degree in electronics and electrical communication engineering from the Indian Institute of Technology, Kharagpur, India, in 1992, the M.S. degree in electrical engineering from Virginia Polytechnic Institute and State University, Blacksburg, in 1994, and the Ph.D. degree in computer science and engineering from the University of Michigan, Ann Arbor, in 1999.

He is currently a Research Fellow at the University of Michigan. His research interests include very large scale integration (VLSI) circuit simulation, CAD for VLSI, deep-submicrometer defect and fault modeling, and emerging technologies.

**Pinaki Mazumder** (S'84–M'87–SM'95–F'99) received the B.S.E.E. degree from the Indian Institute of Science, Bangalore, India, in 1976, the M.Sc. degree in computer science from the University of Alberta, Edmonton, Canada, in 1985, and the Ph.D. degree in electrical and computer engineering from the University of Illinois, Urbana-Champaign in 1987.

He is currently with the Department of Electrical Engineering and Computer Science of the University of Michigan, Ann Arbor, as a Professor. Prior to this he was a Research Assistant with the Coordinated Science Laboratory, University of Illinois, Urbana-Champaign for two years. He also was with Bharat Electronics Ltd., Bangalore, India, for over six years, where he developed analog and digital integrated circuits for consumer electronics products. During the summers of 1985 and 1986, he was a Member of Technical Staff at AT&T Bell Laboratories, Naperville, IL. His research interests include VLSI testing, physical design automation, ultrafast digital circuit design, and neural hardware.

Dr. Mazumder is a member of Sigma Xi, Phi Kappa Phi, and ACM SIGDA.