# **Machine-Description Driven Compilers for EPIC Processors**

B. Ramakrishna Rau, Vinod Kathail, Shail Aditya Compiler and Architecture Research HPL-98-40 September, 1998

E-mail: [rau,kathail,aditya]@hpl.hp.com

retargetable compilers, table-driven compilers. machine description, processor description, instruction-level parallelism, EPIC processors, VLIW processors, EPIC compilers, VLIW compilers, code generation, scheduling, register allocation

In the past, due to the restricted gate count available on an inexpensive chip, embedded DSPs have had limited parallelism, few registers and irregular, incomplete interconnectivity. More recently, with increasing levels of integration, embedded VLIW processors have started to appear. Such processors typically have higher levels of instruction-level parallelism, more registers, and a relatively regular interconnect between the registers and the functional units. The central challenges faced by a code generator for an EPIC (Explicitly Parallel Instruction Computing) or VLIW processor are quite different from those for the earlier DSPs and, consequently, so is the structure of a code generator that is designed to be easily retargetable.

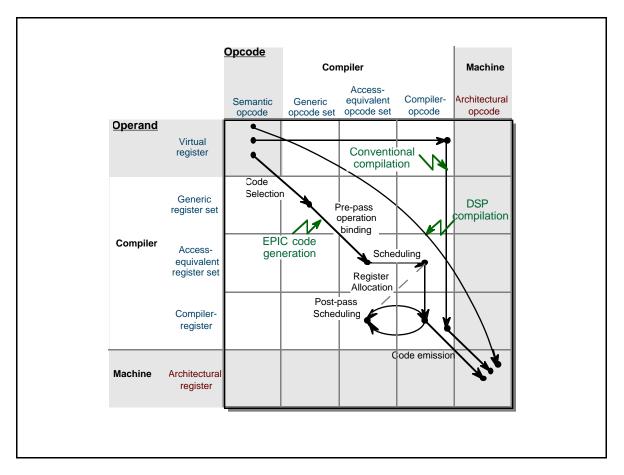

In this report, we explain the nature of the challenges faced by an EPIC or VLIW compiler and present a strategy for performing code generation in an incremental fashion that is best suited to generating high-quality code efficiently. We also describe the Operation Binding Lattice, a formal model for incrementally binding the opcodes and register assignments in an EPIC code generator. As we show, this reflects the phase structure of the EPIC code generator. It also defines the structure of the machine-description database, which is queried by the code generator for the information that it needs about the target processor. Lastly, we discuss general features of our implementation of these ideas and techniques in Elcor, our EPIC compiler research infrastructure.

An abbreviated version of the report will appear in an issue of *Design Automation for Embedded Systems*, Kluwer Academic Publishers, 1999. Presented at the *3<sup>rd</sup> International Workshop on Code Generation for Embedded Processors*, Witten, Germany, March 4-6, 1998.

#### 1 Introduction

In the past, due to the restricted gate count available on an inexpensive chip, embedded digital signal processors (DSPs) have had limited parallelism, few registers and irregular, incomplete interconnectivity [1-3]. As a result, compilers for such processors have focused primarily on the task of code selection, i.e., choosing a sequence of instructions that minimizes the number of instructions executed without requiring more registers than the number present. A large amount of work has been done in this area [4-6]. These DSPs are in many ways reminiscent of the early "attached processors", such as Floating Point Systems' AP-120B and FPS-164 [7] for which, due to their irregular and idiosyncratic architecture, it was very difficult to write high quality compilers. Both sets of processors share the property that they were typically designed to support some particular computation, such as convolution or (in the case of the AP-120B) the FFT, and the data paths reflected this. Typically, such machines were horizontally microprogrammed, and their programmability came as an afterthought; the read-only control store was replaced by a writeable one. In effect, these processors were like special-purpose ASICs with a thin veneer of programmability. However, in one important respect these machines were already taking the first step towards VLIW in that the operations that they executed were not micro-operations but, rather, operations such as floating-point adds and multiplies.

The first-generation of VLIW processors¹ were motivated by the specific goal of cleaning up the architecture of the attached processor sufficiently to make it possible to write good compilers [8, 9]. Such processors typically had higher levels of instruction-level parallelism (ILP), more registers, and a relatively regular interconnect between the registers and the functional units. Furthermore, the operations were RISC-like (in that their sources and destinations were registers), not "micro-operations" (which merely source or sink their operands from or to buses). Recently, with increasing levels of integration, DSPs have begun to appear that have a VLIW architecture [10, 11]. This current generation of embedded VLIW processors reflects the state of the art of VLIW in the mini-supercomputer space a decade ago [12, 13].

-

<sup>&</sup>lt;sup>1</sup> Note that our use of the term VLIW processor is specifically intended to differentiate it from the array processors of the past and the DSPs of today. Even though these might have certain VLIW attributes, such as the ability to issue multiple operations in one instruction, we view them as being half way between VLIW processors and horizontally microprogrammed processors.

In the meantime, VLIW has continued to evolve into an increasingly general-purpose architecture, providing high levels of ILP and incorporating a number of advanced features [14, 15]. This evolved style of VLIW is termed EPIC (Explicitly Parallel Instruction Computing). Our current research is based on the belief that the EPIC style of architecture will show up in embedded DSPs a few years down the road. In the rest of this report, we shall use the term EPIC to include VLIW as well.

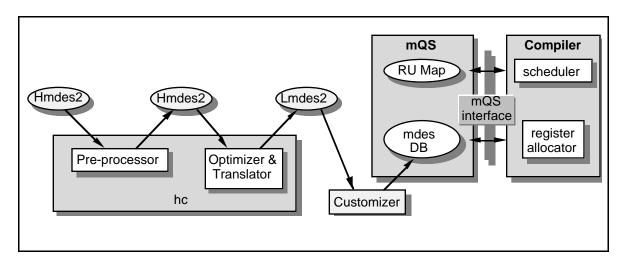

For EPIC processors, since the primary focus is on achieving high levels of ILP, the most important compiler task is to achieve as short a schedule as possible. The scheduler and register allocator are, therefore, the key modules. These two topics have received a great deal of attention over the years in many research communities, resulting in a vast body of literature. In this report, we are concerned not with the scheduling and register allocation algorithms but with the information that EPIC compilers need about the processor for which they are performing these functions. The identification of this information makes it possible to write "table-driven" EPIC compilers which have no detailed assumptions regarding the processor built into the code.

Instead, such a compiler makes queries to a *machine-description database (mdes)* which provides the information needed by the compiler about the processor. Such a compiler can be retargeted to different EPIC processors by changing the contents of this database, despite the fact that the processors vary widely, including in the number of functional units, their pipeline structure, their latencies, the set of opcodes that each functional unit can execute, the number of register files, the number of registers per register file, their accessibility from the various functional units and the busing structure between the register files and the functional units.

An mdes-driven compiler is of particular value in the context of developing a capability to automatically synthesize custom EPIC ASIPs (Application-Specific Instruction-Set Processors), where one of the obstacles, both to the evaluation of candidate designs as well as to the use of the selected one, is that of automatically generating a high-quality compiler for the synthesized processor.

In this report, we discuss the mdes-driven aspects of compilers for EPIC processors. It is important to stress that our goal is not to be able to build an mdes-driven compiler that can target any arbitrary processor. The target space is limited to a stylized class of EPIC processors for which we know how to generate good code using systematic rather than ad hoc techniques. Clearly, if one does not even understand how to write a compiler for a

single target processor using systematic, formal techniques, the goal of automatically generating a compiler for any processor in the permissible space will be impossible to achieve. Also, our focus in this report is restricted to the mdes required by the scheduler and register allocator, since these are the most important modules of an EPIC compiler. Specifically, we shall not address other phases of a compiler such as code selection, partitioning across multiple clusters and optimizations concerned with the memory hierarchy.

The outline of the report is as follows. In Section 2, we describe our space of target EPIC processors. To a large extent, the set of issues that we address in achieving the mdesdriven capability of an EPIC code generator are complementary to the ones that are of primary importance in writing retargetable code generators for contemporary DSPs. In Section 3, we explain the additional issues in EPIC code generation and develop the key concepts of the expanded computation graph, full-connectedness, opcode and register option sets, and access-equivalent operation sets. Section 4 develops the concepts of binding hierarchies for opcodes and registers as well as the Operation Binding Lattice (OBL). It also articulates our model of phase ordered EPIC code generation. In Section 5, we describe all the relevant information about the target machine that has to be stored in the mdes, and in Section 6 we explain how it is used by the EPIC code generator modules. Section 7 provides a brief overview of the implementation of the mdes in Elcor, our EPIC compiler research infrastructure. Section 8 reviews the antecedents of this work, as well as other related work. Section 9 summarizes the contributions of this report.

# 2 The space of target EPIC processors

EPIC processors evolved in response to a different set of emphases than did contemporary DSPs. The first one was that they provide relatively high levels of ILP. The second one was that they lend themselves to the implementation of efficient, high-quality compilers. The space of processors was consciously restricted to promote the latter goal. As a result, the typical structure of an EPIC processor is different in a number of important ways which, in turn, leads to a different set of code generation challenges. We wish to highlight these points of difference.

## 2.1 Key features of an EPIC processor

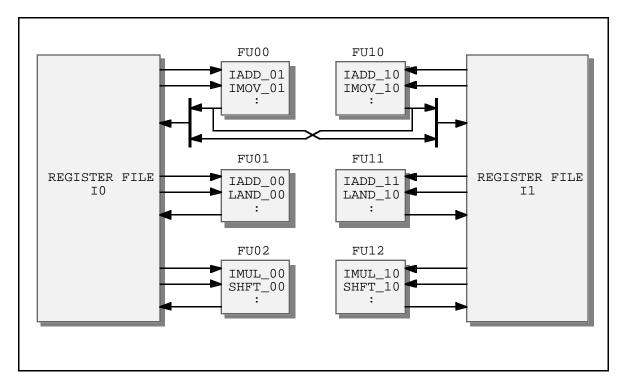

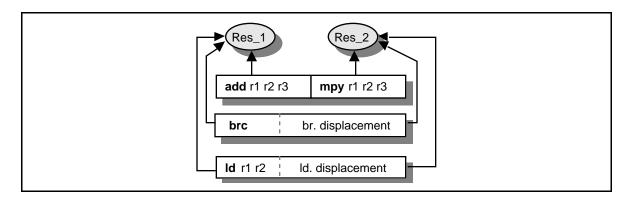

Figure 1 shows an EPIC processor, which we shall use as a running example, throughout this report, to illustrate various points. We first list those features that are the basic

requirements for achieving high levels of instruction-level parallelism while ensuring that it is possible to write an efficient, high quality code generator.

Figure 1: A sample EPIC processor.

• Multiple pipelined functional units. Since the EPIC architecture was developed to exploit ILP, the most basic characteristic of our space of target EPIC processors is the presence of multiple functional units (FUs) that can execute multiple operations in parallel. Often, the parallelism is such as to allow multiple identical operations to be issued simultaneously. In Figure 1, integer add operations can be performed on four of the FUs, whereas integer multiply operations can be performed on the other two FUs. The machine has been designed in such a way that all six FUs can initiate operations simultaneously.

In real machines, there are always at least a few opcodes that take more than one cycle to generate their results. Also, depending on the relative importance of such an opcode, its execution may be not pipelined at all, be fully pipelined (i.e., a new operation can be issued every cycle), or be partially pipelined (e.g., a divide may take 24 cycles to complete, but a new divide can be started every 10 cycles).

- Register-register operations. A fundamental requirement for facilitating the task of writing a scheduler is that it be possible to write all results, produced during the same cycle, to a register file. In certain processors, a result is transient--it is necessary to consume it directly off the result bus either because the result bus is not connected to a register file, or because the register file does not have enough write bandwidth to accomodate this result as well as the other results that are simultaneously produced. All of the operations that consume this result have to be scheduled at precisely the cycle on which this result is produced. Often, this is impossible due to resource conflicts between those operations. It is difficult to write a high quality, efficient scheduler for such a processor. Consequently, in an EPIC processor, all of the operations, other than loads and stores, are such that they operate from register to register. (Optionally, there can be register bypass logic that provides the additional capability to pass the result directly from a result bus to a source bus.)

- **Register files.** Rather than a heterogeneous collection of registers with differing special capabilities and interconnectivity, the registers in an EPIC processor are organized into one or more register files, each of which consists of a number of similar registers.

- Large numbers of registers per register file. Rather than taking the view that most of the operands of the operations executed reside in memory (and providing the requisite memory bandwidth), the view taken is that most operands will be in registers. The expectation is that a variable will primarily be referenced in a register, with, perhaps, an initial load from memory or a final store to memory. Consequently, a relatively large numbers of registers are provided, compared to most contemporary DSPs. The code generator takes advantage of this and is designed with the view that register spill is infrequent, not the norm<sup>2</sup>. This also reduces the memory bandwidth requirement, which is particularly valuable at high levels of ILP.

Competently architected EPIC processors have a number of additional features that we also include within our space of target architectures.

• Multiple register files. From the compiler's viewpoint, the most convenient arrangement is for all similar registers to be in the same register file, e.g., all the 16-bit registers in one file and all the 32-bit registers in another one. But in a highly parallel EPIC processor, this implies very highly ported register files, which tend to be slow

<sup>&</sup>lt;sup>2</sup> This assumption is central to our use of the phase ordering described in Section 4.

and expensive. Instead, such highly ported register files are split into two or more register files, with a subset of the FUs having access to each register file. In our example processor, the integer registers have been divided into two register files, I0 and I1.

- Heterogeneous functional units. When designing a processor that can issue multiple integer operations per cycle, it is unusual for all of the integer or floating-point FUs to be replicas of one another. In Figure 1, the processor has been designed to be able to perform an IADD on every one of four FUs. But on two of them, it can perform an IMOV (copy) operation, while on the other two it can perform an LAND (logical-AND) operation. This leads to a set of heterogeneous FUs which, in the extreme case, are all dissimilar.

- **Shared register ports.** It is often impractical to provide every FU with dedicated register ports for every opcode that it can execute. Opcodes that are provided for completeness, but which are infrequently used, use register ports that they share with other FUs. FU00 and FU10 each need a write port into both register files to permit data to be copied from one register file to the other. Instead of dedicated ports, they share a single write port per register file. Thus, while F00 is writing the destination register of an IMOV\_01 into I1, FU10 cannot be completing an operation at the same time. Correct code generation must honor this constraint.

- Shared instruction fields. Likewise, bits in the instruction word are a valuable commodity, and must often be shared. The instruction format that permits the specification of a long literal may do so by using the instruction bits that would normally have specified, for instance, the third operand of a multiply-add operation. This precludes the multiply-add opcode, but not the two-input multiply or add opcode, from being issued in the same cycle as the opcode that specifies a long literal.

- Interruption model. The schedule constructed by the compiler for a program can be disrupted by events, such as interrupts, page faults or arithmetic exceptions, which require that the execution of the program be suspended and then be resumed after the interrupt or exception handler has been executed. We shall refer to such events, generically, as *interruptions*. We shall consider two hardware strategies for dealing with interruptions. The first one halts the issue of any further instructions, takes a snapshot of the processor state for the executing program, including the state of execution of the pipelined operations, and then invokes the interruption handler. After the handler has executed, the program's processor state is restored, and program execution is resumed. The net effect, from the viewpoint of the program, is that its

execution was frozen in place during the execution of the interruption handler. We refer to this as the *freeze model*.

The second strategy halts the issue of any further instructions, but permits those that have already been issued to go to completion. Once the pipelines have drained, the interruption handler is executed, after which instruction issue takes up where it left off. We refer to this as the *drain model*<sup>3</sup>. Although the drain model is considerably less complex to implement from a hardware viewpoint, it requires that specific measures be taken during scheduling and code generation to ensure correctness. These measures, which are discussed in Section 6, affect the information needed in the mdes regarding execution latencies.

In the case of pipelined branch operations, i.e., branches which have a latency of more than one cycle between the initiation of the branch operation and the initiation of the target operation, we always use the freeze model regardless of the model used for the rest of the operations. Since the semantics of a branch are to alter the flow of control and start issuing a new stream of instructions, the drain model, which would permit the branch to continue to completion, but which would nevertheless prevent any further instructions being issued, is meaningless.

In addition to those mentioned above, EPIC processors can have a number of other features such as predication, control speculation, data speculation, rotating registers and programmatic cache management [14, 15] which, individually and collectively, can have a great impact on the quality of the schedule. Since these features do not introduce any additional issues that are pertinent to the subject of this report, we shall not discuss them further.

## 2.2 The compiler's view of a processor

Conceptually, the compiler is playing the role of a human assembly language programmer. As such, it is not interested in the structural description of the hardware. More precisely, it is only interested in the hardware structure indirectly, to the extent that this is reflected in the architectural description of the machine as might be found in the Architecture Manual. Specifically, rather than needing the equivalent of Figure 1 in the form of an HDL description, it only needs to know, for each opcode, which registers can be accessed as

\_

<sup>&</sup>lt;sup>3</sup> In previous works by the authors, the freeze and drain models have been termed the EQ model and the LEQ model, respectively. We believe that way in which we conceptualized these issues in the past was imprecise, and that our current terminology better reflects our current way of thinking about exception handling.

each of the source and destination operands<sup>4</sup>. Table 1 lists some of the opcodes and the set of registers<sup>5</sup> to which each of the source or destination operands of those opcodes can be bound.

Table 1: The input-output behavior of selected opcodes

| Semantics | Opcode  | Source 1 | Source 2 | Destination |

|-----------|---------|----------|----------|-------------|

| Integer   | IADD_00 | {10}     | {IO}     | {10}        |

| Add       | IADD_01 | {10}     | {10}     | {I0,I1}     |

|           | IADD_10 | {11}     | {I1}     | {I0,I1}     |

|           | IADD_11 | {11}     | {I1}     | {I1}        |

| Integer   | IMUL_00 | {10}     | {10}     | {10}        |

| Multiply  | IMUL_10 | {11}     | {I1}     | {I1}        |

| Сору      | IMOV_01 | {10}     | -        | {I0,I1}     |

|           | IMOV_10 | {11}     | -        | {I0,I1}     |

An *operation* consists of an opcode and a register tuple—one register each per operand. An important point to note is that the choice of register for one operand can sometimes restrict the choice for another operand. Imagine that in our example processor FU00, in addition to the two read ports from I0, also possessed its own read port from I1 which could be used as the input port for either of the inputs of FU00. In this case, IADD\_01 could source a register in either I0 or I1 as its left source and it could source a register in either I0 or I1 as its left source. But it cannot simultaneously source two registers in I1 since it has only one read port from it. Thus the accessibility of registers by an opcode must be specified in terms of which register tuples are legal. It is insufficient to merely specify which registers are accessible on an operand by operand basis. Consequently, the first row for IADD\_00 in Table 1 should be interpreted as stating that every register tuple in the Cartesian product  $\{10\} \times \{10\} \times \{10\}$  is legal.

<sup>&</sup>lt;sup>4</sup> Additionally, for an EPIC processor, it also needs to know the relevant latencies and resource usage of each of these operations, since it is the responsibility of the compiler to ensure a correct schedule. We shall return to this issue later on.

<sup>&</sup>lt;sup>5</sup> As a notational convenience we shall use {I0} and {I1} to refer to the set of all the registers in register files I0 and I1, respectively.

Note that Table 1 does not contain any explicit information about the structure of the hardware. Instead, for each opcode, it specifies which sets of registers can be the sources or destination. The compiler does not need to know about FUs, register files and interconnects; all it needs to know is which opcodes can access which registers. This opcode- and register-centric view will be reflected throughout the report.

## 3 Issues in EPIC code generation

Due to the nature of our space of target EPIC processors, performing traditional code selection for an EPIC processor in a machine-description driven fashion is no different than for a CISC or RISC processor [16-20], depending on whether or not the EPIC processor has complex opcodes such as loads, stores or branches with complex addressing modes. In contrast, retargetable code selection for contemporary DSPs is quite different, because they fall outside of this space on one or more counts<sup>6</sup> [21-24, 5, 25]. Since there is little about traditional code selection that is unique to EPIC, we shall not dwell upon it. However, there are other EPIC-related code selection and code generation steps that are somewhat unique. These are the topic of this section.

#### 3.1 Imperatives in an EPIC code generator

The driving issue in EPIC code generation is that, in general, each type of operation can be executed on more than one FU and that in each of these options the operation may execute out of a different subset of the registers. The code generator is faced with a multiplicity of choices which have to be made in such a way as to minimize the length of the resulting schedule.

Our discussion of the EPIC code generation process makes extensive use of the notion of a computation graph which we define as follows:

**Definition:** A *computation graph* is a directed, bipartite graph whose vertices are either operators or variables. The operators specify the action to be performed upon the variables to which they are connected. The variables serve as the operands of the operators. The operator, along with its operands, constitutes an operation.

available ILP is to be achieved. The second reason is that whereas it may have many "register files", each of them typically has just one or two registers. These two factors have major implications for code selection.

<sup>&</sup>lt;sup>6</sup> There are two main reasons why the traditional DSP falls outside of our space of processors. One is that every operation may not be register-to-register; certain results may have to be consumed right off the result bus, if the

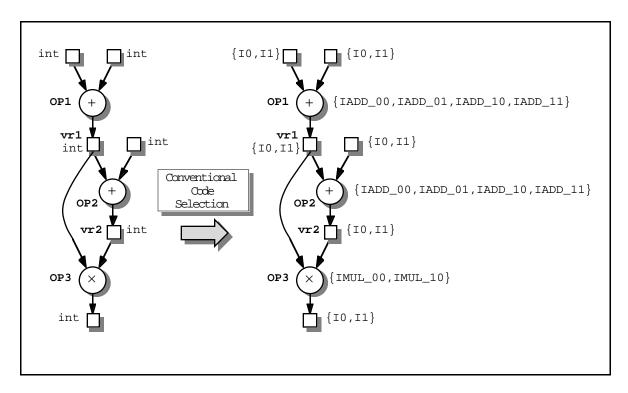

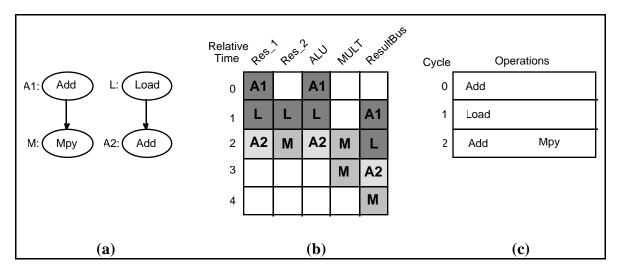

In order to constrast the difference between conventional code generation and EPIC code generation, consider the code fragment in Figure 2, which is intended to be compiled to the machine described in Table 1. On the left side of Figure 2, we have the computation graph for the machine-independent code. The vertices are either operators (circles) or variables (squares). At this stage of compilation, the operators are associated with machine-independent *semantic opcodes* for a virtual machine which specify only the semantics of the operator (e.g. an integer add) but not how it is to be implemented. The variables are associated with machine-independent *virtual registers* which specify the data type of the variable, but nothing about which physical register in the machine is to be used to hold this variable. Conventional code selection rewrites this computation taking into account the types of opcodes that exist in the actual machine, e.g., CISC-style compound opcodes, and the types of registers present. (In the case of our example machine, this is a null step.) At this point, for a sequential processor, code selection is complete and register allocation and scheduling would take place.

Figure 2: A fragment of a computation graph before and after conventional code selection.

In the case of EPIC code generation, the conventional code selection step has merely narrowed the options in Figure 2 down to those listed against OP1, OP2, and OP3 on the

right side of Figure 2. The four opcode options listed against OP1 and OP2 represent all of the ways in which an integer add can be performed on this machine. We refer to them jointly as the generic IADD\_G opcode set. In general, a *generic opcode set* is the set of all the opcodes available for implementing an action having the same semantics. Also, in Figure 2, the options listed for vr1 and vr2 are the union of all the registers in I0 and I1. We refer to them jointly as a generic register set. In general, a *generic register set* consists of all of the registers that can hold a variable of a particular data type. In Figure 2, the opcodes and the operands are both far from being unambiguously specified.

For an EPIC compiler, the primary measure of code quality is the schedule length. The entire code generator is designed with this in mind and, over the years, a number of complex, sophisticated scheduling algorithms have been developed [26-31]. All of these scheduling algorithms benefit from having as many options as possible available to choose from while deciding when and where to schedule each operation. It is desirable, therefore, to avoid making premature code selection decisions. Rather than bind OP1 to use the IADD\_00 opcode, one would rather leave it up to the scheduler to choose which of the four integer add opcodes is best used. This allows the scheduler to use whichever FU happens to be free, with a view to minimizing the schedule length. Doing so constitutes a form of delayed code selection; only after the scheduler is done, do we know which precise opcode has been selected.

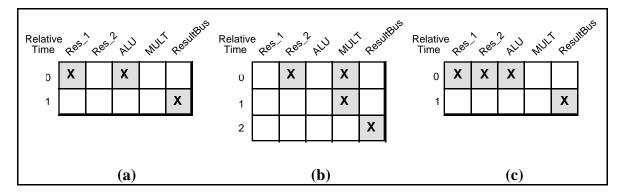

On the other hand, we do wish to constrain the options available to the scheduler to those that the scheduler can handle efficiently. Consider again the example in Figure 2. If the scheduler is given full freedom in selecting which multiply and add opcodes to use, it might end up selecting, for OP1, OP2 and OP3, the opcodes in either Figure 3a or Figure 3b. Referring to Table 1 we see that the choices made in Figure 3a are structurally valid. It is possible to find a register file, I1, which can be the destination of IADD\_01 and the source for IADD\_11 and IMUL\_10. In contrast, the choices made in Figure 3b are jointly incorrect. IADD\_00 can only write to register file I0, whereas IMUL\_10 can only read from register files I1. Thus there is no register which can be allocated to vr1 such that it is accessible by both opcodes. One solution is for the scheduler, in the course of scheduling, to insert an IMOV\_01 operator which copies the result of OP1 from vr1 to a new variable, vr3, which is then read by OP3 (Figure 3c). Now, vr1, v2 and vr3 can be allocated to I0, I1 and I1, respectively, and be accessible to all the operators that source or sink them.

Figure 3: (a) A valid choice of opcodes. (b) An invalid choice of opcodes since vr1 cannot be assigned to either register file I0 or I1 and be accessible to both OP1 and OP3. (c) The insertion of a copy operator to make the choice of opcodes valid once again.

Unfortunately, there is a new problem with this solution. All of the scheduling algorithms mentioned above perform analyses, of one sort or other, on the computation graph prior to scheduling it. Common examples are the annotation of vertices in the computation graph with the length of the longest path to a terminal vertex in the graph or, in the case of loops, the identification of the critical recurrence cycles or the number of operations of each type (according to some pre-specified grouping) [29, 28, 31]. The scheduling heuristics are guided by the results of these analyses, which would be invalidated if the computation graph is modified. Each time such a copy operator is inserted, the analyses and scheduling would have to be repeated—a level of inefficiency that is hard to tolerate.

If these scheduling algorithms are to be used, then in the interests of efficiency, it is important for the scheduler to avoid changing the computation graph during scheduling by inserting or deleting operators, or by altering the structure of the computation graph. In other words, it is inappropriate to give the scheduler complete freedom in choosing the opcode. Some amount of binding is needed prior to scheduling.

It might well be the case that if best use is to be made of the available FUs, the insertion of a certain number of copy operators is essential to successfully spreading the computation

out over the entire machine. Since three of the FUs in our example machine, operate primarily out of register file I0, and the other three out of I1, the computation should be partitioned so that approximately half of the IADDs and IMULs execute on each trio of FUs. Whenever there is a flow dependence between these two partitions, IMOV operators are needed to copy the result from one register file to the other. Obtaining a good schedule demands that we do this. However, efficiency demands that the copy operators be inserted, once and for all, into the computation graph prior to scheduling, and with no further copy insertion thereafter. This leads to an additional step, *partitioning*, which precedes scheduling, decides how best to spread the computation over the available FUs, and inserts the appropriate copy operators.

An EPIC compiler typically contains a number of optimization and transformation steps that modify the computation graph. Most of these occur before partitioning. This includes a long list of traditional optimizations as well as ILP-related optimizations such as tail duplication, loop unrolling, expression re-association and critical path length reduction [30, 32, 33]. Others, most notably spill code insertion, occur after scheduling and register allocation but before post-pass scheduling (see Section 4). Our position is only that the modification of the computation graph not occur during scheduling. Scheduling is already the most time-consuming phase, and this would make it much worse. No product compiler for a significantly parallel ILP processor does this, as far as we are aware. However, if compile-time is not an issue (a luxury that we have never faced) one could entertain modifying the computation graph during scheduling.

## 3.2 A property of correctly generated code

If the code that results from code generation is correct, it must satisfy a number of properties. There is one property that is particularly germane to our discussion. Assume that specific opcodes and registers have been selected for the operators and variables, respectively, in the computation graph. Then, for all the operators that either source or sink a particular variable, their selected opcodes must all have access to the register that has been selected for that variable. If not, the "connectedness" of the computation graph has been violated. We shall formalize this property shortly, but we first need to define a few terms.

**Definitions:** The *expanded computation graph*, corresponding to a computation graph, is a directed, bipartite graph in which for each vertex in the computation graph, there is a corresponding set of vertices in the expanded computation graph. Each such vertex set represents the generic opcode set or the generic register set

corresponding to an operator vertex or a variable vertex, respectively, in the computation graph. Two generic sets are *adjacent* in the expanded computation graph if the corresponding vertices in the computation graph are connected by an edge. Every pair of adjacent generic sets in the expanded computation graph has a set of edges between them, one edge between each opcode and each of the registers that it can access as a particular operand. The direction of the edge is the same as that between the corresponding vertices in the computation graph.

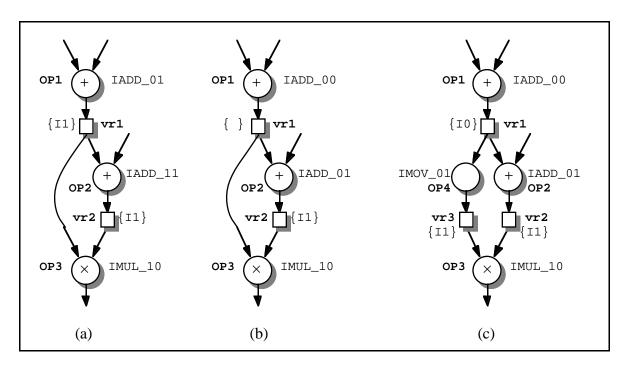

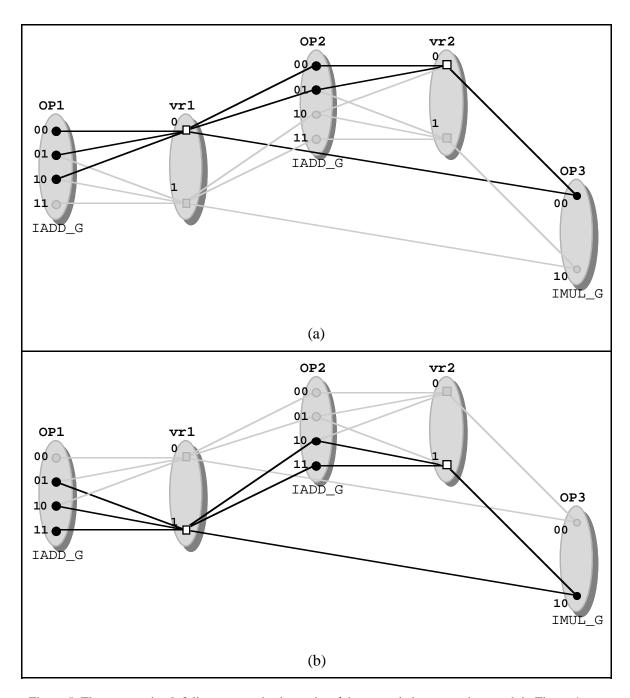

Figure 4: The expanded computation graph for the computation graph in Figure 2, considering only two of the variables, vr1 and vr2. The four opcodes corresponding to an IADD\_G are IADD\_00, IADD\_01, IADD\_10 and IADD\_11, the two opcodes for IMUL\_G are IMUL\_00 and IMUL\_10, and the two sets of registers for the variables are I0 and I1 (in each case, reading from top to bottom).

The space of all correct binding decisions is best illustrated using an expanded computation graph. For each operator or variable in Figure 2, Figure 4 contains its generic opcode set or generic register set, respectively. Each such set is represented by a gray ellipse containing black circles (opcodes) or hollow squares (registers). The flow of data along the edges is from left to right. For the sake of convenience, we take two liberties in Figure 4. First, as in Figure 3, we ignore all but two of the variables (vr1 and vr2). Second, in the two generic register sets, we lump together all of the registers which are part of the same register file and represent them by a single hollow rectangle. An edge to a register file is to be viewed as graphical shorthand for an edge to every register in that register file. For each

opcode in the expanded computation graph, the set of registers that it can access, and to which it has an edge is specified by Table 1.

The code generator's task is to select exactly one opcode or register from each generic set. Correctness requires that the following property exist after code generation has taken place.

**Connectedness property:** For every opcode option selected by the code generator, all of the selected register options in the adjacent generic register sets must each be connected by an edge to the opcode option, and they must jointly constitute a valid register tuple for that opcode.

For the tiny example in Figure 2, one could exhaustively enumerate all of the correct bindings for the three operators and the two variables by analyzing Figure 4. Every one of these would represent code that possesses the connectedness property.

Table 2: The set of correct bindings for the code fragment in Figure 2, obtained by analyzing Figure 4.

| OP1     | vr1 | OP2     | vr2 | OP3     |

|---------|-----|---------|-----|---------|

| IADD_00 | IO  | IADD_00 | IO  | IMUL_00 |

| IADD_01 | 10  | IADD_00 | IO  | IMUL_00 |

| IADD_10 | 10  | IADD_00 | IO  | IMUL_00 |

| IADD_00 | 10  | IADD_01 | IO  | IMUL_00 |

| IADD_01 | 10  | IADD_01 | IO  | IMUL_00 |

| IADD_10 | 10  | IADD_01 | IO  | IMUL_00 |

| IADD_01 | I1  | IADD_10 | I1  | IMUL_10 |

| IADD_10 | I1  | IADD_10 | I1  | IMUL_10 |

| IADD_11 | I1  | IADD_10 | I1  | IMUL_10 |

| IADD_01 | I1  | IADD_11 | I1  | IMUL_10 |

| IADD_10 | I1  | IADD_11 | I1  | IMUL_10 |

| IADD_11 | I1  | IADD_11 | I1  | IMUL_10 |

## 3.3 Constraining the scheduler's and register allocator's options

As the example in Figure 3b demonstrates, one cannot arbitrarily choose the opcode or register for an operator or variable, respectively, from their respective generic sets without running the risk of getting incorrect code. We need to constrain the choice of opcodes that

are available to the scheduler for each operator and the choice of registers that are available to the register allocator for each variable so that the resulting bindings will always possess the connectedness property. We refer to these constrained sets of choices as option sets, and define them as follows.

**Definition:** An *opcode option set* is a subset of the generic opcode set associated with an operator in a computation graph, with the intent that the opcode selected for this operator be a member of this subset.

**Definition:** A *register option set* is a subset of the generic register set associated with a variable in a computation graph, with the intent that the register selected for this variable be a member of this subset.

We wish to assign option sets to the operators and variables of a computation graph, prior to scheduling and register allocation, in such a way that the resulting code possesses the connectedness property

- regardless of which opcode the scheduler independently selects for each operator from its opcode option set,

- regardless of which register the register allocator independently selects for each variable from its register option set, and

- without the insertion of any copy operators during or after scheduling and register allocation,

- while keeping the option sets as large as possible.

Thus we preserve the efficiency of the scheduler and register allocator while retaining as much flexibility as possible for the two of them. With respect to our example code fragment, we would like to start off with the largest number of options for each operator and variable such that regardless of which option is independently selected for each one, the result would be one of the correct bindings listed in Table 2.

The ability to independently choose the option for each operator and variable and yet be certain that the resulting code will possess the connectedness property requires that the option sets associated with the vertices of the computation graph possess the following property.

**Full-connectedness property:** For every pair of adjacent vertices in the computation graph, the corresponding pair of option sets must be fully connected in

the expanded computation graph, i.e., every option in one option set is connected to every option in the other option set. Furthermore, for every opcode in an opcode option set, every register tuple in the Cartesian product of the adjacent register option sets must be legal for that opcode.

Figure 5: The two maximal, fully-connected sub-graphs of the expanded computation graph in Figure 4.

If this is the case, then regardless of which option is selected out of each option set, the resulting code will necessarily possess the connectedness property. The desire to maximize the number of options available to the scheduler and register allocator means that we want these fully connected option sets to be maximal, i.e., it should not be possible to add an option to any of the option sets while still maintaining full-connectedness.

Figure 5 displays the two maximal, fully-connected sub-graphs of the expanded computation graph in Figure 4. In each case, OP1 has three options, OP2 has two options, and OP3, vr1 and vr2 have one option each. Note that adjacent option sets are completely connected and that no option set can be augmented without violating the property of full-connectedness. In this example the edges of the two sub-graphs are disjoint, but this need not necessarily be the case.

The full-connectedness property as stated above can be understood as a specification of the problem of finding all possible, maximal, fully-connected sub-graphs from the expanded computation graph. Each such sub-graph identifies a choice of maximal option sets for all the vertices of the given computation graph. Clearly, the naive algorithm of first listing all possible combinations, as in Table 2, and then collapsing them into maximal sets would be exponential. We do not take any algorithmic or heuristic position on how this is best done.

Table 3: The two 5-tuples of maximal, fully-connected option sets for the vertices of the computation graph in Figure 2.

| OP1                       | vr1  | OP2               | vr2  | OP3       |

|---------------------------|------|-------------------|------|-----------|

| {IADD_00,IADD_01,IADD_10} | {10} | {IADD_00,IADD_01} | {IO} | {IMUL_00} |

| {IADD_01,IADD_10,IADD_11} | {I1} | {IADD_10,IADD_11} | {I1} | {IMUL_10} |

Table 3 lists the two maximal, fully-connected sub-graphs in the form of 5-tuples of maximal option sets. In general, a given correct choice of options could be part of more than one of these tuples of maximal option sets. Also, due to the full connectivity between adjacent option sets, options can be removed from one or more option sets and, as long as no option set becomes empty, the resulting binding is still guaranteed to possess the connectedness property. Thus, for the five vertices in our example computation graph fragment, the two tuples in Table 3 completely specify all possible choices of option sets which jointly possess the full-connectedness property. Naturally, to maximize the degrees

of freedom for the code generator, the preferred choice of option sets is one of the two maximal sets in Table 3. After selecting one of these, scheduling and register allocation can proceed.

Although these are the only 5-tuples of maximal option sets for the computation graph as shown in Figure 2, different tuples are obtained by modifying the computation graph, for instance, by inserting a copy operator as in Figure 3c, and these might well be more attractive. In keeping with our philosophy, this copy insertion must happen before invoking the scheduler. After copy insertion, the maximal option set tuples would have to be computed as described above, followed by scheduling and register allocation.

#### 3.4 Access-equivalent option sets

In practice, the number of operator and variable vertices in the computation graph can be very large. All of these vertices must be decorated with option sets which jointly possess the full-connectedness property. Ideally, these option sets should be maximal as well. For large computation graphs, and when the processor has a rather irregular connectivity between FUs and register files, computing a tuple of maximal option sets is expensive; there can be very many of them, and even defining a local metric for selecting the best one—one that is correlated with eventually getting a good schedule—can be difficult. Although the concept of a tuple of maximal option sets is useful in understanding what we would like to achieve, it has little value as part of a constructive procedure that an EPIC compiler can use. The compiler needs a practical method of constructing a tuple of fully-connected option sets, and the machine description database must contain supporting information that can be computed off-line rather than during code generation.

We do so by focusing on smaller, modular portions of the computation graph. Instead of considering the computation graph as a whole, we consider overlapping sub-graphs, each of which correspond to a single operation: one operator vertex and the variable vertices adjacent to it. Corresponding to each of these sub-graphs is an expanded computation graph, which we term a *generic operation set*, i.e., a generic opcode set for the operator and, for each of its operands, the appropriate generic register set.

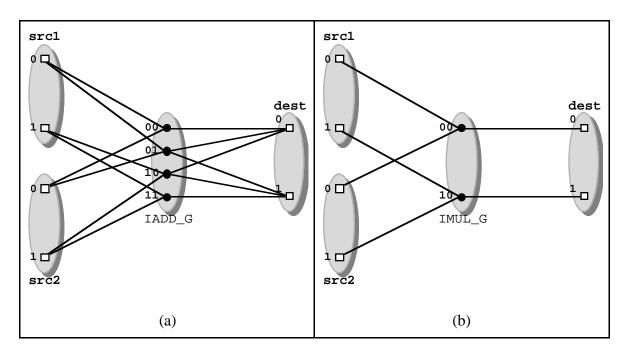

Figure 6 shows the expanded computation graphs for IADD\_G and IMUL\_G. Note that each of these graphs is completely specified by Table 1. Each generic operation set can be analyzed at the time that the mdes is constructed and the set of tuples of maximal option sets

can be constructed for each generic operation set, individually. These are listed in Table 4 for IADD\_G, IMUL\_G and IMOV\_G.

Figure 6: The expanded computation graphs for the (a) the IADD\_G operation and (b) the IMUL\_G operation.

Table 4: Access-equivalent operation sets, i.e., maximal mutually access-equivalent sets of opcode option sets and register option sets. ({I0} and {I1} each represent a set of registers.)

| Semantics | Opcode            | Source 1 | Source 2 | Destination |

|-----------|-------------------|----------|----------|-------------|

| Integer   | {IADD_00,IADD_01} | {IO}     | {10}     | {10}        |

| Add       | {IADD_01}         | {IO}     | {10}     | {I0,I1}     |

|           | {IADD_10}         | {I1}     | {I1}     | {I0,I1}     |

|           | {IADD_10,IADD_11} | {I1}     | {I1}     | {I1}        |

| Integer   | {IMUL_00}         | {IO}     | {10}     | {10}        |

| Multiply  | {IMUL_10}         | {I1}     | {I1}     | {I1}        |

| Сору      | {IMOV_01}         | {10}     | _        | {I0,I1}     |

|           | {IMOV_10}         | {I1}     |          | {I0,I1}     |

Each tuple of maximal option sets is termed an *access-equivalent operation set*. Each one represents a set of legal, completely bound operations. These sets are not necessarily disjoint. Each of the constructed option sets is termed an *access-equivalent opcode set* or an *access-equivalent register set* (as the case may be). For any given access-equivalent operation set, every register in the access-equivalent register set corresponding to a particular operand is equally accessible by any opcode in the access-equivalent opcode set. Conversely, for every opcode in the access-equivalent opcode set, that opcode can access any register in the access-equivalent register set corresponding to a particular operand, and every register tuple in the Cartesian product of these access-equivalent register sets is legal with respect to that opcode. These option sets are mutually access-equivalent. Again, note that one can subset one or more of the options sets in an access-equivalent operation set to any non-empty subset of the maximal set, without loosing the property of mutual access-equivalence.

The same algorithm, that might have been used to derive the fully-connected, maximal subgraphs of the expanded computation graph of a program, can be applied to the expanded computation graphs of each individual generic operation set to yield the access-equivalent operation sets. This problem is substantially easier since each such modular expanded computation graph is much smaller in size and even exponential enumeration and grouping may not be impractical.

The significance of Table 4 is that these access-equivalent operation sets are a property of the machine alone and, unlike Table 3, not of the computation graph as well. They can be computed once and for all from Table 1 while constructing the mdes. Thereafter, for any given computation graph, they can be used to annotate each operator and variable with an access-equivalent option set, using some form of constraint-satisfaction process. The constraint that must be satisfied is that each operation in the computation graph has to be annotated with an access-equivalent operation set in such a way that, for every variable, the intersection of the access-equivalent register sets imposed upon it by all of the operations that access it (i.e., its access-equivalent register option set), must be non-empty. If this constraint is satisfied, the full-connectedness property holds. This annotation and partial binding step is termed the *pre-pass operation binding* phase.

Consider once again the example in Figure 2. OP3 has a choice of two access-equivalent opcode sets, {IMUL\_00} and {IMUL\_10}, each of which contains only a single option. Let us assume that {IMUL\_10} is selected. This restricts the options sets for both vr1 and vr2 to {I1}. This, in turn, restricts the possible option sets for OP2 to be either

{IADD\_10,IADD\_11} or {IADD\_10}. The former is clearly preferable since it contains more options. Since vr1 has the option set {I1}, OP1 can be bound to either {IADD\_10,IADD\_11} or to {IADD\_01}. Perhaps for the purposes of load balancing across the FUs, the partitioning algorithm picks the latter. Now that every vertex in the computation graph has been decorated with an option set, scheduling can be performed and might result in the code shown in Figure 3a.

In general, there are many correct annotations for the computation graph and, for a processor with an arbitrary topology, the task of obtaining a good annotation could still be very complex. Consequently, there is a strong incentive to design processors with a relatively simple structure. Typically, each opcode can only access a single register file, except for copy opcodes that source one register file and sink a different one. Our example processor is not far removed from this design style. For such processors, once the desired copy operators have been inserted by the partitioning algorithm, the process of assigning access-equivalent option sets is trivial. The real problem lies in deciding where to insert copy operators so that the computation is equitably distributed over the FUs of the machine [34, 29, 35, 36].

One way of characterizing traditional DSPs in the context of our framework is that by the time pre-pass operation binding has been performed, the opcode and register option sets have dwindled down to such an extent that there is typically just one option per option set. The scheduling and register allocation that follow are largely trivialized. All the scheduler can do is "compaction", i.e., selecting the time at which each operation is performed within the constraints imposed by the lack of opcode options and the anti- and output dependences introduced by the register binding. Thus, for DSPs, the pre-pass operation binding phase is the crucial one, whereas for the EPIC processor the most important part of code generation is yet to come. It has been consciously designed in such a way as to ensure plenty of options at this stage of binding. Because of the large number of register options for each operand, the scheduler has the luxury of acting as if there is an unlimited number of register options available, with register spill being handled as an exceptional circumstance.

An issue that attracts a lot of attention in the DSP literature is that of making good use of address generators [6, 5]. To our way of thinking, an address generator is an adder, one of whose inputs (the array address) is from the same register file to which it writes its result (which is also sent to the memory as the address for the load or store). The other input (the address increment) is from a different register file. None of this causes any great difficulty with our model of compilation. Nor does it cause any problems with the style of machine

description that we shall propose. What does constitute a problem is that each of these register files typically has just a single register. If not for this, making use of address generation hardware would not constitute any particular problem. In fact, the Cydra 5 mini-supercomputer had what might be viewed as an address generator, except that it was designed in such as way, with an adequate number of registers in the address register file, as to lie within our space of EPIC processors [37].

The access-equivalent operation sets, as defined in this section are applicable across all phase orderings that might be imposed upon the rest of the code generator; they are unbiased with respect to the phase order. For any given phase ordering, the definition of access-equivalent operation sets may change (as we shall see in the next section). But, in every case, the resulting access-equivalent operation sets must, necessarily, be a subset of those defined in this section (since these sets are maximal).

# 4. A model of EPIC code generation

The last section discussed the major challenges of EPIC code generation and argued that, for reasons of efficiency, the code generation process for an EPIC processor must use a phased approach in mapping the source program's operations to the processor's architectural operations. We concluded that a pre-pass operation binding phase, which binds operations to access-equivalent operation sets, was a practical necessity. However, the detailed phase ordering used to accomplish scheduling and register allocation was left unspecified.

For any EPIC processor with even a reasonable amount of parallelism, register allocation is never performed before scheduling. If it were, schedule-unaware register allocation would impose crippling and unnecessary restrictions upon the scheduler in the form of anti- and output dependences caused by using the same register for an unfortunate choice of variables. This leaves one with two choices. Either scheduling can be performed before register allocation, or the two can be performed simultaneously. Each one has its advantages and drawbacks.

In this section, we look at how the incremental binding process and even the definition of an access-equivalent operation set are affected by the specific choice of phase ordering for scheduling and the register allocation. In particular, we consider the example of the phase ordering used by Elcor, our research compiler for EPIC processors. Its phase order is:

- 1. code selection

- 2. pre-pass operation binding (including partitioning, if needed)

- 3. scheduling

- 4. register allocation and spill code insertion

- 5. post-pass scheduling

- 6. code emission

Each phase successively refines and narrows down the options available for either the opcodes, the registers, or both, finally yielding architectural operations that can be executed by the processor. Optimization phases may be inserted at various points in this sequence but, since they do not affect the level of binding, we ignore them. This section introduces a hierarchy of operation refinements between the semantic and architectural layers that forms the basis for organizing the machine description database for the use of the code generator.

Table 5: Access-equivalent operation sets in the context of our phase ordering. ({I0} and {I1} each represent a set of registers.)

| Semantics | Opcode            | Source 1 | Source 2 | Destination |

|-----------|-------------------|----------|----------|-------------|

| Integer   | {IADD_00,IADD_01} | {IO}     | {10}     | {10}        |

| Add       | {IADD_01}         | {10}     | {10}     | {I1}        |

|           | {IADD_10}         | {I1}     | {11}     | {I1}        |

|           | {IADD_10,IADD_11} | {I1}     | {11}     | {I1}        |

| Integer   | {IMUL_00}         | {10}     | {10}     | {10}        |

| Multiply  | {IMUL_10}         | {I1}     | {11}     | {I1}        |

| Сору      | {IMOV_01}         | {10}     | _        | {10}        |

|           | {IMOV_01}         | {10}     | _        | {I1}        |

|           | {IMOV_10}         | {I1}     | _        | {I1}        |

|           | {IMOV_10}         | {I1}     | _        | {10}        |

Our focus, in the rest of this report, is on steps 3 through 5. Each of these steps imposes a pre-condition upon the state of binding that affects our definitions of access-equivalence.

Just prior to register allocation, the scheduler has bound the opcode that is to be used by each operation, as well as when it is scheduled, thereby specifying which functional unit and resources will be used, and when. The operands, however, have only been bound to access-equivalent register sets. It is necessary that the choices made by the register allocator not invalidate the schedule in any manner.

This imposes a new constraint upon the definition of access-equivalent register sets, which tends to shrink them relative to those defined in the previous section. This, in turn, changes the definition of the access-equivalent operation sets that are acceptable just prior to scheduling. Table 5 shows all of the (maximal) access-equivalent operation sets in the context of our phase ordering. The rest of this section explains the reasoning behind this redefinition of access-equivalent operation sets as well as the process of incremental binding that results from our phase ordering. For a different phase ordering, the methodology presented below could be used to derive the corresponding access-equivalent operation sets.

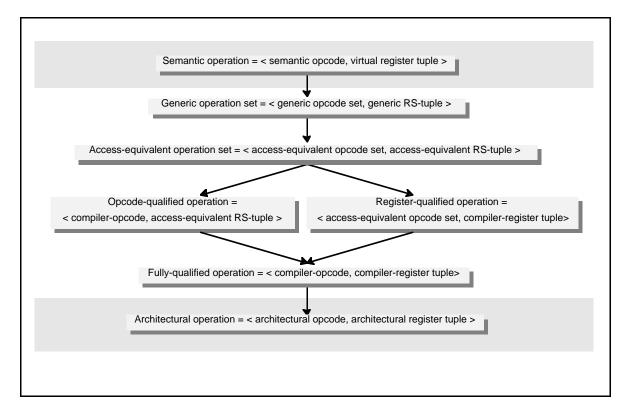

# 4.1 Code generation: semantic operations to architectural operations

Semantic operations and architectural operations form the two end points of the EPIC code generation process. In this section, we describe those properties of these two types of operations that are relevant to our discussion in the subsequent sections.

**Semantic operations.** These are the operations in the input to the code generation process, and they correspond to actions performed by a pre-defined virtual machine. The opcodes at this stage of compilation are the semantic opcodes provided by the pre-defined virtual machine. An operand is either a constant (such as 3 or 4.1) or a *virtual register* (VR). The following two attributes of a VR are relevant to the discussion of the code generation process.

- 1. Data type, *e.g.*, int, long, float, double. The data type determines the number of bits in the container that is needed to store the value.

- 2. Simple VR or an element of an *expanded virtual register* (EVR) [38]. Although EVRs are not part of any language, some of the machine-independent loop-transformations preceding the code generation may introduce them into the code. EVRs either can be mapped to rotating registers [13, 15] or can be converted to simple VRs by code transformation (*e.g.*, loop-unrolling) [39].

**Architectural operations.** These are the operations in the output of the code generation process, and they represent commands performed by the target machine. The opcodes at this stage are architectural opcodes available in the target machine. To simplify the exposition, we treat any addressing modes supported by the target machine as part of the opcode rather than part of an operand. An operand is an *architectural register* which is either a literal or a register in the target machine. For uniformity, we model a literal as the contents of a read-only "literal register". Thus an architectural register is either a real machine register or a literal register. Architectural registers are characterized by the following two types of attributes.

- **Storage attributes:** There are five storage attributes associated with an architectural register.

- The bit width of the register. This is the number of bits in the container.

- The presence or absence of a speculative tag bit. Architectures that support compile-time speculative code motion (control, data or both) provide an additional speculative tag bit in each register that is intended to participate in the speculative execution. This is provided for the correct handling of architecturally-visible exceptions [40, 41, 15].

- Whether this is part of a static or rotating architectural register file. This determines

whether the register specifier used for this register is an absolute register address

or an offset from the rotating register base [15].

- Whether the register is read/write (the normal case), read-only (a literal) or write-only (the proverbial "bit bucket", which is often implemented as GPR 0 in a number of architectures).

- For a read-only register, the value of the literal.

Note that the presence or absence of the speculative tag bit and the static/rotating classification make sense only for "normal" architectural registers and not for literals or the bit bucket.

• Accessibility from opcodes: This consists of the set of architectural opcodes that can use the given architectural register as an operand, and for each opcode, the operand positions in which that register can appear as an operand. This is the same as specifying the connectivity between functional units and register files in a structural description of the target machine.

#### 4.2 The register binding hierarchy

The process of binding generic operations to architectural operations is based on two refinement hierarchies, one for opcodes and one for registers. We describe the additional register layers in this section and do the same for opcodes in the next section.

The three additional layers that an EPIC compiler needs, to translate VRs to architectural registers, are described below. Note that the order in which they appear is not the order in which they are used to successively refine virtual registers.

**Compiler-registers.** A *compiler-register* is either a single architectural register or a set of architectural registers, with a fixed spatial relationship, that are viewed as a single entity by the compiler. Although, in principle, an architecture could view any arbitrary set of registers as a single entity, we believe that such a view is too general and not very useful. Thus all architectural registers that are part of a compiler-register must be identical with respect to all of their characterizing attributes, *i.e.*, storage attributes and the accessibility from opcodes. A compiler-register is characterized by the same types of attributes as is an architectural register. The width of a compiler-register is a function of the width of constituent architectural registers. The other attributes simply carry over.

It is important to note that an architectural register can be part of more than one compiler-register. For example, some architectures view an even-odd pair of single-precision floating-point registers as a double-precision register. In that case, a single-precision architectural register is both a single-precision compiler-register and an element of a double-precision compiler-register.

Compiler-registers also provide a convenient abstraction for compiler and OS conventions such as the procedure calling convention. For example, most phases of the compiler can work with compiler-registers such as the stack pointer, the frame pointer, and parameter passing registers without worrying about the specific architectural registers reserved for these purposes; only the register allocator need be aware of the exact correspondence.

Note that the translation from compiler-registers to architectural registers is primarily a book-keeping step as there are no decisions to be made.

**Generic register sets.** A generic register set is a maximal set of compiler-registers that have the same storage attributes.

Generic register sets provide the first layer in translating operands in the semantic layer, *i.e.*, VRs and constants, to architectural registers. They provide a useful abstraction, since they focus on the properties that are relevant to the abstract computation model and ignore details such as the physical connectivity of the target machine. To map a VR to a generic register set, the data type of a VR is used to select all the generic register sets with the appropriate width. If loop unrolling is precluded, an element of an EVR can be mapped only to those generic register sets that have rotating registers. This restricts the set of candidate generic register sets. A simple VR, on the other hand, can be mapped to any one of the selected generic register sets. The default position is that a VR can map to a register whether or not it has the speculative tag bit (i.e., the VR does not need it). Subsequent code transformations may determine that the VR needs a generic register set with speculative tag bit, which would then restrict the candidate generic register sets further. If at the end of this process there are multiple candidate generic register sets, the VR can be mapped to any one of them using an appropriate heuristic. Constants are mapped to generic register sets corresponding to the literals provided by the target machine.

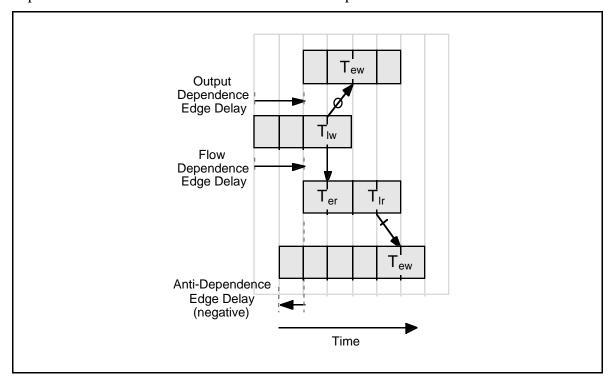

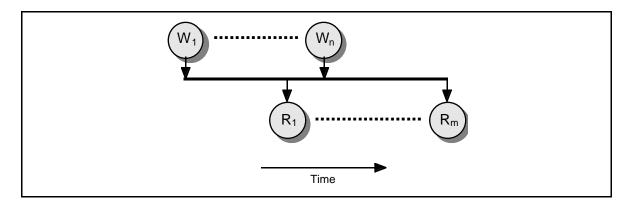

Access-equivalent register sets. In order to help us redefine an access-equivalent register set, we first define a few other terms. An *alternative* is a triple consisting of a compiler-opcode (as defined in Section 4.3), a latency descriptor and a reservation table<sup>7</sup>, that are jointly valid for the target processor. A *register set tuple* (*RS-tuple*) is a tuple of register sets, such that each register set is a subset of a single generic register set (*i.e.*, all the registers have the same storage attributes). An *access-equivalent RS-tuple* corresponding to a given alternative is a maximal RS-tuple, where each register set corresponds to one of the operands of the compiler-opcode, and every register tuple in the Cartesian product of the register sets is jointly valid with that alternative, taking into account both the connectivity constraints of the processor as well as the instruction format constraints. Each register set in an access-equivalent *RS*-tuple is an *access-equivalent register set*.

For every choice of register tuple in the access-equivalent RS-tuple, along with the compiler-opcode of the alternative, the resulting operation has the same latency descriptor and the same reservation table, since all the register tuples are accessible with the same

<sup>&</sup>lt;sup>7</sup> Latency descriptors and reservation tables are discussed in Section 5. For now, it suffices to say that a latency descriptor provides all the information needed by the scheduler regarding an operation's latencies, and a reservation table describes its resource usage over time.

alternative<sup>8</sup>. Consequently, each access-equivalent register set contains registers that are interchangeable with respect to that opcode after scheduling has taken place; any register can be used in place of any other without any impact on the correctness of a scheduled piece of code. Furthermore, since all the register tuples implied by an access-equivalent RS-tuple are architecturally valid, the compiler-register for each operand can be independently selected by the register allocator.

Purely to help in explaining this definition of access-equivalent register sets, we outline the following conceptual procedure to find all of them. (This is not necessarily a practical approach.) We first consider the set of all legal compiler-register tuples, L, for a given alternative. Next, we find all maximal compiler-register set tuples, T, such that each of the compiler-register sets in T is a subset of a single generic register set, and such that the set of register tuples that results from forming the Cartesian product of the compiler-register sets in T, is a subset of L<sup>9</sup>. Each T is an access-equivalent RS-tuple, and each of the compiler-register sets in T is an access-equivalent register set for the given alternative. Finally, we repeat the entire process for every possible alternative in the target processor.

Since all compiler-registers in an access-equivalent set have identical storage attributes, we can also associate these attributes with the set itself. The hardware notion of a register file is an example of an access-equivalent register set.

Access-equivalent register sets provide the second layer in translating VRs to architectural registers. The refinement of an access-equivalent set to a particular compiler-register in the set is done during the register allocation phase.

We refer back to Table 4 to see how our phase ordering affects the definition of access-equivalent register sets for our example processor. Consider the second access-equivalent operation set for integer add. Different resources (register write ports) are used depending

registers in the register file constitute an access-equivalent register set with respect to both opcodes. Nevertheless, ADD1 uses different resources when accessing this access-equivalent register set than does ADD2.

<sup>&</sup>lt;sup>8</sup> Note that in the event that a particular RS-tuple happens to be the access-equivalent RS-tuple with respect to two compiler-opcodes, the two compiler-opcodes can have different latencies or resource usage when accessing this access-equivalent RS-tuples. For example, assume there are two functional units FU1 and FU2, which can each perform an add using opcodes ADD1 and ADD2, respectively, using the same register file. Assume that FU1 uses a different set of shared buses to access the register file than does FU2. Now, ADD1 and ADD2 both have the property that the choice of register that they access does not affect the resources (buses) used. Therefore, the

<sup>&</sup>lt;sup>9</sup> Clearly, the Cartesian product cannot be allowed to be a superset of L, since this would mean that we are admitting spurious, illegal register tuples. If the Cartesian product is equal to L, then a single access-equivalent RS-tuple suffices to specify L. On the other hand, assume that every Cartesian product, which is not a superset of L, is a proper subset of L. Since, by definition, each of the register sets that form the Cartesian products is maximal, we shall need multiple access-equivalent RS-tuples to cover L.

on whether the destination is I0 or I1. So, this corresponds to two different reservation tables and two distinct alternatives. Consequently, the access-equivalent RS-tuple has to be split into two. The first one is identical to that for the first access-equivalent operation set in Table 4. (The resulting access-equivalent operation set is subsumed by the first one, which has a larger opcode set.) The second one is <{I0}, {I0}, {I1}>. Thus {I0, I1} is no longer an access-equivalent register set. The access-equivalent RS-tuples and register sets, in the context of our phase ordering, are shown in Table 5.

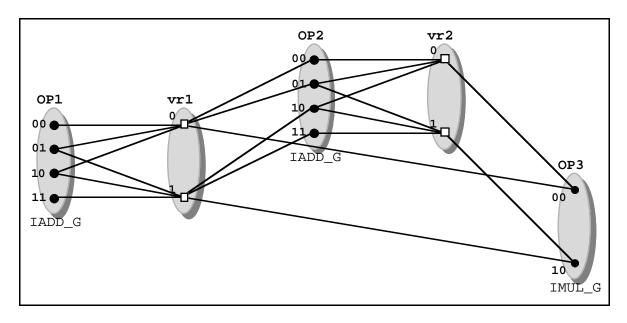

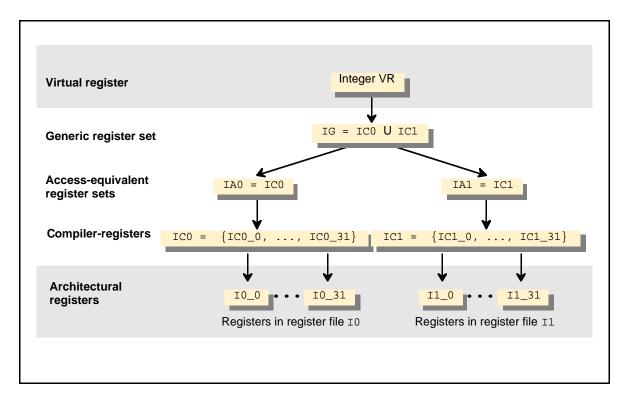

Figure 7: The register binding hierarchy for the integer registers in the example machine introduced in Section 2. Virtual register and architectural register (shown shaded) are not part of the binding hierarchy. They are included to show implementation relations; that is, virtual registers are implemented using generic register sets, and compiler-registers are implemented using architectural registers.

Figure 7 shows the binding hierarchy for integer registers in the context of our phase ordering. At the lowest level are architectural registers in the two register files I0 and I1; at the highest level is a VR with integer data type. These two levels are not part of the refinement hierarchy; they are used to show "implementation relationships". Architectural registers are used to implement compiler-registers, and in this case, they have a one-to-one relationship with compiler-registers. Since all these compiler-registers have the same

storage attributes, they are grouped into one generic register set denoted by IG in the figure. This example shows a trivial implementation relation between the integer VR and the generic register set, but that need not always be the case. As shown in Table 5, with our refined definitions of access-equivalent register sets, there are now only two distinct architectural register sets, I0 and I1, that are accessed by various alternatives corresponding to the integer add, multiply and move opcodes. The architectural register sets, I0 and I1, expressed in terms of compiler-registers form the two access-equivalent register sets, IA0 and IA1, respectively.

#### 4.3 The opcode binding hierarchy

The binding process for opcodes parallels that for registers. The three additional opcode layers that an EPIC compiler needs are described below. As in the case of registers, the order in which they appear is not the order in which they are used to successively refine semantic opcodes.

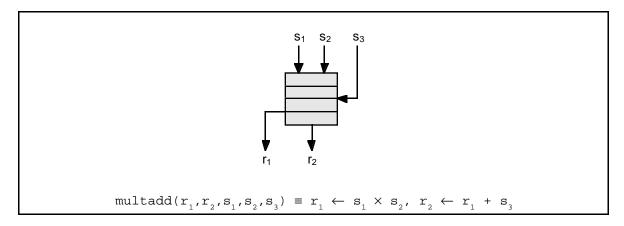

Compiler-opcodes. In some cases, architectural opcodes don't provide the right abstraction that the compiler, especially the scheduler, needs. As a consequence, either the scheduler has less freedom during scheduling, or it has to use a complex scheduling algorithm. Consider, for example, a target machine that doesn't provide an explicit register-to-register copy and in which the copying of a register is done, instead, by either adding 0 or multiplying by 1. We must be able to describe that a copy operation can be implemented in one of these two ways so that the scheduler is free to choose either one based on the availability of resources. In addition, compiler algorithms, such as copy-propagation, would prefer to deal with the abstract notion of a register-to-register copy rather than all possible ways in which it can be coded for the target machine. Thus, we need a capability to describe versions of architectural opcodes in which some of the operands have been prebound to literals.

Another example is a compiler-opcode whose semantics specify a 64-bit add on a machine that only has 16-bit adds. The 64-bit add can be implemented as four 16-bit adds with the carry-out of one add feeding the carry-in of the next. Since there is only a single carry bit per adder, the four 16-bit adds must be constrained to execute on the same adder in successive cycles (assuming a single cycle add latency).

As a final example, consider a target machine which provides register-to-register add and multiply operations. In addition, suppose that it provides a fast way of doing a multiply-

add by "chaining" the two units, without going through a register, provided that the add is scheduled in the cycle after the multiply. Such constraints, which are necessary to handle transient data, increase the complexity of the scheduling algorithm and are one of the reasons why it is hard to schedule for DSPs. However, if such constraints are rare, a simple way to handle them is to represent the two operations, with a fixed relative schedule, by one multiply-add compiler-opcode.

Thus, we introduce an abstraction over architectural opcodes, called compiler-opcodes. A compiler-opcode is implemented by one or more architectural opcodes as specified by a *bundle-macro*, which is described in detail in Section 5.2. As with registers, the translation from compiler-opcodes to architectural opcodes is essentially a book-keeping step; there are no decisions to be made. The compiler intermediate representation with compiler-opcodes is translated to architectural opcodes using the associated bundle-macro definition. This step constitutes a form of delayed code selection.

**Generic opcode sets.** A generic opcode set is the maximal set of compiler-opcodes that implement the same function, *e.g.*, integer add. In other words, the compiler-opcodes in such a set are interchangeable as far as their semantics are concerned, and the function being implemented can be materialized using any one of the compiler-opcodes.

These sets provide the first layer in translating semantic opcodes to architectural opcodes and provide a useful abstraction. During the code selection phase, they focus on the semantics of the operations available on the target machine and hide details such as the connectivity of functional units to register files.

Access-equivalent opcode sets. These sets are defined using the notion of access-equivalent register sets introduced in the last section. An access-equivalent opcode set is the maximal set of compiler-opcodes that are part of the same generic opcode set (*i.e.*, implement the same function) and for each of which there is an alternative that yields the same access-equivalent RS-tuple. Note that this definition permits each compiler-opcode to access the access-equivalent RS-tuple with a different latency descriptor or reservation table, but it does require that the RS-tuple be equally accessible by every compiler-opcode in the set. Therefore, these compiler-opcodes can be interchanged without having to insert or delete any copy operations.

Conceptually, to find all access-equivalent opcode sets, we consider all possible access-equivalent RS-tuples for the target processor that were discovered during the process of identifying the access-equivalent register sets. Each RS-tuple has one or more alternatives

with respect to which it is an access-equivalent RS-tuple, and each such alternative has an associated compiler-opcode. We partition these compiler-opcodes, grouping together those that are a subset of the same generic opcode set. Each of these partitions constitutes an access-equivalent opcode set.

Access-equivalent register sets, RS-tuples and opcode sets, as defined in this and the previous sections, provide maximal freedom to the scheduler while satisfying both requirements: that the computation graph need not change during scheduling, and that the choices available to the register allocator after scheduling are schedule-neutral and can be made considering each operand individually.

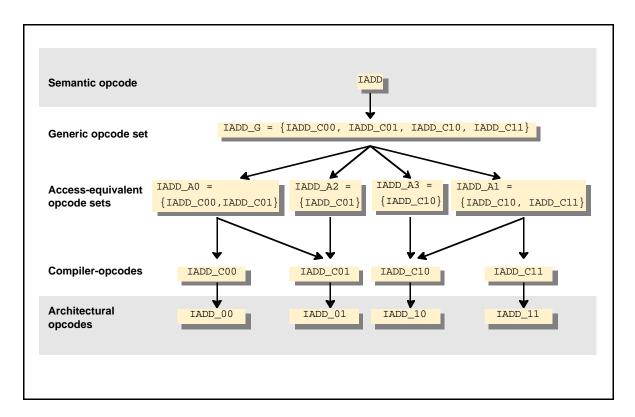

Figure 8: The opcode binding hierarchy for integer add operations in the example machine introduced in Section 2. Semantic opcode and architectural opcode (shown shaded) are not part of the binding hierarchy. They are included to show implementation relations; that is, semantic opcodes are implemented using generic opcode sets, and compiler-opcodes are implemented using architectural opcodes.

The effect of our phase ordering was to split some of the access-equivalent register sets in Table 4. As pointed out earlier, subsetting one or more access-equivalent register sets of an access-equivalent operation set yields another (non-maximal) access-equivalent operation

set with the same access-equivalent opcode set. Consequently, our phase ordering does not alter the definition of the access-equivalent opcode sets (Table 5).