# CirFix: Automated Hardware Repair and its Real-World Applications

Priscila Santiesteban<sup>(D)</sup>, Yu Huang<sup>(D)</sup>, Westley Weimer<sup>(D)</sup>, and Hammad Ahmad<sup>(D)</sup>

Abstract—This article presents CirFix, a framework for automatically repairing defects in hardware designs implemented in languages like Verilog. We propose a novel fault localization approach based on assignments to wires and registers, and a fitness function tailored to the hardware domain to bridge the gap between software-level automated program repair and hardware descriptions. We also present a benchmark suite of 32 defect scenarios corresponding to a variety of hardware projects. Overall, CirFix produces plausible repairs for 21/32 and correct repairs for 16/32 of the defect scenarios. Additionally, we evaluate CirFix's fault localization independently through a human study (n = 41), and find that the approach may be a beneficial debugging aid for complex multi-line hardware defects.

*Index Terms*—Circuit designs, automated repair, empirical study, user study.

# I. INTRODUCTION

**R** ECENT increases in the complexity of hardware designs have challenged the ability of developers to find and repair defects in circuit descriptions [1]. While significant effort has been devoted to efficiently verifying functional correctness in hardware design descriptions, relatively little work has been done in patching defects in such descriptions automatically. By and large, debugging and repairing hardware designs remains a very expensive and time-consuming task [2]. Indeed, recent functional and security vulnerabilities due to defects at the hardware design level have led to expensive consequences [3], [4], [5]. To reduce the cost and improve the maintenance of hardware designs, a solution needs to not only precisely identify sources of defects in real-world off-the-shelf hardware descriptions, but also automatically produce repairs implementing correct functionality of the circuit designs that can then be shown to developers for validation before moving on to the synthesis phase.

Manuscript received 5 August 2022; revised 1 April 2023; accepted 6 April 2023. Date of publication 25 April 2023; date of current version 18 July 2023. This work was partially supported in part by the NSF under Grant 1908633 and in part by AFRL under Grant 2211749. Recommended for acceptance by M. Pradel. (*Corresponding author: Priscila Santiesteban.*)

This work involved human subjects or animals in its research. Approval of all ethical and experimental procedures and protocols was granted by the University of Michigan Health Sciences and Behavioral Institutional Review Boards under Application No. HUM00199335.

Priscila Santiesteban, Westley Weimer, and Hammad Ahmad are with the Computer Science and Engineering, University of Michigan, Ann Arbor, MI 48104 USA (e-mail: pasanti@umich.edu; weimerw@umich.edu; hammada@umich.edu).

Yu Huang is with the Computer Science, Vanderbilt University, Nashville, TN 37235 USA (e-mail: yu.huang@vanderbilt.edu).

Digital Object Identifier 10.1109/TSE.2023.3269899

Additionally, we desire a solution that applies directly to both the behavioral aspects (i.e., higher-level descriptions of circuit functionality) and the register-transfer level (RTL) aspects (i.e., lower-level descriptions) of circuit designs, and makes use of readily-available resources that are part of hardware design to validate proposed repairs.

Previous work has attempted to address this problem but may not satisfy all of these characteristics of a desired solution. For instance, some techniques automatically localize defects in design source code but suffer from high false positive rates [6], [7].

Other approaches for automatic error diagnosis and correction require formal specifications to conduct design verification [8], which usually do not scale to large designs.

Furthermore, previous work does not operate on behaviorallevel descriptions of hardware circuits [9], [10]. On the other hand, in the realm of software, significant research effort focuses on repairing bugs automatically [11], [12], [13]. *Automated program repair* (APR) algorithms fix defects in software by producing patches that pass all test cases while retaining required functionality. Traditional APR for software employs *fault localization* techniques to implicate faulty code, and such techniques are often crucial to the success of program repair. Interest in applying software APR methods to hardware has been seen in the literature. Some methods for localizing hardware errors focus on applying a model-based diagnosis paradigm and making use of structure and behavior for software debugging [14], [15], [16], [17].

While both software programs and hardware description languages (HDLs) share programming concepts like expressions, statements, and control structures, suggesting the possibility of repurposing software repair techniques to hardware designs, we highlight two key differences between the two domains: (1) HDL designs are inherently parallel and often include non-sequential statements, since separate portions of hardware can operate simultaneously. While some conventional languages, such as Javascript, have support for parallelism, APR typically focuses on software written in languages such as C and Java that are generally based around a serial execution model. (2) Software programs usually use test cases to evaluate functional correctness, where individual test cases may pass or fail depending on the quality of the software. HDL designs, on the other hand, use *testbenches* [18], which are programs with documented and repeatable sets of stimuli, to simulate behaviors of a device under test (DUT). In both academia and industry, the majority of digital hardware design is done using such HDLs.

0098-5589 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

3736

We present two key insights to bridge the gap between software repair techniques and hardware designs. We first hypothesize that while traditional spectrum-based fault localization approaches do not apply to hardware designs that feature a more parallel structure [19], dataflow-based fault localization (e.g., [20]) approaches work well in this domain. Second, we hypothesize that a traditional hardware testbench can be instrumented to admit observations for candidate patches that guide the search for APR.

Leveraging these insights, we present CirFix, a framework for automatically repairing defects in hardware designs implemented in languages like Verilog, one of the most popular HDLs [21]. CirFix uses genetic programming (GP), an iterative stochastic search technique, to find candidate repairs for defects in hardware designs. CirFix also makes use of readily-available artifacts in the hardware design process (e.g., testbenches, simulation environments) to diagnose and repair defects in a circuit description. We propose an approach to guide the search for a repair by instrumenting hardware testbenches to record the values of output wires at specified time intervals during a simulation of the circuit design. Our novel fault localization utilizes the simulations to assign blame to incorrect wires and registers.<sup>1</sup> CirFix then performs a bit-level comparison of output wires against information for expected behavior to assess functional correctness of candidate repairs. CirFix employs a fixed point analysis of assignments made to internal registers and output wires to implicate statements and reduce the search space, enabling our approach to scale to large circuit designs in industry.

We present a benchmark suite of 32 *defect scenarios* [22] based on three hardware experts — two from industry and one from academia — asked to transplant bugs they observed in real life into 11 different Verilog projects. CirFix can produce plausible repairs for 21 out of the 32 Verilog defect scenarios within reasonable resource bounds, of which 16 are deemed correct upon manual inspection.

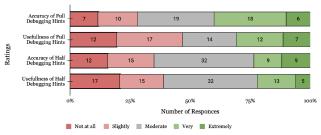

Furthermore, we evaluate the usability of our novel fault localization algorithm independent of the automated repair context through a human study in which n = 41 humans assess its quality and usefulness. We find a statistically-significant preference (p = 0.003) for CirFix fault localization as a debugging aid in fixing multi-line hardware defects, primarily in student applications (p = 0.01).

The main contributions of this paper are:

- CirFix, a repair algorithm for hardware designs.

- A novel dataflow-based fault localization approach for HDL descriptions to implicate faulty design code.

- A novel approach to guide the search for a hardware design repair that is compatible with the testbench-based hardware testing process.

- A new benchmark suite of 32 scenarios, based on proprietary bugs but available in 11 open projects.

- A systematic evaluation of CirFix on our benchmark suite. CirFix was able to correctly repair 16 out of the 32 Verilog defects under consideration.

<sup>1</sup>In HDLs like Verilog, wire elements are used to connect input and output ports of a module instantiation, while registers stores values.

• A human study using CirFix's fault localization algorithm as a debugging aid on real-world and student applications. We observe statistically significant preference using the support for multi-line defects (p = .003) in student applications (p = 0.01).

Additions Relative to Prior Paper: This article extends our ASPLOS 2022 paper [23], but also includes (1) a new human study of the proposed fault localization algorithm for hardware designs, (2) an independent assessment of correctness of the produced CirFix patches from an expert team [24], [25], [26], [27], [28], (3) an investigation of fault localization sensitivity and, (4) a discussion of the degree to which CirFix interacts with the synthesizability or timing of a design. In Section IV-C we introduce a human study to investigate the incremental benefit of our fault localization in various Verilog debugging scenarios. In Section V-A we report an assessment of CirFix patches along an orthogonal evaluation criterion from an independent expert APR team. In Section VI we analyze the results in terms of objective performance and subjective judgements. In Section V-A, we evaluate CirFix's repair performance by conducting a targeted experiment that controls the quality of initially-provided information. Lastly, we discuss synthesizability and timing of repairs in Section VII.

### II. MOTIVATING EXAMPLE

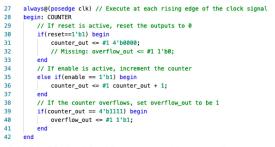

In this section, we use an example defect from a faulty 4-bit counter with an overflow bit, implemented in Verilog, to motivate the fault localization and candidate evaluation approaches used by CirFix. The main block of the source code is shown in Fig. 1(a), with the corresponding testbench in Fig. 1(b). The circuit design uses wires enable and reset to increment (lines 35–37) and reset (lines 30–33) the counter respectively. Incrementing the counter when it has a binary value of 4 ' b1111 results in the overflow bit being set to true (lines 39–41). This implementation incorrectly manages the overflow bit: the if-statement at line 30 is missing an assignment that resets overflow\_out. Such defects can have serious consequences — integer overflow errors can be leveraged into significant security exploits [29].

For the purposes of this work, there are two key hardware design concepts that we highlight for a general audience: circuit synchronization and parallelism.

*Circuit Synchronization:* The main block of the circuit design code shows an *always* block (line 27, Fig. 1(a)) that executes repeatedly until the simulation stops. The execution of such blocks can only be triggered by changes to wires in the *sensitivity list* that follows the always keyword. Nearly every digital circuit design includes a *clock signal* (line 50, Fig. 1(b)) that oscillates between a high and a low state (denoted by events posedge and negedge respectively); circuits rely on clock signals to know when and/or how to execute their programmed actions. A *clock cycle* is the period of time it takes for the clock signal to oscillate from high to low and back to a high state. For the 4-bit counter in Fig. 1(a), the wire clk (denoting the clock signal) is the only wire in the always block's sensitivity list (see line 27), and lines 28–42 are executed every time that wire reaches a

(a) Main block of the 4-bit counter with an overflow error

always #5 clk = !clk; // Set clock signal oscillations 51 initial begin // Execute this block once 52 53 #5 // Wait for 5 time units 54 forever begin // Execute this block indefinitely until simulation stops 55 @(reset\_trigger); // Wait for the reset\_trigger event 56 @(negedge clk); 57 reset = 1; // Set reset to 1 on the next falling edge of the clock 58 @(negedge clk); 59 60 reset = 0; // Set reset to 0 on the next falling edge of the clock -> reset done trigger; // Send the reset done trigger event signal 61 62 end 63 64 initial begin 65 #10 -> reset trigger; // Send the reset trigger event signal after 10 time units @(reset\_done\_trigger); // Wait for the reset\_done\_trigger event 67 @(negedge clk); // Wait for falling edge of the clock signal 68 enable = 1; // Enable the counter repeat (21) begin // Wait for 21 more falling edges of the clock signal 69 70 @(negedge clk); end 71 72 enable = 0: // Disable counter #5 -> terminate\_sim; // Terminate simulation after 5 time units 73 74 end

(b) Main testing logic from the 4-bit counter testbench

Fig. 1. A 4-bit counter with an overflow error in Verilog.

high state. Note that there also exists a notion of asynchronous designs where the state of the system can change in response to changing inputs. However, given the increased complexity associated with asynchronous designs, most hardware designs tend to be synchronous in nature [30].

Parallelism: A key property of HDL designs not immediately apparent in Fig. 1 is that parts of the design code typically execute in parallel. When a design is realized into actual hardware, individual components run all the time. Indeed, every statement in a Verilog design not inside an explicit sequential block of code exhibits concurrency. For instance, for the 4-bit counter in Fig. 1(a), an implementation managing the overflow bit correctly would include two assignments to counter\_out and overflow\_out (on lines 31 and 32 respectively) that happen at the same time when reset is true.

To automatically repair the design code in Fig. 1(a), CirFix needs to first answer, for the original design and each candidate repair: *what part of the circuit, if any, is behaving incorrectly?* Unfortunately, standard spectrum-based fault localization tools commonly used by APR for software do not work for HDL designs that exhibit parallelism. To overcome this challenge, we propose a novel fault localization approach based on assignments to wires and registers. We first instrument the existing testbench to record output values at given time intervals. This instrumented testbench, when used to simulate the design, reports the output values from the circuit, which can be compared against expected output. Any mismatch between expected and actual output serves as the starting point for our fault localization. For the 4-bit counter in Fig. 1, the testbench waits for 10 units

of time before sending the reset signal (line 65, Fig. 1(b) cf. stimuli for unit tests in software). The procedural block within the testbench that was waiting on the reset signal (line 55, Fig. 1(b)) then sets reset to true upon the next falling edge of the clock signal. This causes any subsequent executions of the if-statement that resets the wires (line 30, Fig. 1(a)) to evaluate the true branch, after which the counter is reset. A correct design should also reset the overflow bit: at this point, the expected behavior requires overflow\_out to be 0, while the actual value recorded by our instrumented testbench is x (the Verilog representation an uninitialized or unknown logic value). This causes overflow\_out to be implicated for fault localization, and CirFix focuses repair efforts on assignments to this wire and parts of design code that such assignments transitively depend on (e.g., the conditional in line 39, Fig. 1(a)).

For every candidate repair produced, CirFix needs to also answer: how good (i.e., fit) is the proposed repair at fixing the defect? Unfortunately, evaluation approaches for candidate repairs from software cannot be applied to HDL descriptions that typically use testbenches (see Fig. 1(b)). We address this using a novel fitness evaluation approach. Our instrumented testbench records the values of output wires and registers at every rising edge of the clock during an otherwise standard hardware simulation. For developer-specified time intervals from the design simulation (a clock cycle by default), our fitness function compares each output bit against the expected output: for every bit match, we add to the fitness sum; for every bit mismatch, we subtract from the sum. This fitness sum is then normalized. For the 4-bit counter shown in Fig. 1, the testbench simulates the design code for 26 clock cycles, out of which the first 20 produce an output of x (i.e., uninitialized) for overflow\_out on the original design. This causes an output mismatch for overflow\_out for 17 clock cycles, resulting in a fitness score of 0.58 (see Section III-B for CirFix fitness calculations). A repair managing overflow\_out correctly would match expected behavior, resulting in a fitness of 1.0.

This faulty circuit code was obtained by having a hardware expert from industry adversarially transplant defects from their experience into open circuit descriptions (see Section IV). We use this example to motivate and demonstrate the basic design ideas behind CirFix, an approach that scales well to larger circuit designs, as we will demonstrate.

#### III. TECHNICAL APPROACH

In this section, we present CirFix, an automated repair algorithm for defects in hardware design code. Our prototype implementation of CirFix operates on hardware descriptions written in Verilog, and thus supports HDL programming constructs such as sequential and parallel code, variable reassignment, and synchronized code blocks. Our prototype would require modifications to generalize to other hardware description languages (e.g., adding support for AST parsing or different simulation environments). The pseudocode is shown in Algorithm 1.

CirFix applies our two-pronged HDL-specific approach to implicate faulty design code and assess the correctness of circuit descriptions to produce repairs that can then be shown to

| Algorithm 1: The High-Level CirFix Pseudocode.                        | Algorithm 2: High-Level Algorithm for Fault Localization                             |  |  |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| <b>Input:</b> Circuit design to be repaired, C.                       | for HDL Based on a Fixed Point Analysis of Assignments.                              |  |  |

| <b>Input:</b> Instrumented testbench for circuit, $TB$ .              | Input: Faulty circuit design code AST, ast.                                          |  |  |

| Input: Expected output for circuit behavior, O.                       | Input: Simulation output,                                                            |  |  |

| <b>Input:</b> Fitness function, <i>f</i> .                            | $S: Time \to Var \to \{0, 1, x, z\}.$                                                |  |  |

| Input: Parameters, popSize, maxGens, rtThreshold,                     | <b>Input:</b> Expected output, $O: Time \rightarrow Var \rightarrow \{0, 1, x, z\}.$ |  |  |

| mutThreshold.                                                         | <b>Output:</b> Fault localization set, <i>FL</i> .                                   |  |  |

| Output: Repaired circuit description.                                 | $1: FL, mismatch \leftarrow \emptyset, \emptyset$                                    |  |  |

| $1: pop \leftarrow seed\_pop(C, popSize)$                             | $2: mismatch' \gets get\_output\_mismatch(O,S)$                                      |  |  |

| 2: repeat                                                             | ⊳Section III-B                                                                       |  |  |

| 3: $childPop \leftarrow \emptyset$                                    | 3: while $mismatch \neq mismatch'$ do                                                |  |  |

| 4: while $ childPop  \leq popSize$ and $\forall candidate \in$        | 4: $mismatch \leftarrow mismatch \cup mismatch'$                                     |  |  |

| $childPop. \ f(candidate, TB, O) < 1.0 \ {\rm do}$                    | 5: <b>for</b> node in ast <b>do</b>                                                  |  |  |

| 5: $parent \leftarrow tournament\_selection(pop, f)$                  | 6: <b>if</b> implicated( <i>node</i> , <i>mismatch</i> ) <b>then</b>                 |  |  |

| 6: $fl\_set \leftarrow fault\_loc(parent)$                            | 7: $FL \leftarrow FL \cup \{node.id\}$                                               |  |  |

| 7: <b>if</b> probability() $\leq rtThreshold$ <b>then</b>             | 8: <b>for</b> each <i>child</i> of <i>node</i> <b>do</b>                             |  |  |

| 8: $child \leftarrow apply_fix_pattern(parent, fl\_set)$              | 9: $FL \leftarrow FL \cup \{child.id\}$                                              |  |  |

| 9: $childPop \leftarrow childPop \cup \{child\}$                      | 10: <b>if</b> $type(child) = Identifier and$                                         |  |  |

| 10: <b>else</b> $\triangleright$ Repair operators                     | $child \notin mismatch$ then                                                         |  |  |

| 11: <b>if</b> probability() $\leq mutThreshold$ <b>then</b>           | 11: $mismatch' \leftarrow mismatch' \cup \{child\}$                                  |  |  |

| 12: $child \leftarrow mutate(parent, fl\_set)$                        | 12: return <i>FL</i>                                                                 |  |  |

| 13: $childPop \leftarrow childPop \cup \{child\}$                     |                                                                                      |  |  |

| 14: <b>else</b>                                                       |                                                                                      |  |  |

| 15: $parent2 \leftarrow tournament\_selection(pop, f)$                |                                                                                      |  |  |

| 16: $\{c1, c2\} \leftarrow crossover(parent, parent2)$                | (lines 12 and 16 in Algorithm 1; see Section III-C) or a repair                      |  |  |

| 17: $childPop \leftarrow childPon \cup \{c1, c2\}$                    | <i>template</i> (line 8 in Algorithm 1; see Section III-C) to a parent               |  |  |

| 18: until resources exhausted or                                      | selected for reproduction. Candidate variants are selected for                       |  |  |

| $\exists \ candidate \in childPop. \ f(candidate, TB, O) = 1.0$       | reproduction based on their <i>fitness</i> scores assigned by the CirFix             |  |  |

| 19: <b>return</b> minimize( <i>candidate</i> , <i>TB</i> , <i>O</i> ) | fitness function (line 5 in Algorithm 1; see Section III-D). Our <i>fix</i>          |  |  |

human developers for review. Our *fault localization* approach simulates a faulty circuit and assigns blame to incorrect wire and register outputs (line 6 in Algorithm 1; see Section III-A). Note that while traditional software-based APR techniques typically compute fault localization once at the start of the search for repairs, we choose to repeatedly re-localize to support multiple dependent edits made to the source code. Our fitness function, tailored to the hardware domain, scores each candidate patch to guide the search for repairs (lines 4 and 18 in Algorithm 1; see Section III-B).

At a high level, CirFix uses genetic programming (GP) [31], an iterative stochastic search technique, to synthesize candidate repairs to faulty HDL programs. The framework takes as input the source code implementing a faulty circuit design, an instrumented testbench used to simulate the circuit for testing and verification purposes, the expected circuit behavior,<sup>2</sup> and the input parameters. The algorithm starts with the original source code and maintains a population of program variants, each stored as a *repair patch* [32] describing a sequence of abstract syntax tree (AST) edits parameterized by unique node numbers. Each program variant is obtained by applying a *repair operator*

parent ted for CirFix (11ne 5 in Algorithm 1; see Section III-D). Our fix *localization* identifies code to be inserted or replaced as part of mutation operations (see Section III-E). The algorithm loops for several generations, each maintaining a population of program variants, until a plausible repair is found that produces output (as observed by the instrumented testbench) matching the expected circuit output, or allowed resources are exhausted (i.e., the algorithm reaches a timeout or a certain number of generations). For the final post processing step, CirFix minimizes [33] a candidate repair to remove extraneous operations not needed to obtain correct circuit output (line 19 in Algorithm 1; see Section III-F). Candidate repairs are not deployed directly but are instead shown to human developers (e.g., during the pair process between an RTL design engineer and a verification engineer [34]) for validation before the design is ultimately synthesized, reducing maintenance costs [35], [36].

# A. Fault Localization

Fault localization is critical to the success and efficiency of APR [37]. Traditional APR for software often relies on spectrum-based fault localization [38] to narrow down defects to certain parts of a faulty program by sampling the program counter. Such fault localization approaches do not extend naturally to the parallel structure of hardware descriptions [19].

To overcome this challenge, we propose a novel dataflowbased fault localization approach to implicate faulty code in HDL descriptions. Previous work analyzing defects in

<sup>&</sup>lt;sup>2</sup>CirFix does not require perfect information for expected behavior for every timestep: the developer can choose to only provide information at certain intervals. See prior work RQ4 [23] for an evaluation of the trade-off between the level of detail of expected output and repair success.

large hardware projects reports that most defects in Verilog descriptions correspond to assignment statements and ifstatements [39]. We present an algorithm that implements an analysis of assignments made to wires and registers in a circuit's design code to implicate faulty statements. Our proposed algorithm transitively captures data and control dependencies in a context-insensitive fixed point analysis. While traditional spectrum-based fault localization approaches for software return a ranked list of implicated statements [40], [41], [42], our approach returns a uniformly-ranked set: due to the parallel structure of HDL designs, a set of implicated assignments that are equally likely to contribute to the design defect suffices.

Algorithm 2 outlines the high-level pseudocode for our fault localization approach. The algorithm takes as input the AST of the faulty circuit design, the output from design simulation, and the expected circuit behavior (see Section III-B for the simulated and expected outputs). It then compares the simulation output against the expected behavior to produce a set of *identifiers* (i.e., variable names) for output wires and registers with mismatched values. Using this mismatch set as a starting point, for every node in the AST, the algorithm checks if the node is implicated by output mismatch.<sup>3</sup> Implication for a node in the AST occurs when

- (Impl-Data): either the node corresponds to an assignment statement and the left child of the node corresponds to an identifier in the mismatch set (cf. data dependency analysis),

- (Impl-Ctrl): or the node corresponds to a conditional statement and an identifier in the conditional statement belongs to the mismatch set (cf. control dependency analysis).

Any implicated node and all of the node's children are added to the fault localization set. Additionally, if any child of an implicated node is itself an identifier not part of the mismatch set, the name of the identifier is added to the mismatch set (Add-Child). For example, for the 4-bit counter introduced in Section II, recall that the overflow\_out wire had incorrect output from the circuit simulation. This causes the wire to be added to the mismatch set. The CirFix fault localization implicates the only assignment to overflow\_out (line 40, Fig. 1(a)) by rule (Impl-Data) in the first iteration of the algorithm. Indeed, the entire if-statement wrapping this assignment (line 39, Fig. 1(a)) becomes implicated by (Impl-Ctrl), bringing in the new identifier counter\_out to the mismatch set by (Add-Child). The process is repeated until no new identifiers are added to the mismatch set.

This novel approach to fault localization for hardware is a good fit for automatically repairing HDL designs: it returns a precise set of implicated AST nodes in a faulty circuit design, is context-insensitive and therefore inexpensive to compute, and applies directly to node types associated with ASTs for languages like Verilog. Note that while we demonstrate the scalabaility of our approach on a variety of hardware designs of different sizes (see Table II), our approach may require additional developer effort to generalize to very complex designs (e.g., a microprocessor) with millions of wires, gates, and registers. We discuss this limitation in Section VIII.

# B. Fitness Evaluation

The *fitness function* evaluates the acceptability of a program variant by assigning a value ranging continuously between 0 and 1 to the variant, with 1 indicating a *plausible* [43] (i.e., testbench-adequate) repair ready to be shown to human developers. Fitness provides a termination criterion for CirFix and guides the search for a repair. As mentioned in Section I, traditional APR for software uses test-case based evaluation strategies to assess candidate repairs. Hardware designs, by contrast, use testbenches to verify functional correctness (see Section I for details on the difference between hardware and software evaluations). We present a novel fitness function tailored to hardware to guide the search for repairs to HDL designs. Our fitness function uses two key insights: *visibility* and *comparison*.

Many traditional hardware testbenches monitor the values of output wires during simulation and assess correctness based on the final output values. For instance, the testbench for the 4-bit counter introduced earlier (Fig. 1(b)) may report that the final value of the counter is 5 and the overflow bit is 1 when the simulation terminates. Some off-the-shelf hardware testbenches, especially those for large projects, may not even report the exact incorrect value, reporting instead merely the presence or absence of an error during simulation. We want our fitness function to assess a candidate repair based on intermediary as well as final output values, and assign fitness values to the repair based on its overall closeness to the correct circuit design [44]. To do so, given a testbench for a faulty HDL description, we instrument the testbench to record the values of output wires and registers for specified time intervals. This instrumentation is easily automatable: every hardware testbench must instantiate a device-under-test (DUT) and connect wires to the module being instantiated (cf. unit tests in software instantiating the object being tested); each module in turn specifies input and output wires, and a static analysis of the instantiation of the DUT can provide the information needed to instrument a testbench automatically.

Once the testbench is instrumented, we simulate the circuit design and compare the results against the expected output to assess functional correctness of the HDL description. We desire a fitness function that assigns high values to candidate repairs that display behavior similar to expected behavior. To do so, we need to determine the relative contribution of each bit to the fitness of a proposed repair. Given a set of time steps Time, a set of output wires and registers Var, a simulation result  $S: Time \to Var \to \{0, 1, x, z\}$ , and expected output  $O: Time \to Var \to \{0, 1, x, z\}$ , where x or z correspond to unknown logic value and high impedance respectively, for timestamp  $c_i \in Time$ , we sum over the  $n = |S(c_i)|$  output bits of the circuit. We compare the expected value for wire b from clock cycle  $c_i$ ,  $O_{c_i,b} = O(c_i(b))$ , against the actual value from the simulation result,  $S_{c_i,b} = S(c_i(b))$ . If the bits match, we add to the fitness sum of the circuit; if the bits differ, we subtract from

$<sup>^{3}</sup>$ In a focused investigation of our our three largest benchmarks, both control flow complexity and also the number of wires/registers were found to contribute equally (40–50% each) to the final fault localization size, and thus the scalability of our algorithm.

TABLE I Repair Templates in CirFix

| Defect Category   | Pattern Description                                |

|-------------------|----------------------------------------------------|

| Conditionals      | Negate the conditional of a code block (e.g., if-  |

|                   | statement, while-loop)                             |

| Sensitivity Lists | Trigger an always block on a signal's falling edge |

|                   | Trigger an always block on a signal's rising edge  |

|                   | Trigger an always block on any change to a vari-   |

|                   | able within the block                              |

|                   | Trigger an always block when a signal is level     |

| Assignments       | Change a blocking assignment to non-blocking       |

| 0                 | Change a non-blocking assignment to blocking       |

| Numeric           | Increment the value of an identifier by 1          |

|                   | Decrement the value of an identifier by 1          |

the fitness. An additional penalty weight  $\varphi$  is assigned to bits with values of x (uninitialized) or z (high impedance).

The fitness sum, sum(S, O), and total possible fitness, total(S, O), are defined as follows, where \_ represents a bit value of 0 or 1:

$$sum(S,O) = \sum_{c_i=0}^{k} \sum_{b=0}^{n} \begin{cases} 1 & (O_{c_ib}, S_{c_ib}) \in \{(0,0), (1,1)\} \\ \varphi & (O_{c_ib}, S_{c_ib}) \in \{(x,x), (z,z)\} \\ -1 & (O_{c_ib}, S_{c_ib}) \in \{(1,0), (0,1)\} \\ -\varphi & (O_{c_ib}, S_{c_ib}) \in \{(-,x), (x,-), \\ (z,-), (-,z)\} \end{cases}$$

$$total(S,O) = \sum_{c_i=0}^{k} \sum_{b=0}^{n} \begin{cases} 1 & (O_{c_ib}, S_{c_ib}) \in \{(0,0), (1,1), \\ (1,0), (0,1)\} \\ \varphi & (O_{c_ib}, S_{c_ib}) \in \{(-,x), (x,-), (x,x), \\ (z,-), (-,z), (z,z)\} \end{cases}$$

The normalized fitness of the circuit is then defined as

$$fitness(S,O) = \begin{cases} 0 & sum(S,O) < 0\\ \frac{sum(S,O)}{total(S,O)} & sum(S,O) \ge 0 \end{cases}$$

This novel approach to calculating normalized fitness is effective at capturing whether or not a candidate design is close to the correct implementation of the circuit, and at guiding the search for a repair.

#### C. Repair Templates & Repair Operators

A repair template for a defect in code is defined as a preidentified pattern that can be applied to some aspect of the code to fix the defect. The idea of using templates for APR is well-studied for software [45], [46], [47]. We apply repair templates to aid CirFix in its search for repairs. We propose nine repair templates corresponding to four defect categories for HDL designs. Of the four defect categories we consider, three are suggested in previous work by Sudakrishnan et al. [39] that analyzes the bug fix history of four hardware projects written in Verilog and presents several commonly-occurring fixes for HDL descriptions; we propose the remaining defect category based on our experience with defects in hardware designs. The repair templates in CirFix are presented in Table I. Incorrect conditionals, sensitivity lists, and assignments correspond to the three most commonly occurring defects in the four hardware projects analyzed in previous work [39, Tab. 2]. Note that our repair templates focus on correct behavior from circuit designs during simulation (cf. rules targeting synthesizability [48]). For

an incorrect conditional for a program branch (e.g., the condition for a while-loop or an if-statement), our repair templates can negate the conditional.

CirFix uses two standard repair operators from well-known software repair approaches [22], [49], [50], mutation and crossover, to search the nearby space of circuit designs to produce a repair and to avoid local optima. The input parameter *mutThreshold* (line 11, Algorithm 1) tunes the relative application of mutation and crossover.

As in common software APR approaches (e.g., [22, Sec. III-F]), the mutation operator itself can be characterized into three subtypes: *replace*, *insert*, and *delete*. The mutate function of the CirFix framework generates a random probability value and employs the user-provided replace, insert, and delete thresholds to choose a mutation sub-type. The replace operator picks a random node from the fault localization space and replaces the node with another randomly chosen node from the corresponding fix localization (see Section III-E) space. The insert operator picks a random node from the fix localization space and inserts it after another randomly picked node within a code block. The delete operator picks a random node from the fault localization and replaces it with an empty node — this operation is equivalent to deleting certain statements from the program variant under consideration.

CirFix uses the standard single-point crossover [51], which picks a *crossover point* for each of the two parents. Edit operations to the right of that point are swapped between the two parents. This results in two children program variants, each carrying some information from both parents. The crossover operator plays a key role in avoiding local optima when searching for high-fitness patches.

# D. Selection

Automated program repair techniques based on GP use *selection* to choose parent variants from a population based on fitness. *Tournament selection* [52], a selection approach that selects a random pool of *t* program variants in a population and selects the fittest member of this pool as the parent, has been used widely for software-based APR [22], [49], [53], [54]. CirFix uses tournament selection to select a parent variant to transfer genetic information to the next generation as a child variant. The top e% fittest program variants from the previous generation are automatically included in the next generation, a process known as *elitism* [55], [56].

# E. Fix Localization

Given that fault localization has identified faulty design code to be changed, our *fix localization* provides some guidelines on how to perform the changes. We use fix localization to restrict the scope of the insert and replace operators to reduce the number of syntactically-invalid mutants (cf. [57]).

For the insert operator, we propose to only use statements types (e.g., conditional statements, assignments, etc. — see Annex A.6.4 in the IEEE Standard for Verilog [58] for the full BNF definition of statement types) as the sources for insertion code. We further allow such statements to be inserted only into

initial or always blocks, since such statements inserted elsewhere violate the syntax of Verilog [58, Annex A.6.2]. For the replace operator, we design CirFix such that an item in a Verilog module [58, Annex A.1.4] can be replaced either by another item of the same type, or by an item sharing the same immediate parent type (as specified in the formal syntax definition of Verilog [58, Annex A]). We return to this decision in Section VII.

Our fix localization approach reduces the average number of mutants producing compilation errors in our prototype from 35% to 10%. This reduction is comparable to that of fix localization techniques in software (e.g., [22]).

#### F. Repair Minimization

During the search for a repair, CirFix might produce edits to the code that do not contribute to the repair (e.g., repeated assignment statements within an always block). Such edits do not increase the fitness of the candidate repair, but they could introduce inefficiencies in the final circuit design or affect the design's readability [59].

CirFix removes such extraneous edits in a postprocessing *minimization* step by finding a subset of the edits in a repair patch from which no further elements can be dropped without causing a reduction in the fitness of the patch. As in APR for software (e.g., [22]), we use the delta debugging algorithm [33] to efficiently (i.e., in polynomial time) compute this *one-minimal* subset of the repair patch. The minimized set of repairs is then converted back into HDL code implementing the hardware design correctly.

### **IV. EXPERIMENTAL SETUP**

This section describes the experimental setup for our evaluation of CirFix, including the construction of our new benchmark suite, our choice of experimental parameters, and our human study on evaluating the usability of CirFix's novel fault localization.

For our prototype implementation of CirFix, we use the open-source PyVerilog toolkit [60] (version 1.2.1, modified to support numbering for each node type) to parse a Verilog description of a circuit and produce an AST representing the circuit design code. We use Synopsys VCS [61], the primary hardware verification tool used by a majority of the world's top-twenty semi-conductor companies [62], to simulate the code using a manually instrumented testbench to assess functional correctness of the circuit design. Our prototype for CirFix is implemented using Python 3.6.8 and is made publicly available on GitHub (https://github.com/hammad-a/verilog\_repair).

# A. Benchmark Suite for Hardware Defects

For our evaluation of CirFix, we desire a benchmark suite consisting of faulty hardware designs that are indicative of defects in industry, comprise a wide range in terms of project size, and correspond to a variety of components found in realworld designs. To the best of our knowledge, there are no publicly available benchmarks that satisfy our requirements.

TABLE II BENCHMARK HARDWARE PROJECTS IN OUR EXPERIMENTS. PROJECT AND TESTBENCH SIZES ARE MEASURED BY SOURCE LINES OF CODE AS REPORTED BY THE UNIX WC COMMAND

| Project                  | Description                                                             | Project<br>LOC | Testbench<br>LOC |

|--------------------------|-------------------------------------------------------------------------|----------------|------------------|

| decoder_3_to_8           | 3-to-8 decoder                                                          | 25             | 56               |

| counter                  | 4-bit counter with overflow                                             | 56             | 135              |

| flip_flop                | T-flip flop                                                             | 16             | 39               |

| fsm_full                 | Finite state machine                                                    | 115            | 66               |

| lshift_reg               | 8-bit left shift register                                               | 30             | 44               |

| mux_4_1                  | 4-to-1 multiplexer                                                      | 19             | 51               |

| i2c                      | Two-wire, bidirectional serial bus<br>for data exchange between devices | 2018           | 482              |

| sha3                     | Cryptographic hash function                                             | 499            | 824              |

| tate_pairing             | Core for the Tate bilinear pairing algorithm for elliptic curves        | 2206           | 983              |

| reed_solomon_<br>decoder | Core for Reed-Solomon error cor-<br>rection                             | 4366           | 148              |

| sdram_controller         | Synchronous DRAM memory con-<br>troller                                 | 420            | 95               |

| Total                    |                                                                         | 9770           | 2923             |

Additionally, there is limited open source community support for industrial hardware designs, since such designs are often considered Intellectual Property (IP) of the stakeholder companies. As such, we propose to adapt the defect-seeding approach common in software [63], [64], [65] and present a benchmark suite of *defects scenarios* [22], [37] — each consisting of a circuit design, an instrumented testbench for the design, information for correct circuit behavior, and an expert-transplanted defect from real-life experience — to be used for the evaluation of automated repair techniques for hardware.

1) Selecting Hardware Projects: Every defect scenario includes a base circuit design and a testbench, as introduced in Section II (Fig. 1). We required circuit designs with an available testbench and that admit simulation using the Synopsys VCS tool without any changes to the design code. This is a common requirement comparable to the benchmarks suites for APR in software [22, Sec. IV-A] [66, Sec. 3.1]. The hardware projects for our benchmark suite are presented in Table II. For each hardware project, we need an instrumented testbench to record output values for our fitness function. While the instrumentation process is automatable (see Section III-B), we manually instrument the testbenches for our prototype. Each testbench instrumentation required under 10 lines of Verilog code, took at most 5 minutes of developer time, and did not require any circuit-specific knowledge beyond that available in the testbench (i.e., identifier names of output wires and registers, and the clock cycle duration).

We choose six projects from undergraduate VLSI courses to be indicative of repairing a small component in hardware design. We augment this by choosing the remaining five projects from OpenCores (a popular website for open-source HDL designs) and GitHub collectively to be indicative of repairing the entirety of a large circuit design. Unlike some previous works that only use toy benchmarks for evaluation (e.g., [8], [67]), our benchmarks include a range of project sizes (in terms of source lines of code), and all projects — including those from courses taught at the undergraduate level — correspond to components found in real-world hardware designs. To satisfy our variety requirement, we include a project from each of the key cores listed on the OpenCores website for certified projects (i.e., arithmetic, communication, crypto, error correction, and memory).

2) Obtaining Information for Correct Circuit Behavior: Cir-Fix requires information about expected behavior for a circuit design to assign fitness values to candidate repairs. In APR for software, guidelines for correct behavior often take the form of passing and failing test cases [13]. More generally, however, such information can be induced from a previous version of the design known to be functional [68], [69], [70], [71], [72], [73] or a combination of data mining and static analyses of the design [74], [75], [76], [77], or manually provided by the human developer [78], [79], [80], [81].

This so-called "oracle problem" [82] remains a challenging issue in general for hardware testing and automated repair: implicit, high-level test oracles (e.g., "the program does not divide by zero") used by APR tools for software do not typically carry over to hardware. Given that circuit designs exhibit parallelism and require synchronization against a clock signal [83], how a circuit design reaches a certain output is often equally important as the actual final output produced. As such, any hardware test oracles need detailed information about the intermediate values from design simulation, and it does not suffice to only use the output values from the simulation as correctness information for an approach like CirFix.

For our benchmark suite, we follow an established approach in APR for software [11], [84] and employ a previouslyfunctioning version of the circuit design to record the expected behavior information for circuits in our benchmark suite. We acknowledge that such a previously-functioning version might not always be available, or the circuit specification may have changed. In that case, a developer can use a partially correct or most up-to-date version of the circuit as a starting point, and manually annotate the missing or incorrect bits based on knowledge of the circuit design. This process is analogous to test suite evolution in software [85]. Ultimately, however, if manual developer effort and previous designs are both unavailable, CirFix cannot be applied to repair defects in a circuit.

While we recognize that the process of manually annotating the correctness information may take longer than manually fixing a single defect, this information is a one-time cost as long as the high-level circuit specification (i.e., I/O wires and registers, expected behavior) does not change. Given the number of bugs that may arise during the development and maintenance of a circuit design, we believe that it would still be more cost effective to invest developer effort in the correctness information, which can then be used by CirFix during inexpensive machine idle time (see discussion in Section V-A).

3) Transplanting Hardware Defects: Since actual industrial defects are not made publicly available, we propose an approach based on defect *transplantation* by experts. Previous works have used either randomly-seeded or self-seeded defects for evaluation, potentially admitting bias (e.g., [9]). To combat this, we recruited three hardware experts — two of whom work in industry and one who works in academia, with 19 years of experience with hardware design collectively — to transplant (proprietary or non-public) defects from their real-world experience into otherwise-correct open source implementations of the

#### TABLE III

REPAIR RESULTS FOR CIRFIX. "CAT" INDICATES THE CATEGORY FOR THE DEFECT, "REPAIR TIME" SHOWS THE TIME FOR REPAIR (IN SECONDS), AND A MISSING TIME FOR REPAIR INDICATES NO REPAIR WAS FOUND IN 5

INDEPENDENT TRIALS. CIRFIX PRODUCED PLAUSIBLE REPAIRS TO 21 OF THE 32 DEFECT SCENARIOS IN OUR BENCHMARK SUITE, OF WHICH 16 WERE CORRECT UPON MANUAL INSPECTION BY THE AUTHORS (DENOTED WITH A  $\checkmark$ ) and 14 WERE DEEMED CORRECT ALONG A DIFFERENT CRITERIA BY AN INDEPENDENT EXPERT TEAM (DENOTED WITH A †)

| Project          | Defect Description                       |   | Repair      |

|------------------|------------------------------------------|---|-------------|

|                  |                                          |   | Time (s)    |

| decoder_3_to_8   | Two separate numeric errors              | 1 | √ 13984.3   |

|                  | Incorrect assignment                     | 2 | —           |

| counter          | Incorrect sensitivity list               |   | à19.8       |

|                  | Incorrect reset                          | 1 | √ † 32239.2 |

|                  | Incorrect incremental of counter         | 1 | à27781.3    |

| flip_flop        | Incorrect conditional                    | 1 | à7.8        |

|                  | Branches of if-statement swapped         | 1 | à923.5      |

| fsm_full         | Incorrect case statement                 | 1 | —           |

|                  | Incorrectly blocking assignments         | 1 | 4282.2      |

|                  | Assignment to next state and default in  | 2 | 1536.4      |

|                  | case statement omitted                   |   |             |

|                  | Assignment to next state omitted, incor- | 2 | à37.0       |

|                  | rect sensitivity list                    |   |             |

| lshift_reg       | Incorrect blocking assignment            | 1 | à14.6       |

| 0                | Incorrect conditional                    | 1 | à 33.74     |

|                  | Incorrect sensitivity list               | 1 | à7.8        |

| mux_4_1          | 1 bit instead of 4 bit output            | 1 | —           |

|                  | Hex instead of binary constants          | 1 | 10315.4     |

|                  | Three separate numeric errors            | 2 | 15387.9     |

| i2c              | Incorrect sensitivity list               | 2 | à183        |

|                  | Incorrect address assignment             | 2 | 57.9        |

|                  | No command acknowledgement               | 2 | à 1560.5    |

| sha3             | Off-by-one error in loop                 | 1 | à50.4       |

|                  | Incorrect bitwise negation               | 1 | —           |

|                  | Incorrect assignment to wires            | 2 | —           |

|                  | Skipped buffer overflow check            | 2 | à 50.0      |

| tate_pairing     | Incorrect logic for bitshifting          | 1 | —           |

|                  | Incorrect operator for bitshifting       | 1 | —           |

|                  | Incorrect instantiation of modules       | 2 | —           |

| reed_solomon_    | Insufficient register size for values    | 1 |             |

| decoder          | Incorrect sensitivity list for reset     | 2 | √ 28547.8   |

| sdram_controller | Numeric error in definitions             | 1 | _           |

|                  | Incorrect case statement                 | 2 | _           |

|                  | Incorrect assignments to registers dur-  | 2 | à16607.6    |

|                  | ing synchronous reset                    |   |             |

|                  |                                          |   |             |

hardware projects in our benchmark suite. We desire defects in our benchmark suite corresponding to a variety of complexities, both in terms of finding and fixing the defect. As such, we define two defect categories for this process:

- *Category 1:* A Category 1 (i.e., "easy") defect denotes mistakes pertaining to simpler, higher-level aspects of circuit design.

- *Category 2:* A Category 2 (i.e., "hard") defect denotes more intricate errors that usually require more effort to diagnose, understand, and/or fix.

To get the benefits of real-world defects in our benchmark suite, we instructed our recruited experts to transplant and categorize real defects they have previously encountered to the open-source circuits in our benchmark. We also asked our experts for "... variety in how the defects appear and would be fixed, as long as that variety aligns with how often [they] observe these bugs or mistakes in real life". We further required that any transplanted defects should compile successfully and change the externally-visible behavior of the circuit with respect to the instrumented testbench, and correspond to approximately the same level of complexity as that of real-world defects.

Table III lists the transplanted defects from our experts that met these criteria. In total, our experimental setup includes 32 different defect scenarios spanning across 11 hardware projects, with 19 Category 1 (i.e., "easy") and 13 Category 2 (i.e., "hard") defects. This benchmark suite is  $1.5-10 \times$  as large as benchmark suites used in the hardware diagnosis literature [6], [7], [8], [9], [39], [67].

# B. Algorithm Parameters

We refer to each execution of CirFix as a *trial*. Each trial is initialized with a distinct random seed for reproducibility of our results, and conducted on a quad-core 3.4 GHz machine with hyperthreading and 16 GB of memory. We ran 5 independent CirFix trials for each defect scenario, stopping when an acceptable repair was found. Each individual trial was terminated after 8 generations of evolution or 12 hours of wall-clock time (whichever came first).

For the GP parameters, we use population size popSize = 5000, repair template threshold rtThreshold = 0.2, mutThreshold = 0.7. In line with established practices from APR for software [22], [49], [53], we use deletion, insertion, and replacement thresholds of 0.3, 0.3 and 0.4 respectively. For parent selection, we use a tournament size t = 5 to increase the selection pressure on candidate variants [86]. For elitism, we propagate the top e = 5% of each generation to the next without any modifications.

For fitness evaluations, we use  $\varphi = 2$  as additional weight assigned to bits with values of x or z. This makes incorrect comparisons between ill-defined wires twice as detrimental to the fitness score of a candidate repair as binary bit mismatches. We found that a weight  $\varphi = 1$  did not penalize such incorrect comparisons enough (resulting in longer times to find a repair), while  $\varphi = 3$  caused too significant a drop in fitness for candidate variants (negatively impacting the exploration of the search space for a repair).

We evaluated other values suggested by literature (e.g., smaller population sizes [84], [87]), and found no significant differences in CirFix's performance.

## C. Human Study Protocol

We also investigate the usability of our novel fault localization algorithm (see Section III-A), independent of the automated repair context. We asked humans (i.e., hardware engineers), rather than CirFix, to assess the quality and usefulness of the fault localization algorithm. To investigate the incremental benefit of our fault localization, we consider three scenarios: the full output of the algorithm (see Section III-A), only initially implicated statements of the algorithm (no transitive information, only line 1 of Algorithm 2), and no fault localization annotations.

Participant Recruitment: Under UM IRB-HUM00199335, we recruited a combination of undergraduate and graduate computer science students (n = 41). One student reported having less than a month of experience, ten students reported having 1 to 4 months experience, seven students reported having 4 months to 1 a of experience, nine reported having 1 to 2 years of experience, and the remaining six reported having 2 or more years of experience. We drew students from five undergraduate courses, a graduate course, and a computer engineering lab mailing list at the University of Michigan. At the beginning of the survey, participants' background in Verilog was collected (e.g.,

Fig. 2. Example of defect scenario presented to participants.

any courses they have taken). Participant data was anonymized, but they could optionally request a \$25 USD gift card as compensation. We collected 30

*Debugging Scenarios:* We sampled (uniformly at random) 10 defect scenarios each from student and OpenCores projects, with roughly equal numbers of Category 1 and 2 defects. To favor readability and comprehension within a time-constrained human study (e.g., [88], [89]), we filtered out defects that resulted in more than 100 lines of code implicated by fault localization. This resulted in 12 snippets from the programs in Table II: eight from student projects and four from OpenCore projects. Each debugging scenario included information on the parent hardware design and documentation on the desired properties and output.

*Debugging Task:* Each participant was sequentially presented with 6 distinct randomly-chosen debugging scenarios. Each scenario was paired with a debugging hint: textual highlighting of implicated code, as shown in Fig. 2.

Participants were asked to: (1) identify faulty lines in the snippet, (2) indicate which lines they would alter to fix the defect, (3) propose how they would alter the lines to fix the defect if they could patch it. If the snippet version presented to the participant contained fault localization hints, the participant also rated the usefulness and accuracy of those hints on a 1–5 scale.

## V. CIRFIX REPAIR EVALUATION

In this section, we present an empirical evaluation on our benchmark suite of hardware defect scenarios. We analyzed the following research questions:

*RQ1:* What fraction of defect scenarios can CirFix repair, and how sensitive is our fault localization approach?

*RQ2:* How effective is the CirFix fitness function at guiding the search for a repair to a circuit description?

In prior work [23], we addressed two additional research questions: (1) what is the performance of CirFix on repairing two different types of defects varying in difficulty and (2) how sensitive is CirFix to the quality of the information for expected behavior. We found CirFix to repair both Category 1 and 2 defects with comparably high success rates, and found CirFix to not be overly sensitive to the quality of the expected circuit behavior information, yielding high repair rates and quality even under settings when low quality correctness information is used as input to the algorithm.

Consider the circuit design below

### A. RQ1. Repair Rate, Quality, and Sensitivity for CirFix

Repair Rate: Table III presents the repair results for each defect scenario. CirFix produced plausible (i.e., testbenchadequate) repairs for 21 of the 32 (65.6%) defects. Of the 11 defects that were not repaired, 4 exhausted resource limits while 7 required edits not supported by CirFix operators and repair templates. While a direct comparison between CirFix and APR for software is not possible, we observe that the repair rate of CirFix comparable to the reported repair rates of well-known software repair approaches, e.g., GenProg (52.4%) [22], Angelix (34.1%) [90], and TBar (53.1%) [46]. When comparing CirFix to a more straightforward search algorithm applying edits at uniform to a circuit design, we found that the brute force algorithm did not scale to the complexity of defects in our benchmark suite and reported no repairs within the 12 h resource bounds. Though not part of a comprehensive scientific evaluation, when tested on simple single-edit defects (not part of our benchmark suite) in smaller projects from undergraduate courses, the brute-force algorithm still took hours to find repairs that CirFix found in seconds to minutes, highlighting CirFix's efficient pruning of the search space. We leave a full investigation of CirFix against more straightforward search as future work. Note that we can not compare CirFix to other baselines for hardware repair, since at the time of writing, there are no baselines that operate on source code level Verilog descriptions to automatically repair defects; indeed, that is precisely the improvement CirFix brings over the state-of-the-art.

The average wall-clock time for a trial to find a repair was 2.03 hours, of which an average of over 90% was spent on fitness evaluations (i.e., design simulations). Most non-repairs timed out after 12 hours, though defects for some projects with smaller search spaces hit the 8 generation maximum first. These results are in line with previously-reported patterns of behavior for APR for software, supporting our hypothesis that the CirFix algorithm is capable of performing as well on hardware design defects as established APR approaches do on software.

We acknowledge that wall-clock runtime for CirFix on a given defect can be longer than that of an expert human manually fixing the defect. However, CirFix was designed to favor situations in which developer time is significantly more expensive than machine time: it is often more cost-effective to run tools like CirFix using inexpensive machine idle time and then to employ expensive developer time to ensure the repairs are correct before being synthesized [35]. As such, we see CirFix as being costeffective in terms of reducing the burden on designers.

*Repair Quality:* We follow the approach taken by Long and Rinard [50] for patch assessment since it follows best practices in the APR literature [43], [91]. We manually analyze the 21 repairs produced by CirFix. We found 16 of the generated repairs to exhibit correct behavior, with the final 5 to be correct only with respect to the testbench (i.e., overfitting).<sup>4</sup> While

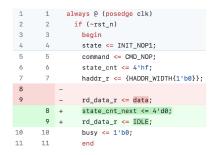

Fig. 3. A representative multi-edit repair by CirFix for a defect in the sdram\_controller benchmark. The original defect, with a missing and an incorrect assignment, is shown in red; the repaired code is shown in green. Edits on lines 8 and 9 correspond to insert and replace operations respectively.

room for improvement remains, software industrial deployments with similar rates have proved useful: for example, Bloomberg reported that a 48% correct patch rate was associated with "very positive" feedback and a general "helpful" opinion [93, p. 5].

We augment this analysis with an independent assessment from Yang et al. an established expert team in APR [24], [25], [26], [27], [28], who analyzed the semantics of the produced repairs against the human-written patches and found 14 of the produced repairs to be semantically identical to the human patches (see Table III). While APR expertise is not equivalent to domain expertise, APR experts tend to be more suited to assessing the patches produced by these methods due to "creative" (or adversarial or potentially-overfitting) nature of such patches [94], [95], [96], and evidence suggests that domainexperts may not be a strong gold standard [97]. We acknowledge that this assessment is not a substitute for a full human study on patch correctness; however, having two independent teams find converging results adds confidence that a majority of the plausible repairs do not overfit to the testbench (a common problem in APR for software [50], [98], [99]), since we inspect intermediate wire values when assigning fitness scores. We do note that correctness is critical in hardware designs (e.g., since manufactured chips cannot be easily updated once deployed), and our use case does not involve deploying patches directly but instead showing plausible patches to developers to reduce maintenance costs [35], [36].

We observed that 7 out of the 21 minimized repairs were multi-edit repairs, highlighting CirFix's ability to produce repairs to defects that require more than one change to the circuit design. By comparison, common APR approaches for software usually only produce single-edit repairs [11], and only recently have there been works investigating multi-edit repairs [90], [100].

For instance, in a faulty version of the sdram\_controller benchmark, one of our experts changed assignments to two wires to transplant a Category 2 defect, causing incorrect functionality in the host interface. CirFix assigned this faulty design code a fitness value of 0.818 based on output mismatch. CirFix repaired this defect scenario in 4.6 hours by inserting a new assignment and modifying an existing assignment. The original defect and the repaired code are shown in Fig. 3. This is an indicative instance of CirFix repairing Category 2 (i.e., "hard") defects

<sup>&</sup>lt;sup>4</sup>We focus on correctness of a patch against the specification of the circuit (e.g., ensuring the absence of clock- or reset-domain issues) during our manual inspections. The synthesizability of the design is left to be evaluated by the developer during the validation phase of the hardware design process [92], but we discuss the synthesizability of CirFix in practice in Section VII.

#### TABLE IV

REPAIR RESULTS FOR CIRFIX WITH ADDED NOISE TO INITIAL MISMATCH SET FOR OUR FAULT LOCALIZATION ALGORITHM. "DEFECT CAT." INDICATES THE CATEGORY FOR THE DEFECT, "NORMALIZED REPAIR TIME" SHOWS THE NORMALIZED TIME FOR REPAIR (IN SECONDS) WHEN COMPARED TO THE ORIGINAL REPAIR, AND A '—' INDICATES NO REPAIR WAS FOUND IN 5 INDEPENDENT TRIALS. "NOISE" INDICATES THE PERCENT OF DISTURBANCE PLACED ON THE FAULT LOCALIZATION. THE ORDERING OF THE BENCHMARKS FOLLOWS TABLE III

| Project        | Defect | Normalized Repair Time |               |                |

|----------------|--------|------------------------|---------------|----------------|

| , í            | Cat.   | 25% Noise              | 50% Noise     | 75% Noise      |

| decoder_3_to_8 | 1      | 1.11×                  | —             | —              |

| counter        | 1      | $0.49 \times$          | $0.45 \times$ | $0.05 \times$  |

|                | 1      | 0.48 	imes             | $0.58 \times$ | $0.86 \times$  |

|                | 1      | $0.06 \times$          | $0.98 \times$ | $0.98 \times$  |

| flip_flop      | 1      | $0.99 \times$          | $0.38 \times$ | 1.86×          |

|                | 1      | $0.87 \times$          | $1.18 \times$ | $0.35 \times$  |

| fsm_full       | 1      | $0.77 \times$          | $0.08 \times$ | $0.58 \times$  |

|                | 2      | $0.58 \times$          | $0.57 \times$ | $0.81 \times$  |

|                | 2      | $3.21 \times$          | $3.24 \times$ | $1.76 \times$  |

| lshift_reg     | 1      | $1.07 \times$          | $0.11 \times$ | $0.11 \times$  |

|                | 1      | $0.18 \times$          | $0.49 \times$ | $0.21 \times$  |

|                | 1      | $1.01 \times$          | $0.32 \times$ | $0.60 \times$  |

| mux_4_1        | 1      | $0.27 \times$          | $0.35 \times$ | $0.61 \times$  |

|                | 2      | $1.19 \times$          | $1.27 \times$ | $1.24 \times$  |

| i2c            | 2      | $0.93 \times$          | 0.39×         | $0.34 \times$  |

|                | 2      | 0.04 	imes             | $0.13 \times$ | $0.13 \times$  |

|                | 2      | $18.57 \times$         | —             | $15.88 \times$ |

| sha3           | 1      | $1.44 \times$          | $2.80 \times$ | 3.60×          |

|                | 2      | $0.67 \times$          | $0.33 \times$ | $0.73 \times$  |

| reed_solomon_  | 2      | $1.39 \times$          | $0.52 \times$ | $1.29 \times$  |

| decoder        |        |                        |               |                |

| sdram_         | 2      | $0.11 \times$          | 1.22×         | $0.55 \times$  |

| controller     |        |                        |               |                |

with multiple edits to the faulty circuit design. We return to multi-edit repairs in the human study (Section VI).

*Fault Localization Sensitivity:* To assess repair performance as fault localization quality decreases, we conducted a targeted experiment reducing the quality of the initial fault location available to CirFix in a controlled manner. This sort of investigation, in which the sensitivity of the algorithm with respect to fault localization is assessed, is important is software APR [101], [102], [103], [104].

When simulation outputs are compared against expected behavior to produce the initial set of wires and registers with mismatched values (see Section III-A), we also randomly include some correct wires and registers (with probability 25%, 50%, or 75%) as "noise". Because our fault localization is a transitive fixed point calculation, additional initial elements may result in larger fault localization sets (e.g., informally, the traditional scalability problem with fault localization is that almost everything may end up implicated).

We focus on defect scenarios CirFix successfully repaired. Table IV presents normalized results of five trials at each noise level. Of the 21 defect scenarios CirFix originally plausibly repaired, CirFix also found plausible repairs for all 21 when subjected to 25% noise, 19 at 50% noise, and 20 at 75% noise. Execution times with lower-quality fault localization are not statistically different to those found without fault localization noise (p = 0.7, p = 0.6, p = 0.9, unpaired Student t-test), suggesting that CirFix performs similarly even if the design or testbench does not admit precise fault localization. Any difference in execution times can be attributed to the randomness of the search for repairs (a larger fault localization set may result in new candidate repairs or repairs being considered in a different order). An investigation of this outcome reveals that many of the same registers and wires were transitively implicated in both cases (i.e., with and without noise). For example, in the largest benchmark (reed\_solomon\_decoder), there are 10 (out of 11 maximum) elements in the initial mismatch set and 114 in the final fault localization set. With 75% noise, there are 11 elements in the initial set but 124 in the final fault localization set. This small increase suggests that many of the potential wires and registers were already transitively implicated without the added noise. Our targeted experiment furthers confidence that CirFix's novel fault localization approach scales to larger designs or those with more complicated or less precise testbenches that do not admit accurate initial fault localization.

CirFix produced plausible repairs to 21 out of 32 (65.6%) defect scenarios in our benchmark suite, of which 16 repairs were fully correct and 5 were correct only with respect to the testbench. The CirFix repair rate is comparable to strong results from APR for software, suggesting that our approach brings the benefits of APR to hardware designs. Lastly, our sensitivity investigation gives confidence that CirFix's fault localization approach scales to larger designs.

# B. RQ2. Quality of Fitness Function

CirFix's high repair rate suggests that our fitness function, coupled with our testbench instrumentation approach, is highly effective at guiding the search for repairs to faulty circuit designs. We observe that for each change to design code that brings a candidate repair closer to a correct repair, our fitness function shows a corresponding increase in the candidate repair's fitness (i.e., our fitness function has a strong fitness distance correlation, a trait that makes genetic algorithms thrive [44]). This is best observed in transplanted defects that require multiple edits to the design code to be corrected. For instance, one of our experts transplanted a defect in the counter project that required three edits to the design be repaired. The triple-edit repair produced by CirFix for this defect scenario incrementally raised the fitness of the best candidate patch first from 0 to 0.58, then to 0.77, and finally to 1.0 to produce a correct repair. Similar behavior is seen for every other multi-edit repair produced by CirFix, indicating that our fitness function is effective at capturing incremental changes to a circuit design during the search for a repair.

We also observe instances where CirFix produces a repair deemed unfit by our fitness function and instrumented testbench but considered correct by the original, unannotated testbench. We examine one such case in detail, related to the out\_stage module in the error correction core reed\_solomon\_decoder. This module is responsible for generating output bytes from pipelining input memories. A faulty version of this circuit obtained from one of our experts removed the reset wire from the sensitivity list of an always block. This caused incorrect resetting of output wires by the circuit. Our fitness function assigns the incorrect design code a non-perfect fitness value of 0.999. The original testbench, however, reports no errors in the incorrect code. The final repair produced by CirFix fixes this defect and passes all checks by the original testbench and our instrumented testbench. This suggests that our fitness function and testbench instrumentation can catch errors beyond the capabilities of the original testbench without adding any additional testing logic.

The CirFix fitness function is highly effective at capturing incremental changes to a circuit's design code to guide the search for a repair, and has the potential to increase testing prowess without any added testing logic to a bench.

# VI. EVALUATION OF HUMAN STUDY

Next, we present statistical analyses of the responses to our human study. In total, 41 users participated in our survey and each completed 6 debugging tasks. We consider the following additional research questions:

*RQ3*: Does CirFix's fault localization algorithm improve designers' objective performances?

*RQ4:* In what contexts do designers find CirFix's fault localization algorithm helpful?

#### A. RQ3. Fault Localization and Human Performance

We assessed programmer performance by evaluating (1) Fscores ( $F_1$ ) of correctly-identified faults for each debugging task by each participant and (2) total time taken to complete a debugging task within no specific time limit (see Section IV-C). A participant is said to correctly identify faults for a given defect scenario if they identified program line(s) that contain a bug or missing line(s). F-scores were evaluated by calculating the harmonic mean of recall and precision.