## ARM°v7-M Architecture Reference Manual Errata markup

#### ARMy7-M Architecture Reference Manual

Copyright © 2006-2010 ARM Limited. All rights reserved.

#### Release Information

The following changes have been made to this document.

Change history

| Date             | Issue           | Confidentiality                        | Change                                                                                                   |

|------------------|-----------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|

| June 2006        | A               | Non-confidential                       | Initial release                                                                                          |

| July 2007        | В               | Non-confidential                       | Second release, errata and changes documented separately                                                 |

| September 2008   | С               | Non-confidential,<br>Restricted Access | Options for additional watchpoint based trace in the DWT, plus errata updates and clarifications.        |

| 12 February 2010 | D               | Non-confidential                       | Fourth release, adds DSP and Floating-point extensions, and extensive clarifications and reorganization. |

| November 2010    | Derrata 2010_Q3 | Non-confidential                       | Marked-up errata PDF, see page iii for more information.                                                 |

#### **Proprietary Notice**

This ARM Architecture Reference Manual is protected by copyright and the practice or implementation of the information herein may be protected by one or more patents or pending applications. No part of this ARM Architecture Reference Manual may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this ARM Architecture Reference Manual.

Your access to the information in this ARM Architecture Reference Manual is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations of the ARM architecture infringe any third party patents.

This ARM Architecture Reference Manual is provided "as is". ARM makes no representations or warranties, either express or implied, included but not limited to, warranties of merchantability, fitness for a particular purpose, or non-infringement, that the content of this ARM Architecture Reference Manual is suitable for any particular purpose or that any practice or implementation of the contents of the ARM Architecture Reference Manual will not infringe any third party patents, copyrights, trade secrets, or other rights.

This ARM Architecture Reference Manual may include technical inaccuracies or typographical errors.

To the extent not prohibited by law, in no event will ARM be liable for any damages, including without limitation any direct loss, lost revenue, lost profits or data, special, indirect, consequential, incidental or punitive damages, however caused and regardless of the theory of liability, arising out of or related to any furnishing, practicing, modifying or any use of this ARM Architecture Reference Manual, even if ARM has been advised of the possibility of such damages.

Words and logos marked with ® or ™ are registered trademarks or trademarks of ARM Limited, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Copyright © 2006-2010 ARM Limited

110 Fulbourn Road Cambridge, England CB1 9NJ

Restricted Rights Legend: Use, duplication or disclosure by the United States Government is subject to the restrictions set forth in DFARS 252.227-7013 (c)(1)(ii) and FAR 52.227-19.

This document is Non-Confidential but any disclosure by you is subject to you providing notice to and the acceptance by the recipient of, the conditions set out above.

| In this document, where the term ARM is used to refer to the company it means "ARM or any of its subsidiaries as appropriate".                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                                                                                                                                      |

| The term ARM is also used to refer to versions of the ARM architecture, for example ARMv6 refers to version 6 of the ARM architecture. The context makes it clear when the term is used in this way.                                                                      |

| <del></del>                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                           |

| Note                                                                                                                                                                                                                                                                      |

| —— Note ———                                                                                                                                                                                                                                                               |

| For this errata PDF, pages i to iii have been replaced, by an edit to the PDF, to include this note, and to show this errata PDF in the Change History table. The remainder of the PDF is the original release PDF of issue D of the document, with errata markups added. |

## Contents

## **ARMv7-M Architecture Reference Manual**

|           | Prefa | About this manual Using this manual Conventions Further reading Feedback | xxiii<br>xxvi<br>xxvii |

|-----------|-------|--------------------------------------------------------------------------|------------------------|

| Part A    | App   | lication Level Architecture                                              |                        |

| Chapter 1 | Intro | duction                                                                  |                        |

| •         | A1.1  | About the ARMv7 architecture, and architecture profiles                  | A1-32                  |

|           | A1.2  | The ARMv7-M architecture profile                                         | A1-33                  |

|           | A1.3  | Architecture extensions                                                  |                        |

| Chapter 2 | Appli | ication Level Programmers' Model                                         |                        |

| -         | A2.1  | About the application level programmers' model                           | A2-38                  |

|           | A2.2  | ARM processor data types and arithmetic                                  |                        |

|           | A2.3  | Registers and execution state                                            |                        |

|           | A2.4  | Exceptions, faults and interrupts                                        | A2-50                  |

|           | A2.5  | Coprocessor support                                                      | A2-52                  |

|           | A2.6  | The optional Floating-point extension                                    | A2-53                  |

|           |       |                                                                          |                        |

| Chapter 3 | ARM    | Architecture Memory Model                                 |        |

|-----------|--------|-----------------------------------------------------------|--------|

| •         | A3.1   | Address space                                             | A3-82  |

|           | A3.2   | Alignment support                                         | A3-83  |

|           | A3.3   | Endian support                                            | A3-85  |

|           | A3.4   | Synchronization and semaphores                            | A3-89  |

|           | A3.5   | Memory types and attributes and the memory order model    | A3-99  |

|           | A3.6   | Access rights                                             | A3-109 |

|           | A3.7   | Memory access order                                       | A3-111 |

|           | A3.8   | Caches and memory hierarchy                               | A3-120 |

| Chapter 4 | The A  | ARMv7-M Instruction Set                                   |        |

| •         | A4.1   | About the instruction set                                 | A4-124 |

|           | A4.2   | Unified Assembler Language                                |        |

|           | A4.3   | Branch instructions                                       |        |

|           | A4.4   | Data-processing instructions                              |        |

|           | A4.5   | Status register access instructions                       |        |

|           | A4.6   | Load and store instructions                               |        |

|           | A4.7   | Load Multiple and Store Multiple instructions             |        |

|           | A4.8   | Miscellaneous instructions                                |        |

|           | A4.9   | Exception-generating instructions                         |        |

|           | A4.10  | Coprocessor instructions                                  |        |

|           | A4.11  | Floating-point load and store instructions                |        |

|           | A4.12  | Floating-point register transfer instructions             |        |

|           | A4.13  | Floating-point data-processing instructions               |        |

| Chapter 5 | The T  | humb Instruction Set Encoding                             |        |

| onapto. o | A5.1   | Thumb instruction set encoding                            | Δ5-152 |

|           | A5.2   | 16-bit Thumb instruction encoding                         |        |

|           | A5.3   | 32-bit Thumb instruction encoding                         |        |

|           |        | ·                                                         |        |

| Chapter 6 |        | loating-Point Instruction Set Encoding                    |        |

|           | A6.1   | Overview                                                  |        |

|           | A6.2   | Floating-point instruction syntax                         |        |

|           | A6.3   | Register encoding                                         |        |

|           | A6.4   | Floating-point data-processing instructions               |        |

|           | A6.5   | Extension register load or store instructions             |        |

|           | A6.6   | 32-bit transfer between ARM core and extension registers  |        |

|           | A6.7   | 64-bit transfers between ARM core and extension registers | A6-199 |

| Chapter 7 | Instru | uction Details                                            |        |

|           | A7.1   | Format of instruction descriptions                        |        |

|           | A7.2   | Standard assembler syntax fields                          | A7-207 |

|           | A7.3   | Conditional execution                                     | A7-208 |

|           | A7.4   | Shifts applied to a register                              |        |

|           | A7.5   | Memory accesses                                           |        |

|           | A7.6   | Hint Instructions                                         | A7-215 |

|           |        |                                                           |        |

|           | A7.7         | Alphabetical list of ARMv7-M Thumb instructions        | A7-216 |

|-----------|--------------|--------------------------------------------------------|--------|

| Part B    | Sys          | tem Level Architecture                                 |        |

| Chapter 1 | Syste        | em Level Programmers' Model                            |        |

| •         | B1.1         | Introduction to the system level                       | B1-616 |

|           | B1.2         | About the ARMv7-M memory mapped architecture           |        |

|           | B1.3         | Overview of system level terminology and operation     |        |

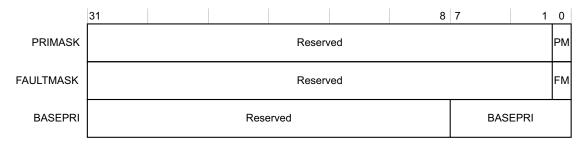

|           | B1.4         | Registers                                              |        |

|           | B1.5         | ARMv7-M exception model                                |        |

|           | B1.6         | Floating-point support                                 |        |

| Chapter 2 | Svste        | em Memory Model                                        |        |

|           | B2.1         | About the system memory model                          | B2-692 |

|           | B2.2         | Pseudocode details of general memory system operations |        |

| Chapter 3 | Syste        | em Address Map                                         |        |

| p         | B3.1         | The system address map                                 | B3-704 |

|           | B3.2         | System Control Space (SCS)                             |        |

|           | B3.3         | The system timer, SysTick                              |        |

|           | B3.4         | Nested Vectored Interrupt Controller, NVIC             |        |

|           | B3.5         | Protected Memory System Architecture, PMSAv7           |        |

| Chapter 4 | The (        | CPUID Scheme                                           |        |

|           | B4.1         | About the CPUID scheme                                 | B4-778 |

|           | B4.2         | Processor Feature ID Registers                         |        |

|           | B4.3         | Debug Feature ID register                              |        |

|           | B4.4         | Auxiliary Feature ID register                          |        |

|           | B4.5         | Memory Model Feature Registers                         |        |

|           | B4.6         | Instruction Set Attribute Registers                    |        |

|           | B4.7         | Floating-point feature identification registers        |        |

| Chapter 5 | Svste        | em Instruction Details                                 |        |

|           | B5.1         | About the ARMv7-M system instructions                  | B5-798 |

|           | B5.2         | ARMv7-M system instruction descriptions                |        |

| Part C    | Deb          | ug Architecture                                        |        |

| Chapter 1 | ARM          | v7-M Debug                                             |        |

|           | C1.1         | Introduction to ARMv7-M debug                          | C1-810 |

|           | C1.2         | The Debug Access Port                                  |        |

|           | C1.2         | Overview of the ARMv7-M debug features                 |        |

|           | C1.3         | Debug and reset                                        |        |

|           | C1.4<br>C1.5 | Debug event behavior                                   |        |

|           | 01.0         | Debug event benavior                                   | 01-023 |

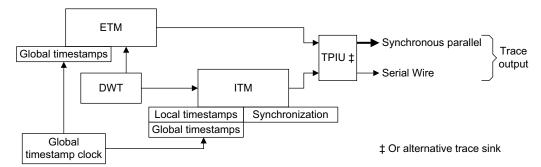

|            | C1.6<br>C1.7<br>C1.8<br>C1.9<br>C1.10<br>C1.11 | Debug register support in the SCS The Instrumentation Trace Macrocell The Data Watchpoint and Trace unit Embedded Trace Macrocell support Trace Port Interface Unit Flash Patch and Breakpoint unit | C1-843<br>C1-856<br>C1-896<br>C1-897 |

|------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Appendix A | <b>ARM\</b><br>A.1                             | 77-M CoreSight Infrastructure IDs CoreSight infrastructure IDs for an ARMv7-M implementati AppxA-914                                                                                                | on                                   |

| Annondiy B | Logo                                           |                                                                                                                                                                                                     |                                      |

| Appendix B | B.1                                            | cy Instruction Mnemonics                                                                                                                                                                            | AnnyD 019                            |

|            | В.1<br>В.2                                     | Thumb instruction mnemonics  Pre-UAL pseudo-instruction NOP                                                                                                                                         |                                      |

|            | B.3                                            | Pre-UAL floating-point instruction mnemonics                                                                                                                                                        |                                      |

| Appendix C | Depre                                          | ecated Features in ARMv7-M                                                                                                                                                                          |                                      |

| Apponaix • | C.1                                            | Deprecated features of the ARMv7-M architecture                                                                                                                                                     | AppxC-928                            |

| Appendix D | Debu                                           | g ITM and DWT Packet Protocol                                                                                                                                                                       |                                      |

|            | D.1                                            | About the ITM and DWT packets                                                                                                                                                                       | AppxD-932                            |

|            | D.2                                            | Packet descriptions                                                                                                                                                                                 |                                      |

|            | D.3                                            | DWT use of Hardware source packets                                                                                                                                                                  | AppxD-944                            |

| Appendix E | ARM                                            | 77-R Differences                                                                                                                                                                                    |                                      |

|            | E.1                                            | About the ARMv7-M and ARMv7-R architecture profiles                                                                                                                                                 |                                      |

|            | E.2                                            | Endian support                                                                                                                                                                                      |                                      |

|            | E.3                                            | Application level support                                                                                                                                                                           |                                      |

|            | E.4                                            | System level support                                                                                                                                                                                |                                      |

|            | E.5                                            | Debug support                                                                                                                                                                                       | AppxE-956                            |

| Appendix F | Pseud                                          | docode Definition                                                                                                                                                                                   |                                      |

|            | F.1                                            | Instruction encoding diagrams and pseudocode                                                                                                                                                        |                                      |

|            | F.2                                            | Limitations of pseudocode                                                                                                                                                                           |                                      |

|            | F.3                                            | Data types                                                                                                                                                                                          |                                      |

|            | F.4                                            | Expressions                                                                                                                                                                                         |                                      |

|            | F.5                                            | Operators and built-in functions                                                                                                                                                                    |                                      |

|            | F.6                                            | Statements and program structure                                                                                                                                                                    |                                      |

|            | F.7                                            | Miscellaneous helper procedures and functions                                                                                                                                                       | AppxF-978                            |

| Appendix G | Pseud                                          | docode Index                                                                                                                                                                                        |                                      |

|            | G.1                                            | Pseudocode operators and keywords                                                                                                                                                                   |                                      |

|            | G.2                                            | Pseudocode functions and procedures                                                                                                                                                                 | AppxG-988                            |

#### Appendix H Register Index

| H.1 | ARM core registers                 | AppxH-1002 |

|-----|------------------------------------|------------|

| H.2 | Floating-point extension registers | AppxH-1003 |

| H.3 | Memory mapped system registers     | AppxH-1004 |

| H.4 | Memory-mapped debug registers      | AppxH-1007 |

#### Glossary

Contents

## **List of Tables**

## **ARMv7-M Architecture Reference Manual**

|             | Change history                                                              | İl     |

|-------------|-----------------------------------------------------------------------------|--------|

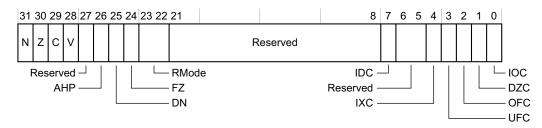

| Table A2-1  | FPSCR bit assignments                                                       | A2-56  |

| Table A2-2  | Default NaN encoding                                                        | A2-64  |

| Table A2-3  | Floating-point exception default results                                    | A2-65  |

| Table A2-4  | FP comparison flag values                                                   |        |

| Table A3-1  | Load-store and element size association                                     | A3-87  |

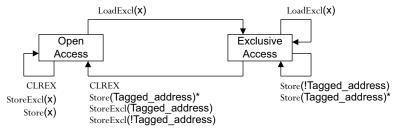

| Table A3-2  | Effect of Exclusive instructions and write operations on local monitor      | A3-91  |

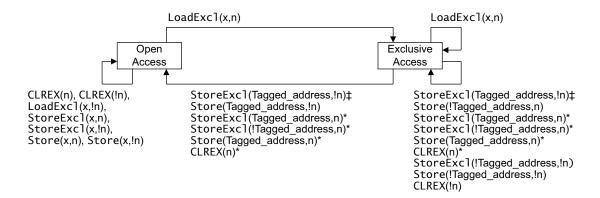

| Table A3-3  | Effect of load/store operations on global monitor for processor(n)          | A3-95  |

| Table A3-4  | Memory attribute summary                                                    | A3-100 |

| Table A4-1  | Branch instructions                                                         |        |

| Table A4-2  | Standard data-processing instructions                                       |        |

| Table A4-3  | Shift instructions                                                          | A4-132 |

| Table A4-4  | General multiply instructions                                               |        |

| Table A4-5  | Signed multiply instructions, ARMv7-M base architecture                     | A4-133 |

| Table A4-6  | Signed multiply instructions, ARMv7-M DSP extension                         |        |

| Table A4-7  | Unsigned multiply instructions, ARMv7-M base architecture                   |        |

| Table A4-8  | Unsigned multiply instructions, ARMv7-M DSP extension                       |        |

| Table A4-9  | Saturating instructions, ARMv7-M base architecture                          | A4-135 |

| Table A4-10 | Halfword saturating instructions, ARMv7-M DSP extension                     | A4-135 |

| Table A4-11 | Saturating addition and subtraction instructions, ARMv7-M DSP extens A4-135 | sion   |

| Table A4-12 | Packing and unpacking instructions, ARMv7-M base architecture               | A4-136 |

| Table A4-13 | Packing and unpacking instructions, ARMv7-M DSP extension                   | A4-136 |

|             |                                                                             |        |

| Table A4-14 | Parallel addition and subtraction instructions                           | A4-138 |

|-------------|--------------------------------------------------------------------------|--------|

| Table A4-15 | Miscellaneous data-processing instructions, ARMv7-M base architecture    | A4-138 |

| Table A4-16 | Miscellaneous data-processing instructions, ARMv7-M DSP extension        |        |

| Table A4-17 | Load and store instructions                                              |        |

| Table A4-18 | Load Multiple and Store Multiple instructions                            | A4-144 |

| Table A4-19 | Miscellaneous instructions                                               | A4-145 |

| Table A4-20 | FP extension register load and store instructions                        |        |

| Table A4-21 | FP extension register transfer instructions                              | A4-149 |

| Table A4-22 | Floating-point data-processing instructions                              |        |

| Table A5-1  | 16-bit Thumb instruction encoding                                        | A5-156 |

| Table A5-2  | 16-bit shift (immediate), add, subtract, move and compare encoding       | A5-157 |

| Table A5-3  | 16-bit data processing instructions                                      | A5-158 |

| Table A5-4  | Special data instructions and branch and exchange                        | A5-159 |

| Table A5-5  | 16-bit Load/store instructions                                           | A5-160 |

| Table A5-6  | Miscellaneous 16-bit instructions                                        | A5-161 |

| Table A5-7  | If-Then and hint instructions                                            | A5-162 |

| Table A5-8  | Branch and supervisor call instructions                                  |        |

| Table A5-9  | 32-bit Thumb encoding                                                    | A5-164 |

| Table A5-10 | 32-bit modified immediate data processing instructions                   | A5-165 |

| Table A5-11 | Encoding of modified immediates in Thumb data-processing instructions    | A5-166 |

| Table A5-12 | 32-bit unmodified immediate data processing instructions                 |        |

| Table A5-13 | Branches and miscellaneous control instructions                          |        |

| Table A5-14 | Change Processor State, and hint instructions                            |        |

| Table A5-15 | Miscellaneous control instructions                                       |        |

| Table A5-16 | Load Multiple and Store Multiple instructions                            |        |

| Table A5-17 | Load/store dual or exclusive, table branch                               |        |

| Table A5-18 | Load word                                                                |        |

| Table A5-19 | Load halfword, memory hints                                              |        |

| Table A5-20 | Load byte, memory hints                                                  |        |

| Table A5-21 | Store single data item                                                   |        |

| Table A5-22 | Data-processing (shifted register)                                       |        |

| Table A5-23 | Move register and immediate shifts                                       |        |

| Table A5-24 | Data processing (register)                                               |        |

| Table A5-25 | Signed parallel addition and subtraction instructions                    |        |

| Table A5-26 | Unsigned parallel addition and subtraction instructions                  |        |

| Table A5-27 | Miscellaneous operations                                                 |        |

| Table A5-28 | Multiply, multiply accumulate, and absolute difference operations        |        |

| Table A5-29 | Long multiply, long multiply accumulate, and divide operations           |        |

| Table A5-30 | Coprocessor instructions                                                 |        |

| Table A6-1  | Data type specification flexibility                                      |        |

| Table A6-2  | Floating-point register specifier formats                                |        |

| Table A6-3  | Example register lists                                                   |        |

| Table A6-4  | Encoding of register numbers                                             |        |

| Table A6-5  | Three-register floating-point data-processing instructions               |        |

| Table A6-6  | Floating-point modified immediate constants                              |        |

| Table A6-7  | FP extension register load and store instructions                        |        |

| Table A6-8  | Instructions for 32-bit data transfers to or from FP extension registers | Ab-198 |

| Table A6-9  | 64-bit data transfer instructions                                     | A6-199 |

|-------------|-----------------------------------------------------------------------|--------|

| Table A7-1  | Condition codes                                                       |        |

| Table A7-2  | Effect of IT execution state bits                                     | A7-211 |

| Table A7-3  | Determination of mask field                                           | A7-278 |

| Table A7-4  | MOV (shift, register shift) equivalences)                             | A7-351 |

| Table B1-1  | Mode, privilege and stack relationship                                | B1-618 |

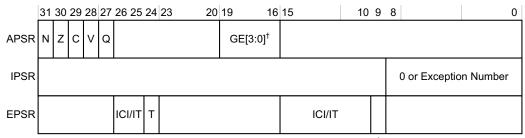

| Table B1-2  | ICI/IT bit allocation in the EPSR                                     | B1-626 |

| Table B1-3  | Mnemonics for combinations of xPSR registers                          | B1-626 |

| Table B1-4  | Exception numbers                                                     | B1-633 |

| Table B1-5  | Vector table format                                                   | B1-634 |

| Table B1-6  | Relation between number of priority bits and maximum priority value   | B1-636 |

| Table B1-7  | Priority grouping                                                     | B1-636 |

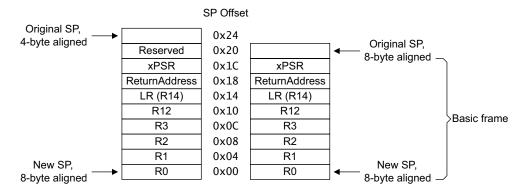

| Table B1-8  | EXC_RETURN definition of exception return behavior, no FP extension   | B1-653 |

| Table B1-9  | EXC_RETURN definition of exception return behavior, with FP extension | B1-653 |

| Table B1-10 | FP common register block                                              | B1-686 |

| Table B3-1  | ARMv7-M address map                                                   | B3-705 |

| Table B3-2  | Subdivision of the System region of the ARMv7-M address map           | B3-706 |

| Table B3-3  | SCS address space regions                                             | B3-708 |

| Table B3-4  | Summary of SCB registers                                              |        |

| Table B3-5  | Summary of additional SCB registers for the FP extension              | B3-711 |

| Table B3-6  | Summary of system control and ID register not in the SCB              |        |

| Table B3-7  | CPUID Base Register bit assignments                                   |        |

| Table B3-8  | ICSR bit assignments                                                  |        |

| Table B3-9  | VTOR bit assignments                                                  |        |

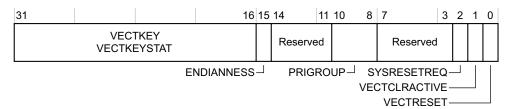

| Table B3-10 | AIRCR bit assignments                                                 |        |

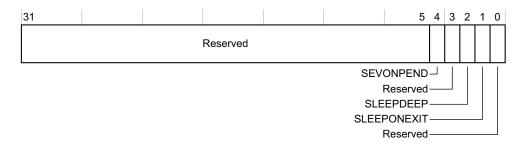

| Table B3-11 | SCR bit assignments                                                   |        |

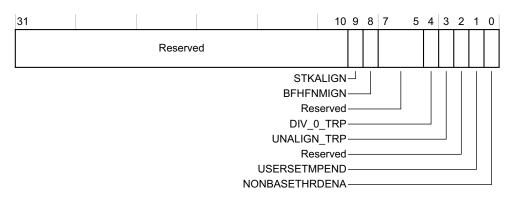

| Table B3-12 | CCR bit assignments                                                   |        |

| Table B3-13 | SHPR1 Register bit assignments                                        |        |

| Table B3-14 | SHPR2 Register bit assignments                                        |        |

| Table B3-15 | SHPR3 Register bit assignments                                        |        |

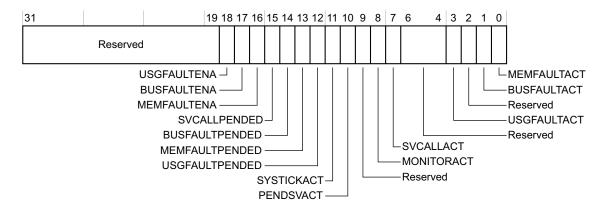

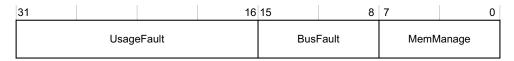

| Table B3-16 | SHCSR bit assignments                                                 |        |

| Table B3-17 | CFSR bit assignments                                                  |        |

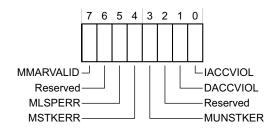

| Table B3-18 | MMFSR bit assignments                                                 |        |

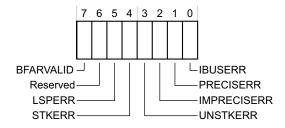

| Table B3-19 | BFSR bit assignments                                                  |        |

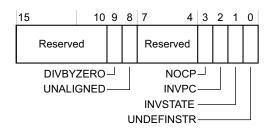

| Table B3-20 | UFSR bit assignments                                                  |        |

| Table B3-21 | HFSR bit assignments                                                  |        |

| Table B3-22 | MMFAR bit assignments                                                 |        |

| Table B3-23 | BFAR bit assignments                                                  |        |

| Table B3-24 | CPACR bit assignments                                                 |        |

| Table B3-25 | FPCCR bit assignments                                                 |        |

| Table B3-26 | FPCAR bit assignments                                                 |        |

| Table B3-27 | FPDSCR bit assignments                                                |        |

| Table B3-28 | ICTR bit assignments                                                  |        |

| Table B3-29 | STIR bit assignments                                                  |        |

| Table B3-30 | SysTick register summary                                              |        |

| Table B3-31 | SYST_CSR bit assignments                                              |        |

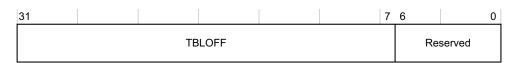

| Table B3-32 | SYST_RVR bit assignments                                              | B3-748 |

| Table B3-33 | SYST_CVR bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . B3-748 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table B3-34 | SYST_CALIB Register bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| Table B3-35 | NVIC register summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . B3-753 |

| Table B3-36 | Implemented NVIC registers, except NVIC_IPRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . B3-754 |

| Table B3-37 | Implemented NVIC_IPRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . B3-754 |

| Table B3-38 | NVIC_ISERn Register bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| Table B3-39 | NVIC_ICERn Register bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . B3-757 |

| Table B3-40 | NVIC_ISPRn Register bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . B3-758 |

| Table B3-41 | NVIC_ICPRn Register bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . B3-759 |

| Table B3-42 | NVIC_IABRx Register bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . B3-760 |

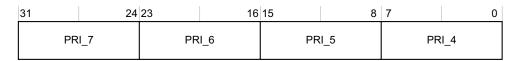

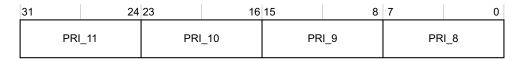

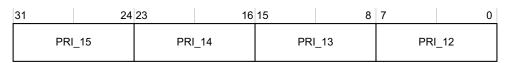

| Table B3-43 | NVIC_IPRx Register bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . B3-760 |

| Table B3-44 | MPU register summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| Table B3-45 | MPU_TYPE Register bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . B3-766 |

| Table B3-46 | MPU_CTRL Register bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| Table B3-47 | Effect of MPU_CTRL settings on unprivileged instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| Table B3-48 | MPU_RNR bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| Table B3-49 | MPU_RBAR bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . B3-771 |

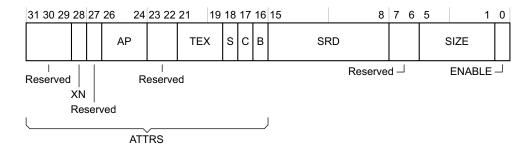

| Table B3-50 | MPU_RASR bit assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| Table B3-51 | TEX, C, B, and S Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| Table B3-52 | Cache policy encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| Table B3-53 | Access permissions field encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| Table B3-54 | Execute Never encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| Table B4-1  | Processor Feature ID register support in the SCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| Table B4-2  | Supported Synchronization Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| Table B5-1  | Special register field encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| Table B5-2  | <br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br> |          |

| Table C1-1  | PPB debug related regions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

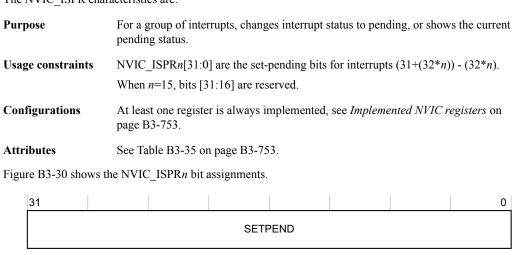

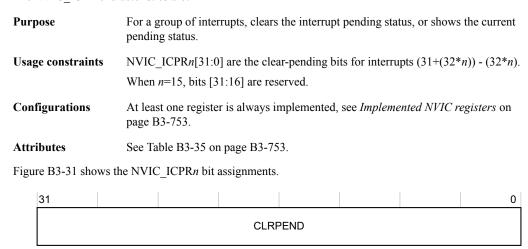

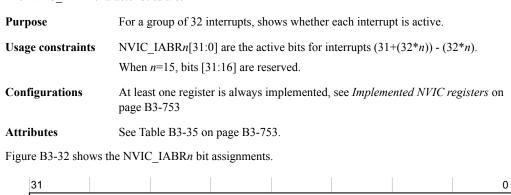

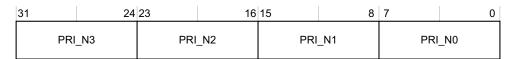

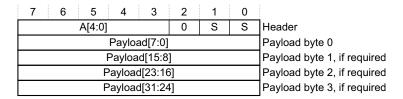

| Table C1-2  | Determining the debug support in an ARMv7-M implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |