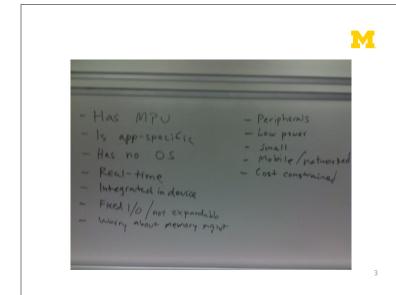

What is an embedded system?

\_

What is driving the embedded everywhere explosion?

#### Outline

## **Technology Trends**

**Design Questions**

Course Administrivia

Tools Overview/ISA Start

#

Outline

Technology Trends

Design Questions

Course Administrivia

Tools Overview/ISA Start

Why study 32-bit MCUs and FPGAs?

MCU-32 and PLDs are tied in embedded market share

Vesir

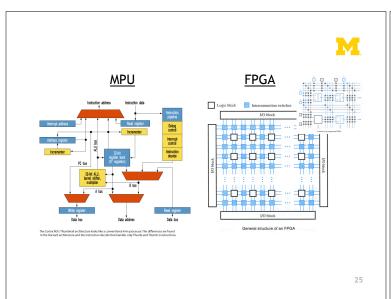

What distinguishes a Microprocessor from an FPGA?

M

22

24

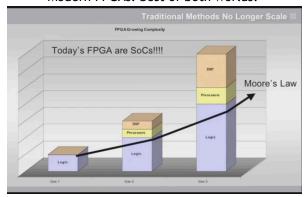

#### Modern FPGAs: best of both worlds!

Why study the ARM architecture (and the Cortex-M3 in particular)?

28

# Lots of manufacturers ship ARM products

# ARM is the big player

- ARM has a huge market share

- As of 2011 ARM has chips in about 90% of the world's mobile handsets

- As of 2010 ARM has chips in 95% of the smartphone market, 10% of the notebook market

- Expected to hit 40% of the notebook market in 2015.

- Heavy use in general embedded systems.

- Cheap to use

- ARM appears to get an average of 8¢ per device (averaged over cheap and expensive chips).

- Flexible

- Spin your own designs.

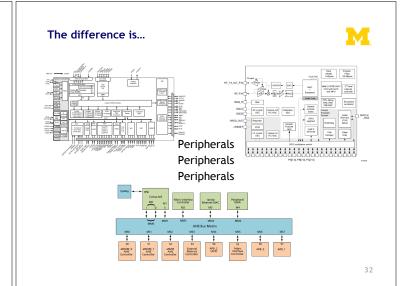

What differentiates these products from one another?

**Outline**

31

**Technology Trends**

**Design Questions**

Course Overview

Tools Overview/ISA Start

W'15 Instructional Staff (see homepage for contact info, office hours)

Matt

Smith

Lab Instructor

Prabal

Dutta

Instructor

Pat Pannuto GSI

John Connolly

Chris Fulara

Alex Laberge

Ryan Wooster

34

# My research interests

# Course goals

- Learn to implement embedded systems including hardware/software interfacing.

- Learn to design embedded systems and how to think about embedded software and hardware.

- Design and build non-trivial projects involving both hardware and software.

35

36

#### **Prerequisites**

- EECS 270: Introduction to Logic Design

- Combinational and sequential logic design

- Logic minimization, propagation delays, timing

- EECS 280: Programming and Intro Data Structures

- C programming

- Algorithms (e.g. sort) and data structures (e.g. lists)

- EECS 370: Introduction to Computer Organization

- Basic computer architecture

- CPU control/datapath, memory, I/O

- Compiler, assembler

37

#### **Topics**

- Memory-mapped I/O

- The idea of using memory addressed to talk to input and output devices.

- Switches, LEDs, hard drives, keyboards, motors

#### Interrupts

- How to get the processor to become "event driven" and react to things as they happen.

- · Working with analog signals

- The real world isn't digital!

- · Common peripheral devices and interfaces

- Serial buses, timers, etc.

38

#### Example: Memory-mapped I/O

- This is important.

- It means our software can tell the hardware what to do.

- In lab 3 you'll design hardware on an FPGA which will control a motor.

- But more importantly, that hardware will be designed so the software can tell the hardware exactly what to do with the motor. All by simply writing to certain memory locations!

- In the same way, the software can read memory locations to access data from sensors etc...

39

#### Example: Anatomy of a timer system Application Software Applications Operating System Timer Abstractions and Virtualization Low-Level Timer Subsystem Device Drivers Software R/W R/W R/W Counter Compare < Capture le timer(clr, ena, clk, alrm); put clr, ena, clk; Prescaler Clock Driver Internal External Xtal/Osc 1/0

# Grades

| ı cem             | weight |      |                     |     |        |

|-------------------|--------|------|---------------------|-----|--------|

| =====             |        |      | =                   |     |        |

| Labs (7)          | 25%    |      |                     |     |        |

| Project           | 25%    |      |                     |     |        |

| Exams             | 35%    | (15% | <pre>midterm;</pre> | 20% | final) |

| HW/Guest talks    | 10%    |      |                     |     |        |

| Oral presentation | 4%     |      |                     |     |        |

| Course Fraluation | 1 2    |      |                     |     |        |

Waiaht

- Project & Exams tend to be the differentiators

- Class median is generally a B+

# Time

- Assume you are going to spend a lot of time in this class.

- 2-3 hours/week in lecture (we cancel a few classes during project time)

- 8-12 hours/week working in lab

- Expect more during project time; some labs are a bit shorter.

- ~20 hours (total) working on homework

- $\sim$ 20 hours (total) studying for exams.

- ~8 hour (total) on your oral presentation

- Averages out to about 15-20 hours/week preproject and about 20 during the project...

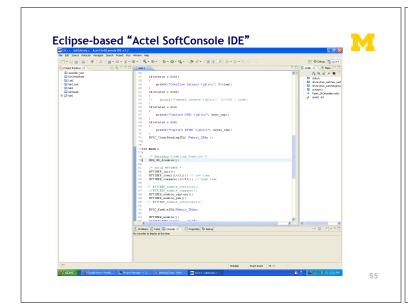

- This is more than we'd like, but we've chosen to go with state-of-the-art tools, and those generally have a steep learning curve.

#### Labs

- Start next week.

- 7 labs, 8 weeks, groups of 2

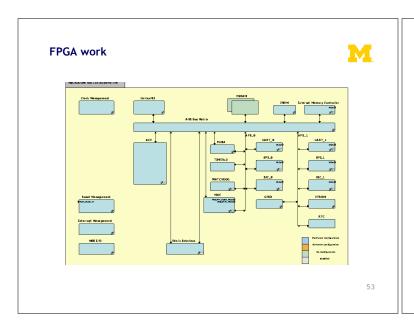

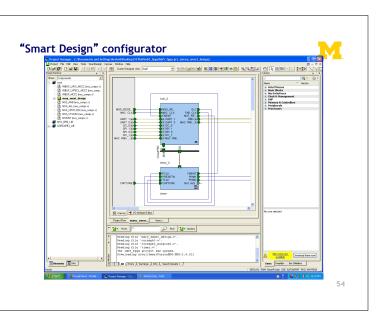

- 1. FPGA + Hardware Tools

- 2. MCU + Software Tools

- 3. Memory + Memory-Mapped I/O

- 4. Interrupts

- 5. Timers and Counters

- 6. Serial Bus Interfacing

- 7. Data Converters (e.g. ADCs/DACs)

- · Labs are very time consuming.

- As noted, students estimated 8-12 hours per lab with one lab (which varied by group) taking longer.

43

#### **Open-Ended Project**

- Goal: <u>learn how to build embedded systems</u>

- By building an embedded system

- Work in teams of 2 to 4

- You design your own project

- The major focus of the last third of the class.

- Labs will be done and we will cancel some lectures and generally try to keep you focused

- Important to start early.

- After all the effort in the labs, it's tempting to slack for a bit. The best projects are those that get going right away (or even earlier)

- Some project lead to undergraduate research

## Sample projects from F' 10 and their results

Energy-harvesting sensors → Sensys demo, IPSN paper, TI project, Master's thesis

Wireless AC Power Meter → SURE, IPSN demo, NSF GRFP, SenSys paper, Grad School

#### Letters of recommendation for graduate school

- · Grad school apps will require supporting letters

- Faculty write letters and read "coded" letters

- · Strong letters give evidence of research ability

- Strong letters can really help your case

- · Weak letters are vague and give class standing

- Weak letters are useless (or even worse)

- · Want a strong letter?

- Do well in this class

- Pull off an impressive project

- Continue class project as independent research in W' 15

46

# Homework

- Start TODAY!

- 4-5 assignments

- A few "mini" assignments

- · Mainly to get you up to speed on lab topics

- A few "standard" assignments

- Hit material we can't do in lab.

- Also a small part is for showing up to guest lectures

# Midterm and Final Exams

- Midterm (Tue, Feb 25, 2015 from 1:30pm-3:00pm)

- Emphasize problem solving fundamentals

- Final (Tue, Apr 28, 2015 from 4:00-6:00pm)

- Cumulative topics w/ experience of projects

- Some small amount of material from presentations

# Looking for me?

- Nominal Office Hours

- Time TBD in 4773 BBB

- Sometimes in lab sections

#### Outline

**Technology Trends**

**Design Questions**

Course Overview

Tools Overview/ISA Start

49 50

#

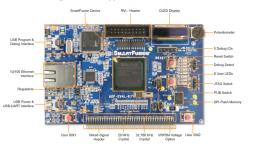

A2F200M3F-FGG484ES - 200,000 System FPGA

- 200,000 System FPGA gates, 256 KB flash memory, 64 KB SRAM, and additional distributed SRAM in the FPGA fabric and external memory controller

- Peripherals include Ethernet, DMAs, I<sup>2</sup>Cs, UARTs, timers, ADCs, DACs and additional analog resources

- $\bullet\ \ \mbox{USB}$  connection for programming and debug from Actel's design tools

- USB to UART connection to UART\_0 for HyperTerminal examples

- 10/100 Ethernet interface with on-chip MAC and external PHY

- Mixed-signal header for daughter card support