# The ARM Architecture

Ali Saidi

# **Agenda**

Introduction to ARM Ltd

ARM Architecture/Programmers Model

Data Path and Pipelines

System Design

Development Tools

## **ARM Ltd**

- Founded in November 1990

- Spun out of Acorn Computers

- Designs the ARM range of RISC processor cores

- Licenses ARM core designs to semiconductor partners who fabricate and sell to their customers.

- ARM does not fabricate silicon itself.

- Also develop technologies to assist with the designin of the ARM architecture

- Software tools, boards, debug hardware, application software, graphics, bus architectures, peripherals, cell libraries

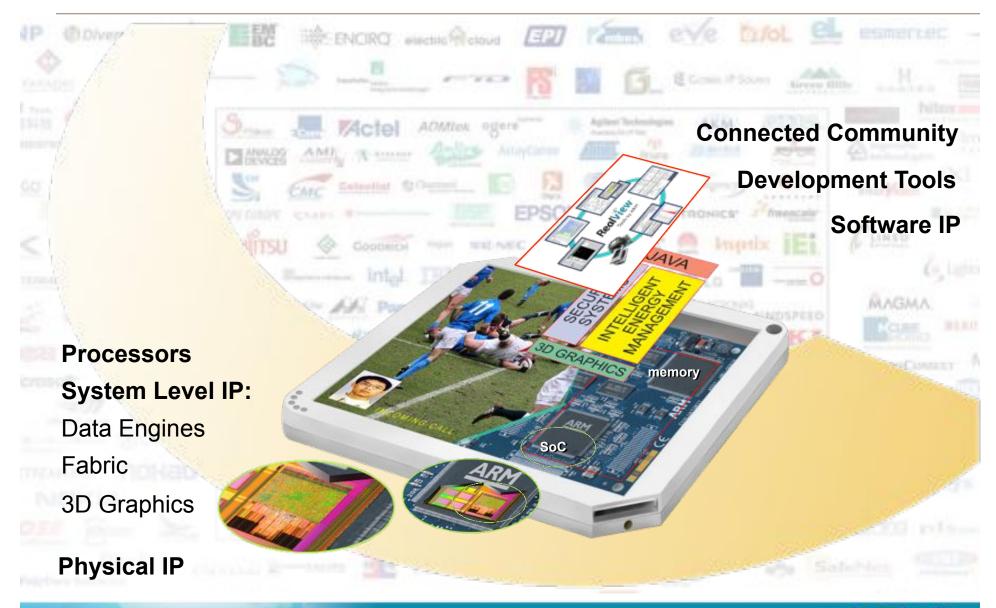

# The Architecture for the Digital World

ARM designs technology that lies at the heart of advanced digital products

## **ARM's Activities**

## **Product Areas**

Cortex-M0 toCortex-A9

180nm to 28nm

Compilers&OSprofiling

GPU to HD video

# **ARM Business Today**

Processor Shipped Last Year : ~4 Billion

Processor Shipped In Total : >24 Billion

Processor Licenses : 500+

Semiconductor Partners : 200+

Process Technology : 28 – 250 nm

Connected Community Members : 700+

## **ARM Business Model Drivers**

Deliver more functionality to the end-user sooner and more cost-effectively

- Integration

- Economics

- Focus

- Ecosystem

- Choice

- Power efficiency

# **Global Company**

## 700+

# Nokia N95 Multimedia Computer

#### **OMAP™ 2420**

#### **Applications Processor**

ARM1136™ processor-based SoC, developed using Magma ® Blast® family and winner of 2005 INSIGHT Award for 'Most Innovative SoC'

#### Symbian OS™ v9.2

Operating System supporting ARM processor-based mobile devices, developed using ARM® RealView® Compilation Tools

\$60 <sup>™</sup> 3<sup>rd</sup> Edition \$60 Platform supporting ARM processor-based mobile devices

Mobiclip™ Video Codec Software video codec for ARM processor-based mobile devices

#### **ST WLAN Solution**

Ultra-low power 802.11b/g WLAN chip with ARM9<sup>™</sup> processor-based MAC

Connect. Collaborate. Create.

# **ARM Processor Applications**

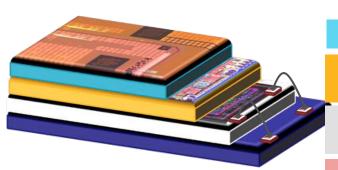

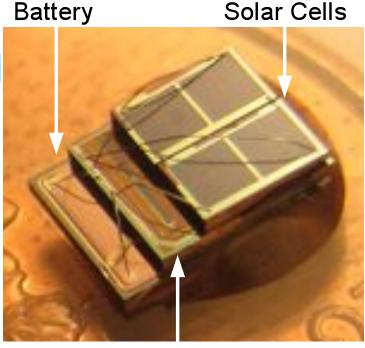

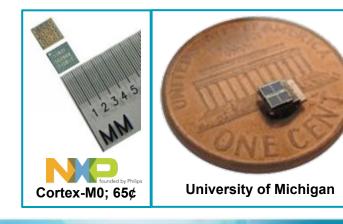

# World's Smallest ARM Computer?

Wireless Sensor Network

Sensors, timers

Cortex-M0 +16KB RAM 65nm UWB Radio antenna

10 kB Storage memory ~3fW/

12µAh Li-ion Battery

Processor, SRAM and PMU

Wirelessly networked into large scale sensor arrays

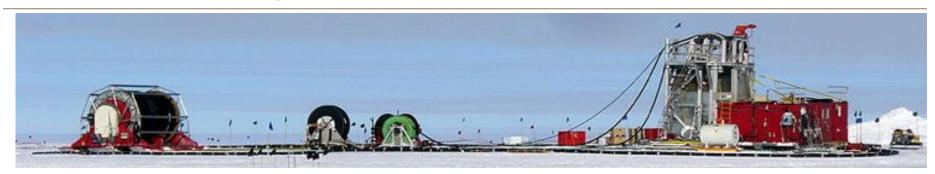

# World's Largest ARM Computer?

**4200 ARM powered Neutrino Detectors**

70 bore holes 2.5km deep

60 detectors per string starting 1.5km down 2.5km

1km³ of active telescope

Work supported by the National Science Foundation and University of Wisconsin-Madison

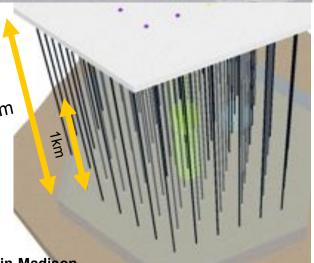

## From 1mm<sup>3</sup> to 1km<sup>3</sup>

## The Architecture for the Digital World

# **Agenda**

### Introduction to ARM Ltd

ARM Architecture/Programmers Model

Data Path and Pipelines

System Design

Development Tools

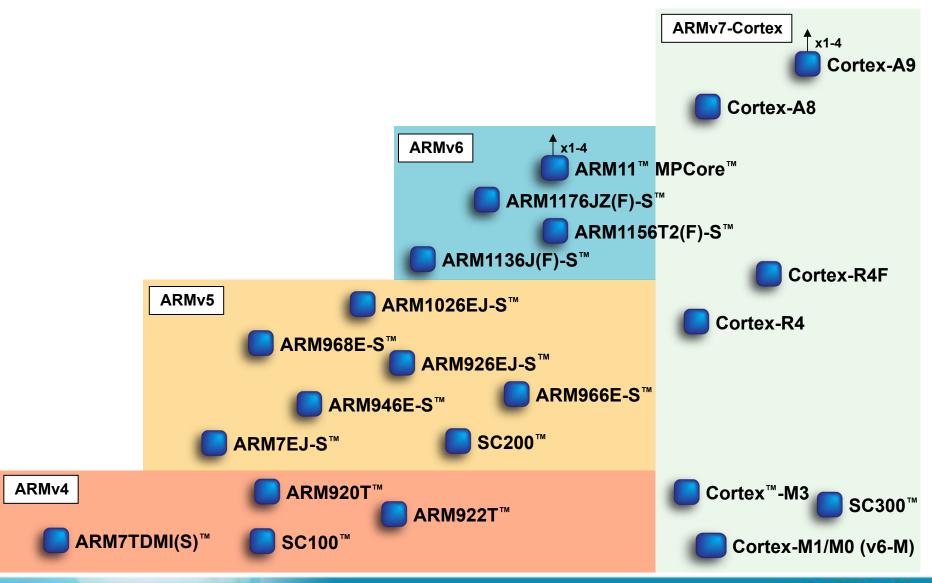

## **Architecture Versions**

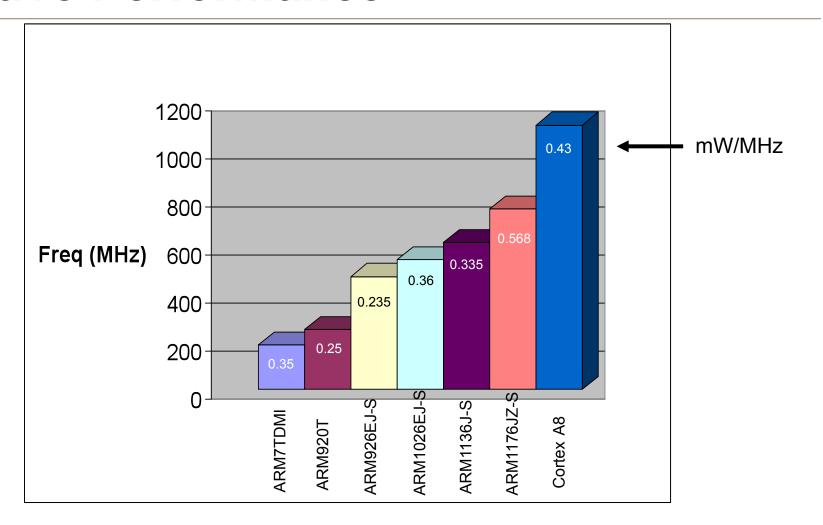

## **Relative Performance\***

<sup>\*</sup>Represents attainable speeds in 130, 90 or 65nm processes

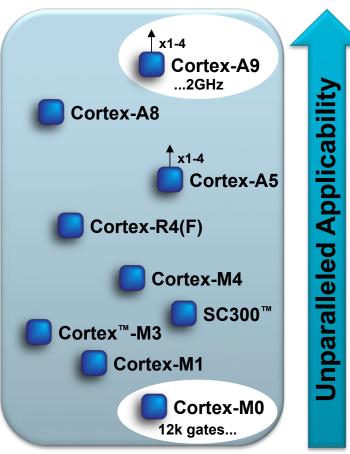

## **ARM Cortex Advanced Processors**

Architectural innovation, compatibility across diverse application spectrum

- ARM Cortex-A family:

- Applications processors for featurerich OS and 3<sup>rd</sup> party applications

- ARM Cortex-R family:

- Embedded processors for real-time signal processing, control applications

- ARM Cortex-M family:

- Microcontroller-oriented processors for MCU, ASSP, and SoC applications

## **Data Sizes and Instruction Sets**

- The ARM is a 32-bit architecture.

- When used in relation to the ARM:

- Byte means 8 bits

- Halfword means 16 bits (two bytes)

- Word means 32 bits (four bytes)

- Most ARM's implement two instruction sets

- 32-bit ARM Instruction Set

- 16-bit/32bit Thumb Instruction Set

- Jazelle cores can also execute Java bytecode

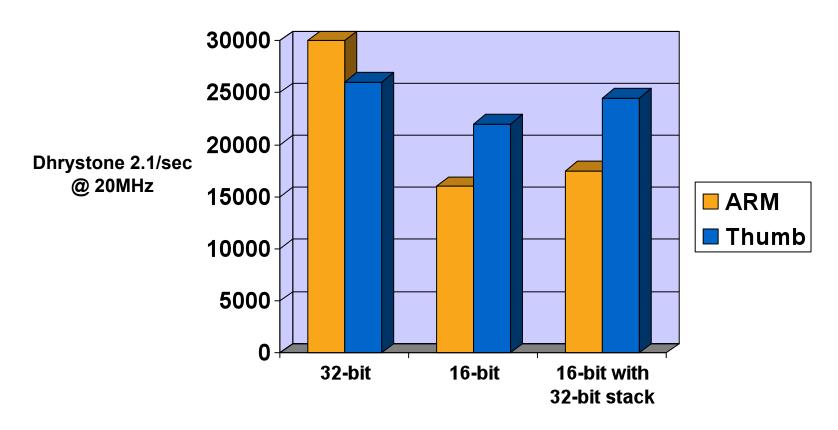

## **ARM** and Thumb Performance

**Memory width (zero wait state)**

## **Thumb-2 Instruction Set**

#### **EEMBC Analysis - Performance**

- Second generation of the Thumb architecture

- Blended 16-bit and 32-bit instruction set

- 25% faster than Thumb

- 30% smaller than ARM

- Increases performance but maintains code density

- Maximizes cache and tightly coupled memory usage

#### **EEMBC Analysis - Code Size**

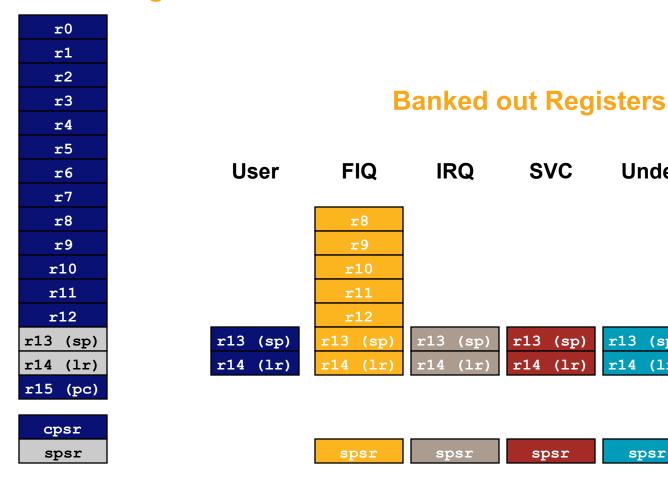

## **Processor Modes – A Class**

- The ARM has seven basic operating modes:

- User: unprivileged mode under which most tasks run

- FIQ: entered when a high priority (fast) interrupt is raised

- IRQ : entered when a low priority (normal) interrupt is raised

- Supervisor : entered on reset and when a Software Interrupt instruction is executed

- Abort : used to handle memory access violations

- Undef: used to handle undefined instructions

- System: privileged mode using the same registers as user mode

# The ARM Register Set

### **Current Visible Registers**

#### **Abort Mode**

Undef

r13 (sp)

r14 (lr)

spsr

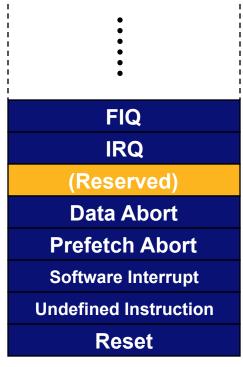

# **Exception Handling**

- When an exception occurs, the ARM:

- Copies CPSR into SPSR <mode>

- Sets appropriate CPSR bits

| Change to ARM or Thumb state | 0x1C |

|------------------------------|------|

|------------------------------|------|

- Change to exception mode

- Disable interrupts (if appropriate) <sub>0x10</sub>

- Stores the return address in LR\_<mode> 0x0C

- Sets PC to vector address

- To return, exception handler needs to: 0x04

- Restore CPSR from SPSR\_<mode>

- Restore PC from LR\_<mode>

#### **Vector Table**

Vector table can be at 0xFFFF0000 on ARM720T and on ARM9/10 family devices

0x18

0x14

80x0

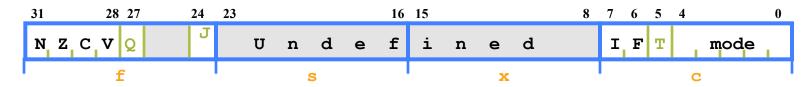

# **Program Status Registers**

- Condition code flags

- N = Negative result from ALU

- Z = Zero result from ALU

- C = ALU operation Carried out

- V = ALU operation oVerflowed

- Sticky Overflow flag Q flag

- Architecture v5+ only

- Indicates if saturation has occurred

- J bit

- Architecture v5+ only

- J = 1: Processor in Jazelle state

- Interrupt Disable bits.

- I = 1: Disables the IRQ.

- F = 1: Disables the FIQ.

- T Bit

- Architecture v5+ only

- T = 0: Processor in ARM state

- T = 1: Processor in Thumb state

- Mode bits

- Specify the processor mode

# **Conditional Execution and Flags**

- ARM instructions can be made to execute conditionally by postfixing them with the appropriate condition code field.

- This improves code density and performance by reducing the number of forward branch instructions.

```

CMP r3,#0

BEQ skip

ADD r0,r1,r2

skip

```

- Why was this developed?

- When would you want to use it? Always? Any downsides?

# **Agenda**

# Introduction to ARM Ltd ARM Architecture/Programmers Model

Data Path and Pipelines

System Design

Development Tools

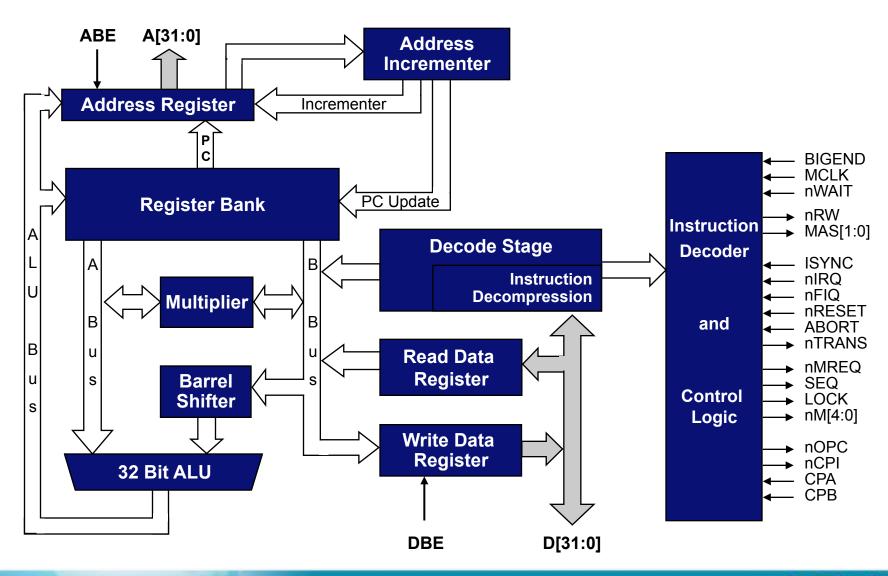

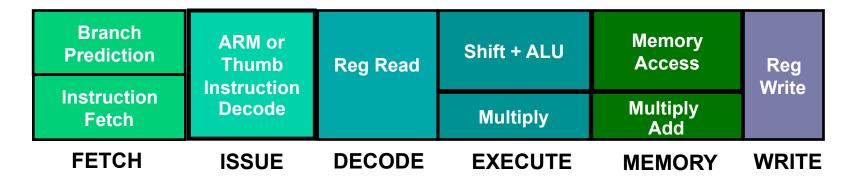

## The ARM7TDM Core

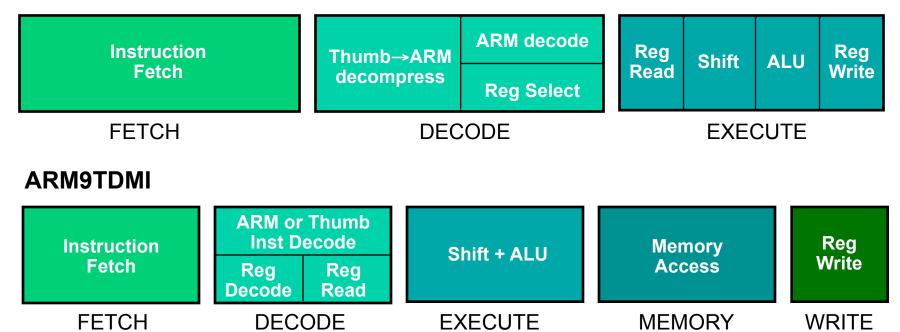

# Pipeline changes for ARM9TDMI

#### **ARM7TDMI**

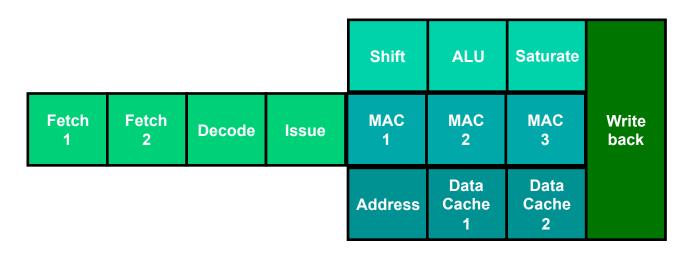

# ARM10 vs. ARM11 Pipelines

### ARM10

### ARM11

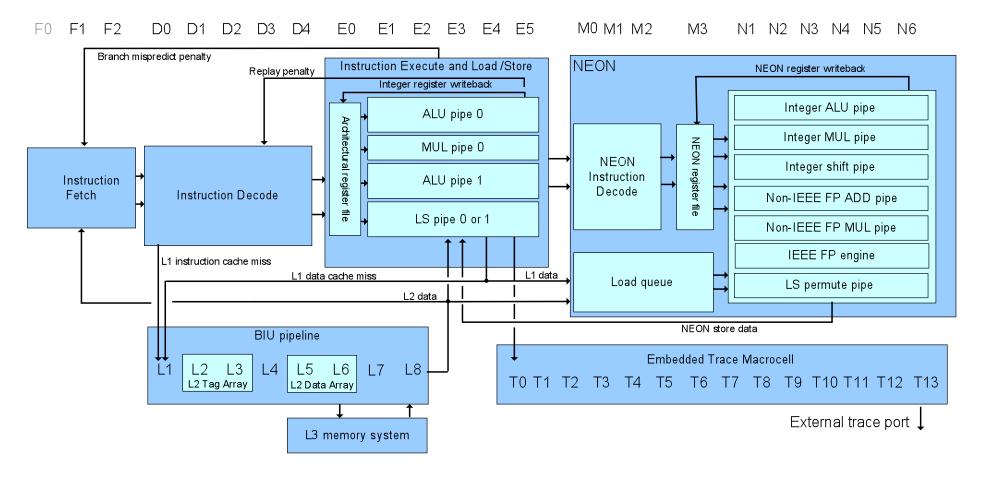

# Full Cortex-A8 Pipeline Diagram

#### 13-Stage Integer Pipeline

#### 10-Stage NEON Pipeline

# **Agenda**

Introduction to ARM Ltd

ARM Architecture/Programmers Model

Data Path and Pipelines

System Design

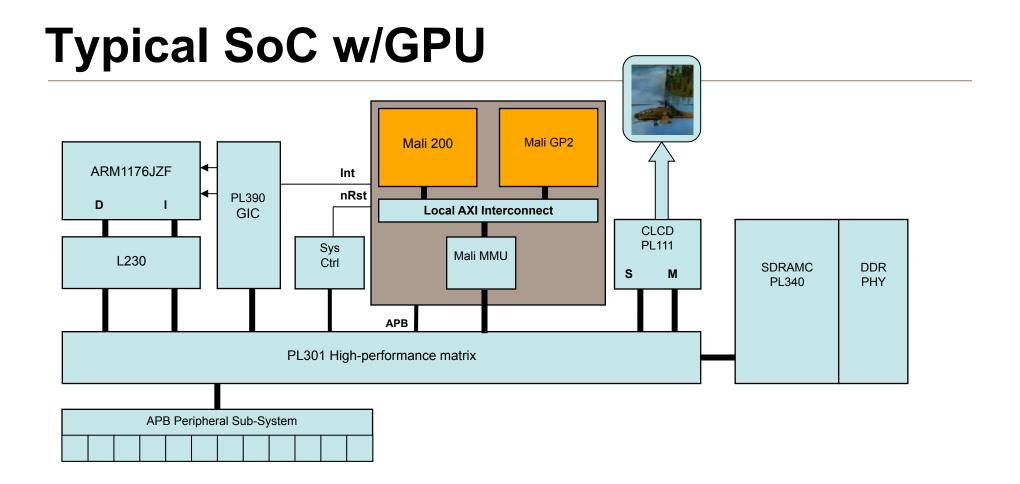

**Development Tools**

- Designed and optimised for AMBA: provides easier integration with ARM cores and fabric IP

- Unified Memory Architecture

# **Agenda**

Introduction to ARM Ltd

ARM Architecture/Programmers Model

Data Path and Pipelines

System Design

Development Tools

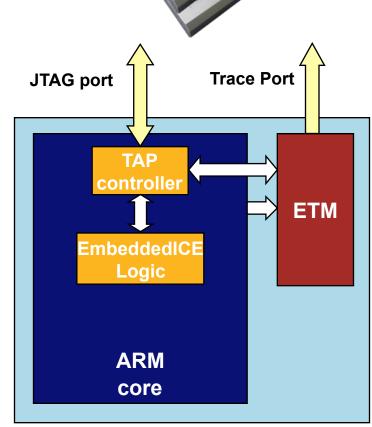

# **ARM Debug Architecture**

Debugger (+ optional trace tools)

- EmbeddedICE Logic

- Provides breakpoints and processor/system access

- JTAG interface (ICE)

- Converts debugger commands to JTAG signals

- Embedded trace Macrocell (ETM)

- Compresses real-time instruction and data access trace

- Contains ICE features (trigger & filter logic)

- Trace port analyzer (TPA)

- Captures trace in a deep buffer

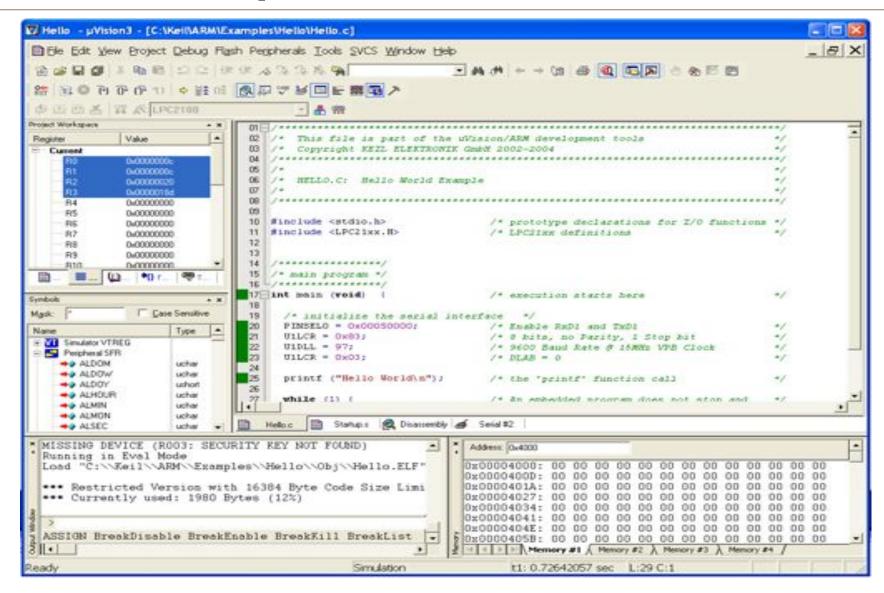

# Keil Development Tools for ARM

- Includes ARM macro assembler, compilers (ARM RealView C/C++ Compiler, Keil CARM Compiler, or GNU compiler), ARM linker, Keil uVision Debugger and Keil uVision IDE

- Keil uVision Debugger accurately simulates on-chip peripherals (I<sup>2</sup>C, CAN, UART, SPI, Interrupts, I/O Ports, A/D and D/A converters, PWM, etc.)

- Evaluation Limitations

- 16K byte object code + 16K data limitation

- Some linker restrictions such as base addresses for code/constants

- GNU tools provided are not restricted in any way

- http://www.keil.com/demo/

# **Keil Development Tools for ARM**

# **University Resources**

http://www.arm.com/support/university/

University@arm.com

# Fin