The Design & Implementation of Modular Smart Dust

by

Patrick William Pannuto

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Associate Professor Prabal K. Dutta, Chair Professor Kristofer S. J. Pister Professor David E. Culler Taisei Professor Khalid M. Mosalam

Fall 2020

## The Design & Implementation of Modular Smart Dust

Copyright 2020 by Patrick William Pannuto

#### Abstract

The Design & Implementation of Modular Smart Dust

by

#### Patrick William Pannuto

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Science

University of California, Berkeley

Associate Professor Prabal K. Dutta, Chair

Advancements across the computing stack now allow the realization of self-contained, sensing, computing, and communication devices in less than a cubic millimeter of volume—Smart Dust. Today's millimeter-scale systems are often one-offs, however. They are built to prove they can be built or for one particular application, but they are not yet so numerous and diverse to satisfy the vision of ubiquitous, ambient intelligence. This work aims to identify and address challenges in the move from tens to tens of millions of Smart Dust computing systems.

The core contribution of this dissertation is bringing modularity to the millimeter-scale computing class. Much of the rich panoply of conventional systems is driven not by the diversity of individual chips alone but by the number of different ways in which they can be synthesized into novel designs. Composition-oriented design of systems is enabled in part by the interconnect technologies that lie between components. This dissertation identifies the limitations of extant interconnect technologies for the millimeter-scale computing class and then designs, implements, and evaluates a new interconnect bus and interconnect protocol that enables composable Smart Dust systems. As a final contribution, this dissertation shows how this same interconnect can be leveraged to support key operations for bringup and deployment of Smart Dust systems, in particular programming and debugging.

Updates and errata to this dissertation can be found at: patpannuto.com/dissertation

To all the Dreamers and Builders:

Go make something cool.

## Contents

| Co  | nten                                           | uts                             | ii                              |

|-----|------------------------------------------------|---------------------------------|---------------------------------|

| Lis | st of                                          | Figures                         | iv                              |

| Lis | st of                                          | Tables                          | viii                            |

| 1   | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | Classes of Computing            | 1<br>2<br>3<br>4<br>6<br>8<br>8 |

| 2   | The 2.1 2.2 2.3                                | Case for a New Bus Related Work | 10<br>10<br>15<br>20            |

| 3   | MB<br>3.1<br>3.2<br>3.3<br>3.4                 | MBus Physical Design            | 21<br>24<br>29<br>33            |

| 4   | Bui<br>4.1<br>4.2<br>4.3<br>4.4                | A Standard Scaffolding          | 34<br>39<br>44<br>55            |

| 5   |                                                | M3 Implementation Overview      | <b>57</b>                       |

|    |                          |                                                                         | iii                  |  |  |

|----|--------------------------|-------------------------------------------------------------------------|----------------------|--|--|

|    | 5.2<br>5.3<br>5.4        | RTL Design                                                              | 57<br>65<br>73       |  |  |

| 6  | Deb<br>6.1<br>6.2<br>6.3 | ugging & Bringup   M-ulator & ICE   Encapsulated Interactions   Summary | 74<br>74<br>84<br>86 |  |  |

| 7  | Con                      | clusion                                                                 | 87                   |  |  |

| Bi | Bibliography             |                                                                         |                      |  |  |

# List of Figures

| 1.1 | Examples of Smart Dust systems. Three millimeter-scale sensing systems                            |    |

|-----|---------------------------------------------------------------------------------------------------|----|

|     | composed using the modularity and system design principles outlined in this                       |    |

|     | dissertation                                                                                      | 1  |

| 1.2 | Bell's Law for the birth and death of computer classes. This figure is                            |    |

|     | a reproduction of the trends identified by Gordon Bell [18, 19]. Summarized,                      |    |

|     | Bell observes that steady year-over-year technological advancements allow for (1)                 |    |

|     | improved performance at fixed cost, (2) lower cost for fixed performance, or (3)                  |    |

|     | greater overall capability. Roughly every decade, however, an amalgamation of                     |    |

|     | advancements come together to allow for (4) a greater-than-iterative change that                  |    |

|     | result in the creation of a new "class" of computing                                              | 2  |

| 1.3 | Corollary to Bell's Law: Roughly every decade, general-purpose com-                               |    |

|     | puting grows an order of magnitude smaller. In each case, the new class                           |    |

|     | of computing is foretold by one or a few instances made a decade earlier, which                   |    |

|     | proves such machines are possible. This dissertation looks at what is needed to                   |    |

|     | move the millimeter-scale computer class from possible to prevalent, with an eye                  |    |

|     | towards the even smaller systems to come.                                                         | 3  |

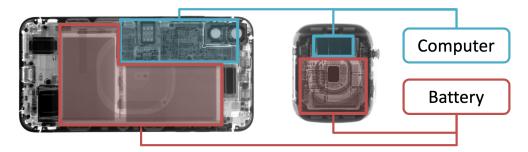

| 1.4 | Looking inside modern computing devices. Energy storage technologies are                          |    |

|     | not shrinking at the same rate as computing. As a result, as computing devices                    |    |

|     | get smaller, a larger proportion of their volume is dedicated to energy storage.                  | 6  |

| 2.4 |                                                                                                   |    |

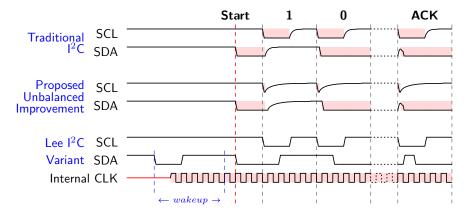

| 2.1 | Waveforms of I <sup>2</sup> C and variants. A comparison of traditional I <sup>2</sup> C and some |    |

|     | of the proposed variations. Shaded areas are power-expensive protocol elements.                   | 11 |

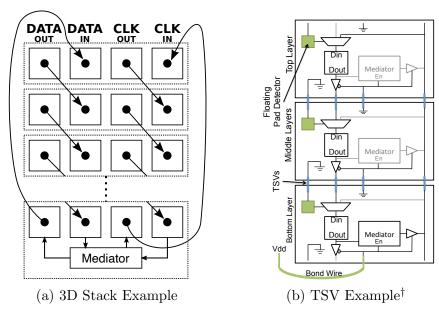

| 3.1 | MBus topology. An MBus system consists of a mediator node and one or more                         |    |

| -   | member nodes connected in two "shoot-through" rings. The ring topology adapts                     |    |

|     | to many system synthesis methods, such as stepped 3D-stacking with wirebonding                    |    |

|     | (a) and TSVs (b)                                                                                  | 22 |

| 3.2 | Conceptual frontend. A simplified view of the MBus frontend. The default                          |    |

|     | configuration "shoots-through" DATA and CLK signals. Note that there are no local                 |    |

|     | clocks or buffers (beyond generic I/O buffers and drivers) in the MBus ring                       | 23 |

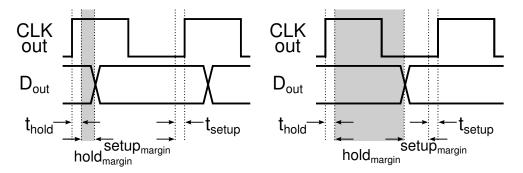

| 3.3 | Setup and hold time diagram. Conventional positive-edge triggering is shown                       |    |

|     | on the left while the balanced MBus clocking is shown on the right                                | 23 |

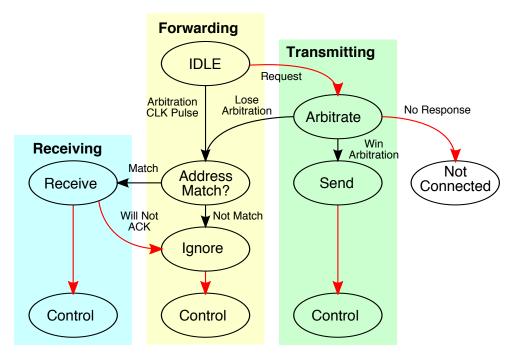

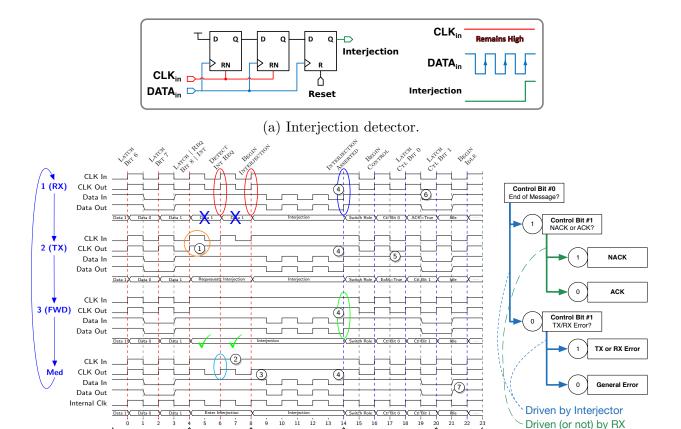

| 3.4 | High-level behavior of MBus nodes. MBus nodes are normally idle. A transaction begins when one or more nodes elect to transmit by starting an arbitration phase (§Arbitration). The winner then transmits a destination address (§Addressing, §Address Assignment), sends payload data (§Data Transmission), and interjects to end the transaction (§Message Termination). Black arrows are synchronous, transitions that match MBus CLK edges, while red arrows are asynchronous. By leveraging the interjection primitive, MBus transmitters can reliably signal the end of message without requiring an embedded length or an out-of-band—extra wire—signal. Not shown are arrows from any state to control |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

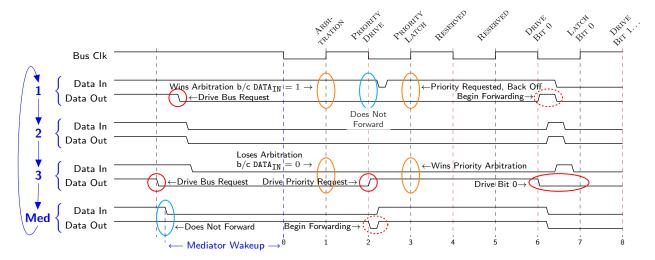

| 3.5 | due to interjections and from control back to idle.  MBus arbitration. To begin a transaction, one or more nodes pull down on DATA <sub>OUT</sub> . This shows node 1 and node 3 requesting the bus at nearly the same time (node 1 shortly after node 3). Node 1 initially wins arbitration, but node 3 uses the priority arbitration cycle to claim the bus. The propagation delay of the data line between nodes is exaggerated to show the shoot-through nature of MBus. Momentary glitches caused by nodes transitioning from driving to forwarding are                                                                                                                                                   | 24 |

| 3.6 | resolved before the next rising clock edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25 |

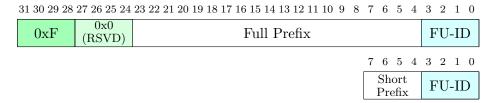

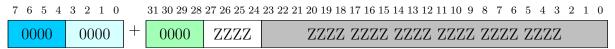

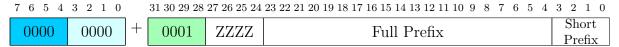

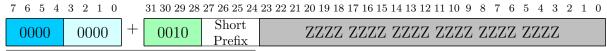

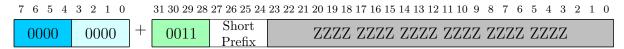

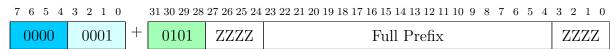

| 3.7 | that identifies a full address and 0x0 indicates a broadcast message. This allows up to fourteen nodes per instance to be address by their short prefix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26 |

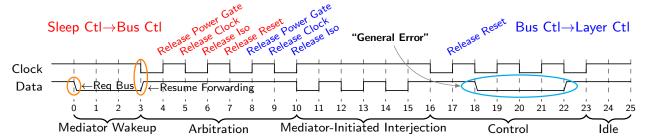

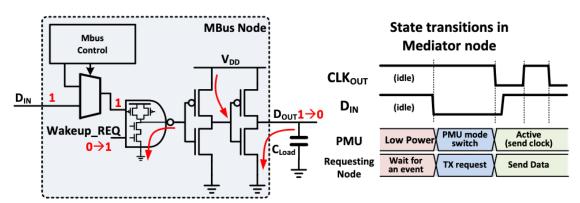

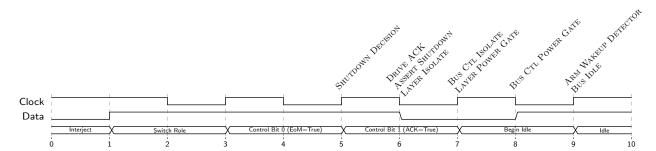

| 3.8 | followed by a two-cycle control sequence that defines why the interjection occurred.  MBus wakeup. Instead of requiring every node to include custom cold-boot circuitry, MBus provides a mechanism to wake a node in response to a single falling edge. The design further considers system-wide power management, with affordance for regulator intervention and update before allowing system components                                                                                                                                                                                                                                                                                                    | 28 |

| 3.9 | to power on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32 |

|     | Controller is waiting for the next wakeup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33 |

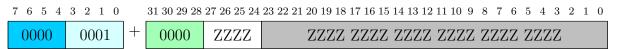

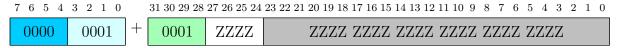

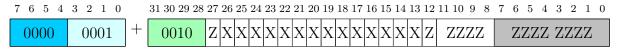

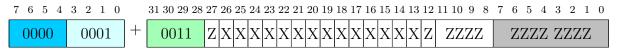

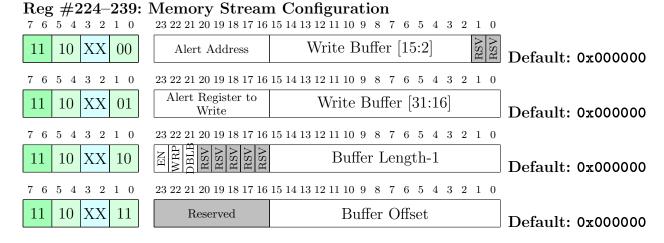

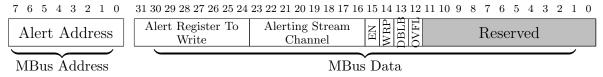

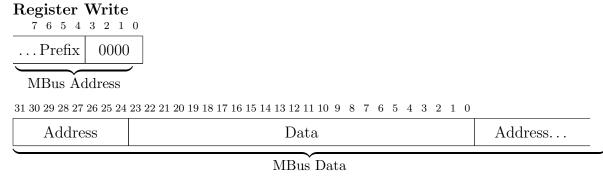

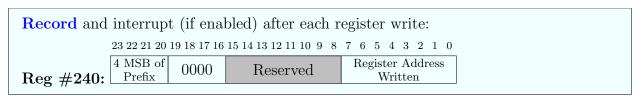

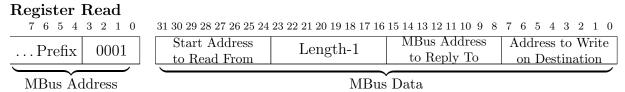

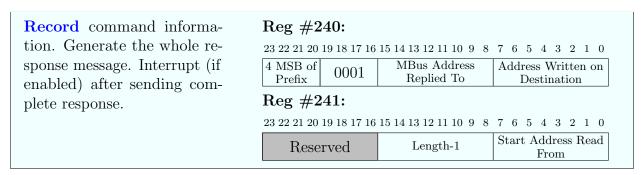

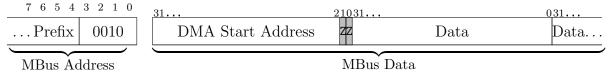

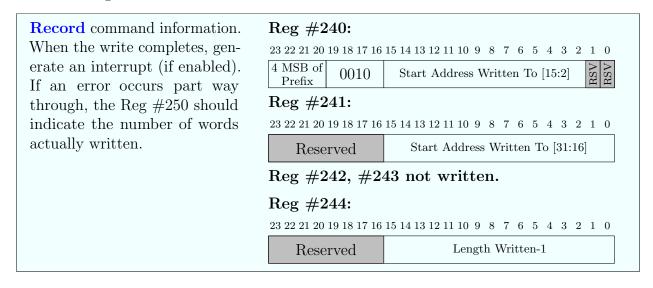

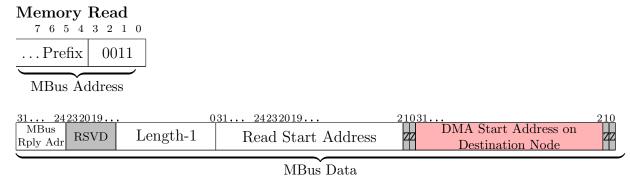

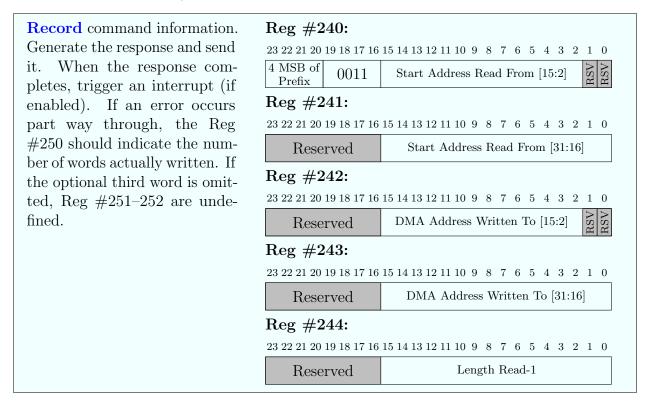

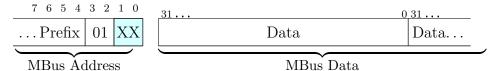

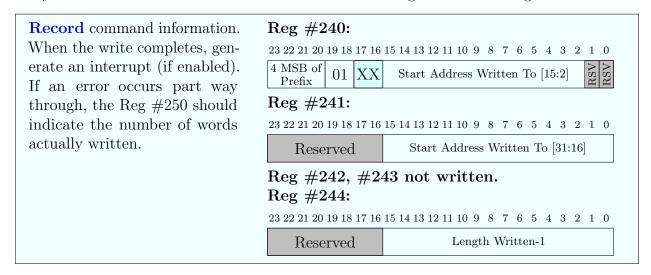

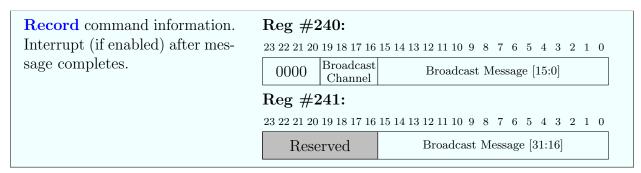

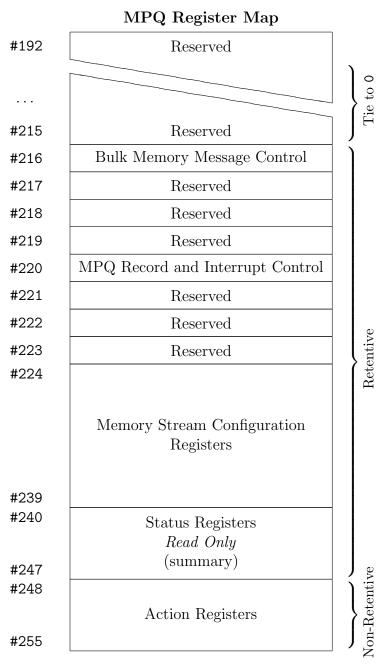

| 4.1 | MPQ register map. MPQ defines a portion of the register space for its own operation. This standard interface allows portable software libraries and remote DMA operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

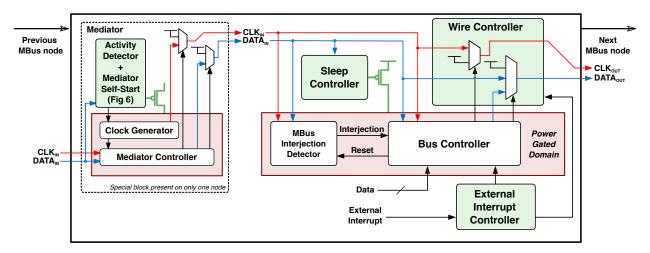

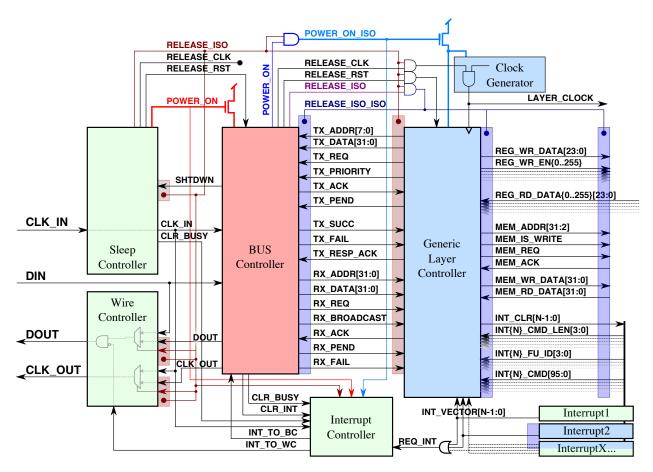

| 5.1 | MBus implementation. MBus is implemented as a series of composable Verilog modules. The module coloring represents the three hierarchical power domains: green modules (Sleep, Wire, and Interrupt Controllers) are always powered on, red modules (Bus Controller) are powered during MBus transactions, and blue modules (Layer Controller, Local Clock) are powered only when the node is active. Critically, MBus itself requires no local oscillator. The generic Layer Controller implements and provides a simple, consistent register/memory interface for a node. The isolate (ISO) signals ensure that floating signals from power-gated blocks remain at stable defaults. Systems that do not perform power-gating omit these isolation gates and all of the green blocks                    | 58 |

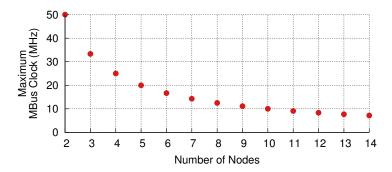

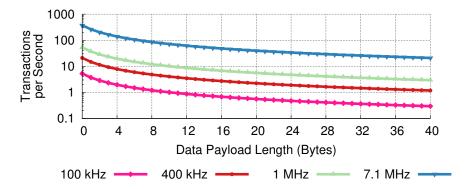

| 5.2 | Maximum frequency. MBus peak clock frequency is inversely proportional to the number of nodes. MBus limits node-to-node propagation delay to 10 ns. For the maximum of 14 short-addressed nodes, MBus could support a 7.1 MHz bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|     | clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

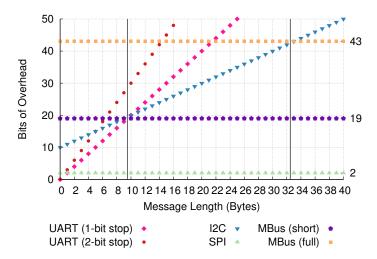

| 5.3 | <b>Bus overhead.</b> MBus message overhead is independent of message length. MBus short-addressed messages become more efficient than 2-mark UART after 7 bytes and more efficient than I <sup>2</sup> C and 1-mark UART after 9 bytes. MBus scales efficiently                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|     | to messages such as 28.8 kB images (Section 5.3) or longer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67 |

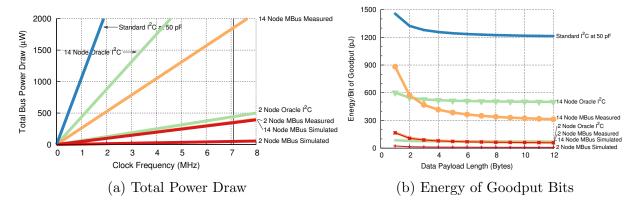

| 5.4 | Energy comparisons. First, (a) compares the power draw of various bus configurations as clock frequency and node population increase. It finds that both simulated and measured MBus outperforms the simulated Oracle I <sup>2</sup> C, which itself outperforms standard I <sup>2</sup> C. Then, (b) examines MBus overhead by computing the energy per bit for each bit of goodput, actual data bits that amortize protocol overhead. The simulated MBus outperforms the simulated Oracle I <sup>2</sup> C for all payload lengths. The measured MBus reveals that MBus efficiency suffers for short (1–2 byte) messages and that systems should attempt to coalesce messages if possible. In both figures, the measured values are based on empirical measurements of the 3-node temperature sensor. | 69 |

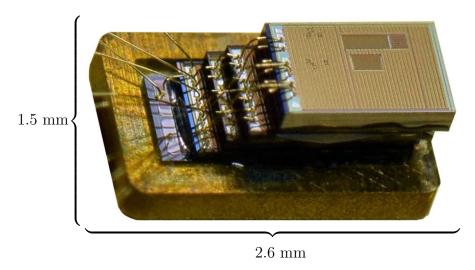

| 5.5 | Temperature sensing system. A system designed as part of the Michigan Micro Mote project consisting of a 2 μAH battery, a 900 MHz near-field radio, an ARM Cortex M0 processor, and an ultra-low power temperature sensor, interconnected using MBus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70 |

| 5.6 | Motion detection and imaging system. (a) An imager made of a 900 MHz near-field radio, a 5 μAH battery, an ARM Cortex M0, and a 160 × 160 pixel, 9-bit grayscale imager with ultra-low power motion detection all connected using MBus. (b) A full-resolution (28.8 kB) image that was transferred by MBus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71 |

| 5.7 | Saturating transaction rate. As a shared medium, MBus can only support a finite number of transactions across all member nodes. The peak transaction rate depends on the transaction size and bus clock speed.                                                                                                                                                                                                        | 72 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

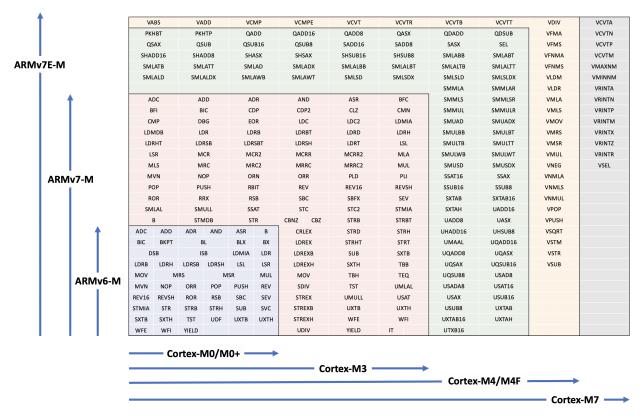

| 6.1 | The ARM microcontroller-class ISA hierarchy The ARM ISA exposes a wide tradeoff space across complexity and capability for CPU designers. The simplest cores facilitate basic data processing and peripheral control tasks. Progressively more advanced cores add support for more advanced data processing,                                                                                                          |    |

|     | complex bit field manipulations, SIMD, and floating point operations                                                                                                                                                                                                                                                                                                                                                  | 76 |

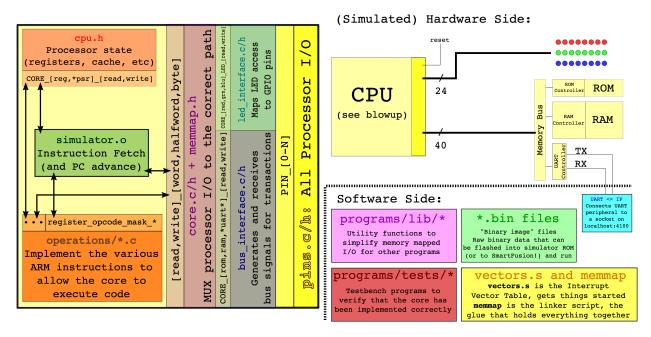

| 6.2 | <b>High-level design of M-ulator.</b> The architecture of M-ulator mirrors that of real hardware. This allows for runtime modularity, where individual components can be implemented either via software emulation or as pass-throughs to real hardware. It further serves a pedagogical goal, as it allows laboratory and project work to explore and implement normally tightly-integrated components in isolation. | 80 |

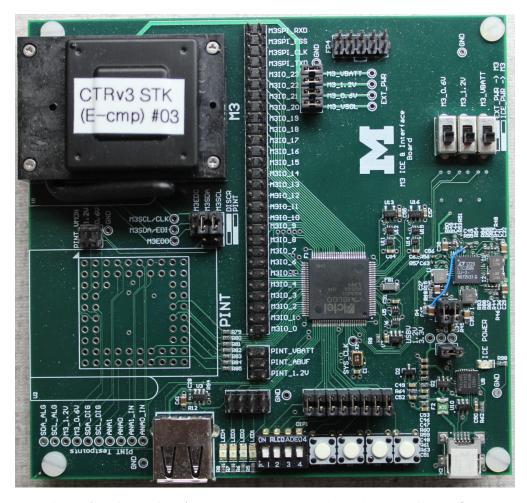

| 6.3 | The ICE board. A custom hardware board that allows flexible hardware access. It supports both traditional in-circuit emulation tasks as well as more general purpose debugging and programming of arbitrary hardware in the greater M3                                                                                                                                                                                |    |

|     | Smart Dust ecosystem                                                                                                                                                                                                                                                                                                                                                                                                  | 82 |

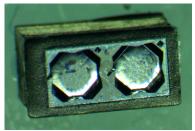

| 6.4 | A pressure sensor encapsulated in bio-compatible epoxy. Deployment considerations for Smart Dust systems limit the capacity to physically interface                                                                                                                                                                                                                                                                   |    |

|     | with devices                                                                                                                                                                                                                                                                                                                                                                                                          | 84 |

## List of Tables

| 2.1 | <b>Feature comparison matrix.</b> Population-independent area, ultra-low power     |    |

|-----|------------------------------------------------------------------------------------|----|

|     | operation, synthesizability, an area-free global namespace, and interrupt support  |    |

|     | are fundamental requirements for a general purpose Smart Dust interconnect.        |    |

|     | Standby power is on the order of 100's of pW and active power ranges from 10's     |    |

|     | of $\mu W$ to 10's of nW.                                                          | 15 |

| 5.4 | Size of MBus components. Non power-gated designs require only the Bus              |    |

|     | Controller. The MBus values are from the temperature sensor chip in Figure 5.5.    |    |

|     | To support its additional features and lower power, MBus incurs a modest increase  |    |

|     | in area                                                                            | 66 |

| 5.5 | Measured MBus power draw. As supplies for MBus modules are not broken              |    |

|     | out, their power draw cannot be directly measured. Instead, this uses differential |    |

|     | system states, which measures how much total system power draw changes when        |    |

|     | various MBus operations are active, to capture an estimate of the power draw for   |    |

|     | MBus. Forwarding nodes reduce switching activity by not clocking flops in their    |    |

|     | receive buffer. The mediator is integrated as a block in the processor and cannot  |    |

|     | be isolated.                                                                       | 68 |

### Acknowledgments

To Family, John, Linda, Steve, and Julie Pannuto: It is an incredible and in some ways indescribable privilege to have and to know that you have a backstop of an endless well of unquestioning love and support. Thank you for your infinite patience, especially in the many times in this process that I disappeared without notice, and for the steadfast help and support every time I came back. I cannot imagine life without you.

To Friends: To Haven Moore, who somehow found himself by my side (and cleaning my kitchen) in both the first and last days of this adventure, as well as so many in between—thank you for so often knowing what I needed, even when I did not. To Lauren Leader, for patience, love, and support, for someday teaching me how to get things done in the right order, and for so much more of our life yet to come. And to Bill Grier, Jill Grier, James Huebschman, Jacob Wimmer, Erin Wimmer, Brian Roberts, Tyler Sanderson, John Krzemien, and Shazil Naqvi, for being some of the best friends anyone could ever possibly ask for—here's to a lifetime together.

To the People and Friends of Lab11: In many ways, a Ph.D. is defined by the people you spend it with, and I could not be more grateful to have spent my time with all of you. Thank you to Brad Campbell, Zakir Durumeric, Noah Klugman, and David Adrian, my partners in every part of graduate life that does not make it into a dissertation. Thank you to all those in Lab11, those who came early and helped to build an incredible institution, especially Thomas Schmid and Aaron Shalev, those who I spent so many years with, Ye-Sheng Kuo, Ben Kempke, Sam DeBruin, Will Huang, Meghan Clark, Branden Ghena, Rohit Ramesh, and Thomas Zachariah, those to whom we pass on the legacy, Joshua Adkins, Neal Jackson, Matt Podolsky, Jean-Luc Watson, Shishir Patil, and all those yet to come.

To the Michigan Micro Mote team: What an incredible thing to have built. Thank you for letting me share in the journey and contribute a small part of it. Thank you especially to ZhiYoong Foo, Yoonmyung Lee, and Gyouho Kim for all of the long and late hours getting things working, your patience and lessons in all of the electrical engineering that I did not know, and for being my friend. And thank you to David Blaauw, for meeting an eager undergraduate at a Borders over Christmas, for later believing in and betting on their ideas in a whole lot of silicon, and for the staunch support as my career began to bloom.

To my Teachers and Mentors along the way: I think you are allowed some indulgences in the acknowledgements section of a dissertation. I remember nearly every teacher I have ever had, from Kindergarten through my final graduate course, in what was perhaps the 24th grade. I suspect I think of at least one former teacher nearly every day of my life, for any number of reasons. I am too afraid of regretting an omission to try list every one here, but I would like to try to thank many of the people who have made me who I am today:

I am a teacher because of my second grade teacher, Mrs. Schroeder.

I am in STEM because of my third grade teacher, Mrs. Smith.

I am a much better teacher because of my fifth grade teacher, Mrs. Boswell.

I am a computer scientist because of my ninth grade math teacher, Mr. Lamkin.

I am an engineer becuase of my FIRST mentors, Mr. Hildebrandt and Paul Slaby.

I think in systems because of Mr. Glenn.

I travel the world because of M<sup>me</sup> Wieten and Frau Barner.

I am still in STEM because of Mrs. Deyo and Mr. Domanski.

I am a researcher because of Dr. Manish Karir.

I am a professor because of Professors Mark Brehob and Peter Chen.

I am an electrical engineer because of Dr. David Blaauw.

I am an ethical hacker because of Dr. J. Alex Halderman.

I am a Dr. because of Dr. Prabal Dutta.

I am immensely grateful to everyone who has a been a part of shaping my life. I can only hope to pay forward what I have learned from each and every person, and in so doing further amplify the impact of your wisdom and kindness.

To my Committee, Kris Pister, David Culler, Khalid Mosalam, and Prabal Dutta: I find somehow that even when I do not intend to, I end up on the path less traveled in life. Thank you for being exactly the mentors and guides that I needed, exactly when and how I needed them. You have set the shape of my career, and I hope to live up to the models you exemplify.

To my Advisor, Prabal Dutta: What a wild thing, to take a chance on the kid who was falling asleep in your class. To this day, I wonder what you saw, and when the opportunity presents itself, I hope that I will see it in someone too. Thank you for teaching me how to think. Thank you for trusting me with an interesting problem—a dissertation-worthy task!—from day one, and for giving me the freedom and flexibility to explore so many other things along the way. Thank you for backing me, visibly and invisibly, all the times that it really mattered. My time in graduate school has been an absolute joy, thank you for making that possible.

This work was supported in part by the TerraSwarm Research Center, one of six centers supported by the STARnet phase of the Focus Center Research Program (FCRP), a Semiconductor Research Corporation program sponsored by MARCO and DARPA. This work was supported in part by the CONIX Research Center, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA. This research was conducted with Government support under and awarded by DoD, Air Force Office of Scientific Research, National Defense Science and Engineering Graduate (NDSEG) Fellowship, 32 CFR 168a. This material is based upon work partially supported by the National Science Foundation under grants CNS-0964120, CNS-1111541, and CNS-1350967, and generous gifts from Intel, Qualcomm, and Texas Instruments.

## Chapter 1

## Introduction

This dissertation is about modular design and systems considerations for the constrained computing platforms known as Smart Dust. The distinguishing features of Smart Dust devices are that they are both computationally interesting and physically small. Computationally interesting means a device is in some way intelligent: it senses data about its ambient environment; it supports arbitrary computation; it offers communication capability. Physically small for the purposes of this dissertation means a device with a principle node dimension on the order of a millimeter. Conceived of in the 1990s [1], it took until 2011 to realize the first fully self-contained device in the cubic millimeter envelope [2]. Today, the question is no longer how to build any one cubic millimeter computer but rather how to build ten million of them and how to make them useful. Hence this discussion of modular design. This dissertation itself is one piece of a much larger whole. The scope of the Michigan Micro Mote project encompasses several theses [3–7] and dozens of papers and talks [2, 8–17]. These concepts are the product of an enormous effort by a diverse and talented team.

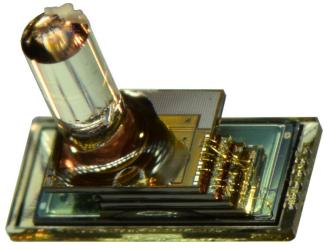

The core contribution of this dissertation is the systems reasoning for an extensible, modular design and the corollary architectural insights that enable modular Smart Dust chips to be deployed ad-hoc. The Smart Dust in Figure 1.1 is set apart by being the first such devices made entirely of modular, reusable components. Roughly half of the individual chips are shared across all three designs.

Figure 1.1: Examples of Smart Dust systems. Three millimeter-scale sensing systems composed using the modularity and system design principles outlined in this dissertation.

Figure 1.2: Bell's Law for the birth and death of computer classes. This figure is a reproduction of the trends identified by Gordon Bell [18, 19]. Summarized, Bell observes that steady year-over-year technological advancements allow for (1) improved performance at fixed cost, (2) lower cost for fixed performance, or (3) greater overall capability. Roughly every decade, however, an amalgamation of advancements come together to allow for (4) a greater-than-iterative change that result in the creation of a new "class" of computing.

## 1.1 Classes of Computing

The emergence of Smart Dust is not the first time that a new and different-looking type of computer has come into the world. In 1975, Ken Olsen and Gordon and Gwen Bell founded The Computer Museum, a precursor to today's Computer History Museum [20]. As part of this process, Gordon Bell began to use the look back as a way to look forward and coined Bell's Law for Birth and Death of Computer Classes [18, 19]. Bell's law, reproduced in Figure 1.2, groups computational systems into classes based on macroeconomic trends:

A computer class is a set of computers in a particular price range with unique or similar programming environments ([...]) that support a variety of applications that communicate with people and/or other systems. (Gordon Bell [18, p. 86])

This grouping into classes shows how progress in underlying technologies manifests in computing devices. In the normal steady-state, extant classes improve iteratively over time. Approximately every decade, however, the collection of many advancements that allow systems to 'do more using less' allow for the imagining of a new "minimal" class, computing systems that are an order of magnitude less expensive but are also as or more capable than their equivalent from the decade before.

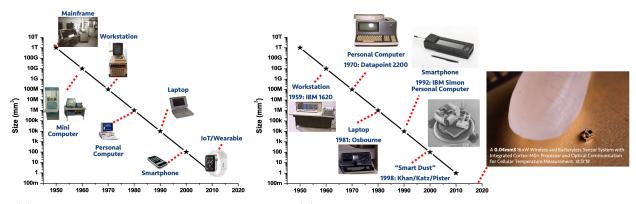

This decennial trend is not restricted to economics, however. Figure 1.3 presents a new corollary to Bell's law based on physical size. At approximately the same cost, every decade one can buy a general purpose computing device that is an order of magnitude smaller. Looking further, while Figure 1.3a looks at the widespread availability of each physical computing class, Figure 1.3b tries to find the first instances of devices in each class. In each case, a new widespread physical class is preceded by a first instance in that class around ten

years earlier. This suggests that there are perhaps two watersheds required to promulgate a new physical class of computing: the first is the collection of advancements that enable the first instance of a class, the 'proof-it-is-possible'; the second is the collection of advancements required for the new class to be reliable, usable, and economically viable. Today, the Smart Dust class lies between these two milestones.

- (a) Volumetric evolution of classes.

- (b) Approximate first instances of each class.

Figure 1.3: Corollary to Bell's Law: Roughly every decade, general-purpose computing grows an order of magnitude smaller. In each case, the new class of computing is foretold by one or a few instances made a decade earlier, which proves such machines are possible. This dissertation looks at what is needed to move the millimeter-scale computer class from possible to prevalent, with an eye towards the even smaller systems to come.

## 1.2 Smart Dust & COTS Motes

The first major push to develop Smart Dust ran roughly for a decade around the turn of the century [1]. That project resulted in the miniaturization of many key elements of future Dust systems including sensor components, micro-actuators, communication frontends, and microprocessors [21–25]. In parallel to the millimeter-scale push ran a side project looking into the development of so-called Macro Motes<sup>1</sup> [26]. While not the primary focus of the original Smart Dust project, these motes had perhaps the more significant immediate impact.

Macro motes laid out the basic components of a useful sensing system. Paraphrasing and slightly updating the original definition: a system must have enough **energy** to do something useful for a reasonable amount of time, must have **sensors** to bridge the digital and physical world, must have **computation** capacity to operate intelligently (or at all), and must have **communication** faculties able to share its results. By showing that such systems could be realized at the centimeter-scale, out of readily accessible commercial-off-the-shelf (COTS) components, the mote computing class was born.

<sup>&</sup>lt;sup>1</sup> "Macro" Motes were likely still some of the smallest complete computational sensing systems, but given the aspirations of the Dust team, all things are relative. Today, we generally call such systems simply "motes."

With the realization of proto-Dust and the first instances of mote-class computing came the same fundamental call to arms that echoes through this document. Kahn, Katz, and Pister asked, now that we are capable of building the proof-of-possible for this emergent mote class of computing, what will be required to go from one to many and to make these many new mote-computers useful [27, 28]? Hollar coined the term "COTS dust" to describe his centimeter-scale Macro Motes [26]. Embedded in this name is the revelation that modularity would not be a challenge for this computing class—it was defined as systems that had all of the desired functionality of the imagined millimeter-scale systems, but could be realized immediately via the composition of available compute, sensing, communication, and power modules. Instead, the need was to "[get] more systems-level researchers interested in this critical area."

Today, systems-level research in mote-class computing, i.e. wireless sensor networking research, is flourishing. As of this writing, the top two subject areas in ACM SIGMOBILE are "Wireless access networks" and "Mobile networks," both of which look to solve the communication, access, and control challenges for portable computational systems. The *International Conference on Information Processing in Sensor Networks (IPSN)* will celebrate its twentieth anniversary next year, and the *Conference on Embedded Networked Sensor Systems (SenSys)* will celebrate its nineteenth year. Key challenges spanning time-synchronization [29], medium access control [30], low-power design [31], networking [32], and much more have been addressed and continue be refined. Yet, if we were to try to make millimeter-scale motes today, we still face the same limitation as the original effort—there is no library of millimeter-scale modules from which to compose such systems.

## 1.3 The Case for Modularity

The spectacular success and diversity of today's centimeter-scale motes, and let us include much of the "Internet of Things" in this measure, are the evidence of the power of enabling modular design. On the one hand, there is proof in various successes at the manufacture of monolithic systems over the years that modular design blocks are not necessary for the creation of a millimeter-scale system [33]. On the other hand, that fact that such designs talk in the number of years to make one system rather than the number of unique systems they can make per year (or month or even day) is the essence of the scale that is missing. Today, a casual hobbyist can visit a local makerspace and in one afternoon devise, design, synthesize, test, and deploy a new centimeter-scale device.

This capacity for system-design-time synthesis of complex motes is enabled by the modular part ecosystem. Consider a radio IC, which encapsulates complex modulation and demodulation operations, precise timing requirements, and sensitive high frequency and analog design blocks into a stable, re-usable package with a lightweight, high-level interface. A system integrator can fuse this radio with a microcontroller, camera, and battery on one device and a microcontroller, screen, and battery on another device to build something new and quite complex like a virtual window, without requiring rich understanding of the internal

workings of any of the constituent pieces. Modular design "increases the range of 'manageable' complexity" and "accommodates uncertainty" [34]. Systems do not need to be built from the ground up every time, and the exact function and operation of a system can be deferred until system-design-time.

### Interconnects and Their Role in Modular Design

Once a system is broken into modular pieces, there must also be something that connects modules back together into a system. In many cases, this interconnect can come to define a class of systems. Indeed, the "PC revolution" and the emergence of the PC class at scale is often defined by the emergence of a wide array of *IBM PC compatible* clones. To quickly and economically bring a new machine to market (the IBM PC and later the IBM XT and IBM PC/AT), IBM designed machines that pieced together generally commercially available modules. To build a clone then, manufacturers simply had to replicate the interconnect used to compose commodity hardware pieces.<sup>2</sup> The AT interconnect would eventually evolve by fiat from a pseudo-standard to the sanctioned Industry Standard Architecture (ISA) Bus, which defined the composition of computers for decades.

### Modularity in the System on Chip Era

Despite the success of ISA and its descendants in the design of innumerable computing systems, today we are seemingly seeing a push back towards integration with the rise of the System on Chip (SoC) architecture. The integration of multiple modules onto a single die for fabrication does not, however, mean that the system which happens to be manufactured into a single physical chip is not modular. SoC designs usually include some form of internal interconnect network or bus (i.e. ARM's AMBA) which integrate modular hardware blocks through a narrow memory bus interface. This memory bus is usually strictly internal to the SoC, though various peripherals with external I/O capability may hang off this bus. This design provides encapsulation and strong isolation of the internal modules, but it does so at the cost of flexibility and composability; it closes off this bus to expansion and integration beyond the originally envisioned SoC. In Chapter 4, this dissertation will show how we can extend the system bus metaphor to become a hierarchy of interconnected system buses between higher-level modules. This allows the preservation of both composability between fabricated modules and the performance advantage of tight, on-die integration.

<sup>&</sup>lt;sup>2</sup>At the time, the real challenge in creating a clone was replicating the Basic Input/Output System (BIOS) firmware. The original intent for BIOS was to act as a runtime hardware abstraction layer, which meant that clones had to provide this same interface in order for existing software to run. Accessing hardware through BIOS proved slow and inefficient compared to directly accessing hardware, however. Through a combination of performance and compatibility concerns (what is the abstraction layer that sits above the differing BIOS abstraction layers...), this hardware abstraction moved up into operating systems and their drivers, relegating BIOS to just the earliest part of the boot process in more modern machines.

Figure derived from phone [36] and watch [37] images from iFixit. Figure licensed CC BY-NC-SA. Source available at patpannuto.com/dissertation.

Figure 1.4: Looking inside modern computing devices. Energy storage technologies are not shrinking at the same rate as computing. As a result, as computing devices get smaller, a larger proportion of their volume is dedicated to energy storage.

## 1.4 Energy Constrained Computing

In the halcyon days of early computing systems, the primary focus of system design was building bigger and better computers that could do more. With the emergence of portable computers (the suitcase-like precursors to laptops), computing 'cut the cord.' Suddenly, it became possible and reasonable for a computer to no longer be tethered to a wall, and equally suddenly it became important for these machines to be able to do more with less. The power draw of a system now determined the lifetime of a system (at this point in history, power dissipation and resulting thermal management concerns were also on the radar, but not yet a primary limiting factor for most semiconductor system performance [35]).

Again, there is a corollary available to Bell's Law. Instead of considering a constant price in dollars and cents, one can hold constant the energy reserves of a portable machine, and find that time and its technological improvements allow for more capable machines (i.e. the steadily improving laptop class). Similarly, one can lower energy rather than lowering price, and find devices slowly shrinking for about the same capability and the possibility of sub-class formation (i.e. thinner, lighter laptops and lately the blurry line between these and tablet computers). Finally, one can lower energy dramatically, and find a new class of device, with comparatively less compute capability, but new levels of portability and utility (i.e. the emergence of the smartphone class).

Interestingly, this trend is driven both by the reduction in energy demand of newer compute technologies as well as the increase in capability of energy storage technologies. Indeed, battery technology has been improving for centuries, since Alessandro Volta's first voltaic pile in 1799. One consequence of this long history, however, is that today the rate of improvement for energy storage technology is considerably slower than that of computing [38]. As a result of the miniaturization of computing outpacing the miniaturization of energy storage, it is increasingly becoming the case that the principle dimension of a computing system is dictated by the energy required to power it, as seen in Figure 1.4.

### Techniques to Reduce Energy

Smart Dust pushes the limits of today's capabilities to miniaturize computing. As a result, these systems no longer adhere to the volume proportionality of current portable computing systems. The systems in Figure 1.1 are more computer than battery. To operate then, these systems must use proportionally less energy as well. That is, Smart Dust systems must develop new energy reduction techniques beyond those used in portable computing today.

#### Voltage and Frequency Scaling

When a system is active, its power use is dominated by switching power losses. Switching power draw is proportional to the square of the system voltage and to the system frequency (i.e.  $P = C \times V^2 \times f$ ). This relationship drove significant effort into reducing system operating voltage to, and later below, the threshold voltage of standard CMOS [39]. There is a bound to the performance gains of voltage scaling, however. As voltage decreases, leakage current grows, and eventually the gains in switching performance are overcome by this increased leakage [40]. The chips used to compose the Smart Dust systems, as described in this work, reach a core voltage of 0.6 V, which is near the limit of today's practical fabrication technologies. While there is still some headroom, particularly with the advent of lower-threshold low-leakage transistor technologies, voltage scaling alone is insufficient to reach energy targets.

Somewhat counter-intuitively, low-power systems often aim to increase their operational frequency (within reason). While increasing frequency increases the instantaneous power draw of the system, it also allows the system to complete its operation in a shorter window of time. Ultimately, the goal is to reduce the total energy use—which is the integral of power over time. The insight here is that in a vacuum, because power is linearly related to frequency, changing the frequency up or down would have no net change in consumed energy. However, in real systems there are additional, constant, static overheads. This is the principle that underlies computational sprinting [41]. Of course, generating very fast clocks is also energy intensive, which caps the practical benefits of increasing frequency as well. The takeaway now is that while voltage and frequency scaling both can help, they alone are insufficient to realize Smart Dust energy budgets.

#### From Dark Silicon to Pitch Black Silicon

What happens when a system finishes its computational sprint? Systems will shut down components that are not in active use to save energy. In performance-oriented designs, this phenomenon where more and more die area is shut down is commonly referred to as "Dark Silicon" [42]. For these systems, shutting down generally means cutting the clock that feeds various subsystems or asking components to enter a sleep state to eliminate idle switching losses. However, these 'shut down' component still preserve state and can exhibit static leakage that proves non-trivial for the energy budget of Smart Dust systems. This is where the extremely resource constrained Smart Dust class exhibits a new operational paradigm, which I call **pitch black silicon**.

When subsystems are not in use, Smart Dust systems power them off completely. Without a new support mechanism, this aggressive energy management strategy can sit at odds with modularity. Components and subsystems must now be freestanding and can no longer rely on the presence of an always-on, central power management block. For the circuit designer, this means each module must provide its own custom timing and control signals to manage cold boot; it also means a new, potentially unique-per-chip, interface to report and control its power state—how, when, and why does something power on? For the systems designer, this turns power state into a distributed systems problem—how is one module to know whether it can safely communicate with another or if it must first power on its target? For the platform integrator, a series of ad-hoc answers to these questions limits the flexibility and reusability of components—routing custom power control between modules is no longer modular design—and impedes abstract, platform-level functionality—how does something like a brown-out detector quickly reduce system load? Modular design with pitch black silicon requires that energy and power are managed by the interface that defines module boundaries.

#### 1.5 Thesis Statement

With the introduction of a clockless, "shoot-through" ring topology, it is possible to design an interconnect that both encompasses the modular design principles that enable system-design-time composition and respects the resource constraints of millimeter-scale "Smart Dust" systems; the creation of such an interconnect will accelerate the development of a diversity of Smart Dust systems and accelerate the actualization of the millimeter-scale computing class.

## 1.6 Contributions of this Dissertation

This dissertation presents modular design principles, and the development of a new interconnect to support them, for the Smart Dust computing class.

The foundation of this dissertation is MBus. MBus is part of the larger Michigan Micro Mote (M3) initiative, which aims to build an array of novel micro-scale motes—Smart Dust—and works to develop all of the constituent technologies required to realize these devices. Within this larger whole, the development of MBus was a collaboration with Yoonmyung Lee, Ye-Sheng Kuo, ZhiYoong Foo, Benjamin Kempke, Ronald Dreslinski, David Blaauw, and Prabal Dutta. Various pieces of MBus described in this document have been published at CICC'14 [43], ISCA'15 [44], and Micro Top Picks '16 [45]. In addition, some of the initial exploration that drove the need for MBus was published as a demo at IPSN'12 [50]. Ideas and results from these publications are woven through the entirety of this document, primarily Chapter 2, Chapter 3, and Chapter 5 and to a lesser extent Chapter 4. In contrast to the prior refereed proceedings, this dissertation is able to take a holistic view of the entire design.

<sup>&</sup>lt;sup>3</sup>There are several additional publications related to MBus, and moreso the systems built on top of it, whose content are not included in this dissertation (non-exhaustively [46–49]).

Chapter 2 lays out the case for a new bus. It looks at an expanded history and comparison of embedded interconnects, including the addition of newer designs such as I3C (MIPI), to understand the root causes of overheads and incompatibilities for Smart Dust. It then synthesizes the needs from circuits to systems to lay out the set of criteria for an interconnect for resource constrained systems. These criteria then serve as the foundation for the rest of the design and evaluation.

Chapter 3 describes the design of MBus. The design is broken into three major elements. The first design point is the physical interconnect, in which a new "shoot-through" ring topology is presented as the best balance of I/O overhead, system active power, and scalability. The second design point is the logical operation of the interconnect, which looks at how to safely and efficiently share the physical wires and also introduces a new, low-overhead interjection technique to handle message framing, acknowledgment, and bus errors robustly and with very low overhead. The final design point is new to interconnects and a unique requirement of Smart Dust systems. Here, MBus adds faculties for transparent, complete system power management. The interconnect is able to provide the illusion of always-on components, while eliminating nearly all dynamic and static leakage power losses by completing powering off unused components and managing their cold-boot in parallel to message arrival.

Chapter 4 describes the design of MPQ, the protocol that runs atop MBus and defines the interface between modules. Before laying out the protocol design, this chapter looks at the tradeoffs between standardization and capability afforded from interconnects across a broader landscape of computing than previously discussed. With this background, it makes the case for a standardized model of memory and registers across all connected devices, and further a standard means of controlling data transfers. The result is a novel and powerful namespaced MMIO abstraction. This interaction model will ultimately serve as the foundation for the federated operation highlighted in Chapter 5 as well as the system-level programming and debugging techniques laid out in Chapter 6.

Chapter 5 makes it all work on real hardware. It begins by mapping the concepts from Chapter 3 and Chapter 4 onto concrete hardware designs. This section covers some of the key subtleties and implementation details. Then it evaluates the performance of the interconnect, both in principle and in practice. This includes theoretical analysis of the performance of the protocol and measured performance on two real-world Smart Dust systems: a temperature sensor and an imager.

Finally, Chapter 6 zooms out from individual devices and looks at the Smart Dust ecosystem as a whole. It describes the design of M-ulator, a new hybrid simulation and in-circuit emulation tool designed to aid the initial bringup and debugging of Smart Dust systems. It also looks at questions of programming and debugging Smart Dust once physical access is no longer an option. Here, the platform design from Chapter 4 shines, as a minimalist injection frontend is able to support rich, complex operations such as *in situ* programming and restricted debugging.

## Chapter 2

## The Case for a New Bus

This chapter begins with an in-depth look at existing interconnects. The goal is to understand common design points and what aspects do and do not work well for the Smart Dust computing class. Ultimately, this survey concludes that no existing design can meet all of the needs of Smart Dust. This summary is then combined with experience from building a number of pre-modular Smart Dust systems to draft a list of requirements for the interconnect for this emerging computing class. This chapter makes no design decisions, rather it seeks to lay out the constraint space that will inform the architecture of modular, millimeter-scale computing.

## 2.1 Related Work

Before building a new bus, it is important to first show why existing, widely adopted bus protocols like I<sup>2</sup>C, CAN, SPI, and I<sup>2</sup>S are not viable system interconnects for modular, resource-constrained systems. The problems stem from their energy use, protocol overhead, pin count, and system design requirements.

## I<sup>2</sup>C, 1-Wire, CAN, and Other Open-Collector Buses

Many interconnects use an open-collector or open-drain design (e.g. I<sup>2</sup>C [51], SMBUS [52], and CAN [53]). This circuit construct turns each bus line into a wired-AND; one or many devices can drive a 0 on the bus, but if nothing actively drives low, then pull-up resistors pull each line high. The advantages of this approach are decentralized arbitration and multi-tiered priority. The pull-up resistors, however, are not energy efficient and result in designs that have up to three orders of magnitude worse energy per bit than MBus.

To illustrate, consider an idealized  $I^2C$  configuration running at 1.2 V (a typical I/O voltage for Smart Dust) that tries to optimize for energy consumption.  $I^2C$  typically requires the pull-up resistor be sized to accommodate 400 pF of total bus capacitance, but that can be relaxed to, say, 50 pF for micro-scale systems; fast mode  $I^2C$  has a 400 kHz clock and must reach 80%  $V_{DD}$  in 300 ns, but again relax that (eliminate setup and hold time) to the full

Figure 2.1: Waveforms of  $I^2C$  and variants. A comparison of traditional  $I^2C$  and some of the proposed variations. Shaded areas are power-expensive protocol elements.

half-cycle (1.25 µs). This relaxed  $I^2C$  bus requires a pull-up resistor no greater than  $15.5 \,\mathrm{k}\Omega$ . To generate the bus clock, this resistor is shorted to ground for a half period, dumping the charge in the bus wires, pads, and FET gates (23 pJ) and dissipating power in the resistor (116 pJ). The clock line then floats for a half cycle and the resistor pulls it high (35 pJ). Thus, generating the clock alone draws  $69.6 \,\mu\mathrm{W}$ . Eliminating the switching power—the  $23 \,\mathrm{pJ/bit}$  charging and discharging of the wire, pad, and gate capacitance—requires complex adiabatic clocks, outside the scope of many practical designs [54, 55]. MBus finds its energy gains by eliminating the  $151 \,\mathrm{pJ/bit}$  lost to the pull-up resistor.

### I<sup>2</sup>C Variations

One conceivable idea for reducing the impact of the pull-up might be to "unbalance" the clock as shown in Figure 2.1. This would allow the designer to nearly double the size of the pull-up resistor (halving the power draw) while maintaining the same bus clock period and minimizing the impact of the SCL line on energy usage. Unfortunately, this concept does not reduce the energy consumed by the pull-up while pulling up, nor does it reduce the energy consumed by the data line when transmitting 0's. Unbalanced clocks would also require local timing modifications, costly in energy and complexity, ruling out this possibility.

Lee et al. reduce I<sup>2</sup>C power draw by designing an "I<sup>2</sup>C-like" bus that replaces the pull-up resistor with logic that actively pulls the bus high and a low-energy "bus keeper" circuit that preserves the last value [17] (similar to I<sup>2</sup>C Ultra Fast-mode [51]). While this eliminates the pull-up, it does so at the cost of requiring a local clock running 5× faster than the bus clock, the energy inefficiency seen in Figure 2.1. There is not a clear path to designing an I<sup>2</sup>C or I<sup>2</sup>C-like bus without either a pull-up or a fast-running internal clock. While the internal clock is not as energy-intensive—Lee's system is able to reduce bus energy to 88 pJ/bit (4 times that of MBus)—, Lee's design also requires hand-tuned, process-specific ratioed logic; this requires manual tuning of every chip and runs counter to the goals of a general-purpose bus.

Furthermore, while Lee's I<sup>2</sup>C variant is designed with commercial interoperability in mind, in practice actual interoperation requires an FPGA to translate between I<sup>2</sup>C and the "I<sup>2</sup>C-like" bus [50]. MBus eschews the "partial compatibility" that I<sup>2</sup>C-like buses provide and uses the clean break to reconsider the primitives provided by the system interface, allowing the addition of features such as power oblivious communication, broadcast messages, and efficient transaction-level acknowledgments.

## SPI, I<sup>2</sup>S, Microwire, and Other Single-Ended Buses

As single-ended buses, SPI and its derivatives do not suffer from the power challenges faced by open-collectors and have little to no protocol overhead. SPI, however, requires a unique chip-select line for every slave device. In a modular system with a variable (and unknown until system design time) number of components, it is difficult to choose the "right" number of chip select lines a priori—too few impede modularity and too many violate the area constraints of Smart Dust systems. Additionally, SPI requires a single master that coordinates and controls access to all slave devices, and it requires all communication between slave devices to go through the master node. This more than doubles the communication cost for slave-to-slave transmissions: every message is sent twice plus the energy of running the central controller. A further subtle, yet critical, implication of a single-master design is that all communication is master-initiated. For a sensor to signal a microcontroller (i.e. an interrupt), it requires an additional I/O line, a resource that is unavailable to Smart Dust systems.

Alternative configurations such as daisy-chained SPI can eliminate the chip-select overhead but do not solve the multi-master/interrupt issue and require the addition of a protocol layer to establish message validity. As a system-wide shift register, a daisy-chain configuration adds overhead proportional to both the number of devices and the size of the buffer in each device. SPI and its derivatives are fundamentally incompatible with size-constrained microsystems.

## The Improved Inter Integrated Circuit (I3C)

Some of the limitations of I<sup>2</sup>C and SPI are also affecting the emerging mobile (smartphone) and wearable computing classes. The MIPI Alliance is a trade association that aims "to design and promote hardware and software interfaces that simplify the integration of components built into a device [56]." In 2014, recognizing the limitations of I<sup>2</sup>C and SPI, MIPI formed a working group to develop a new interconnect technology. In 2018, the result was the Improved Inter Integrated Circuit (I3C) [57].

The I3C design has many similarities to Lee I<sup>2</sup>C. In particular, it also introduces the idea of both a bus keeper and explicit push-pull logic. However, I3C includes extra provisions that attempt to better ensure backwards compatibility with I<sup>2</sup>C. The I3C insight is to assign a fairly capable "Main Master" device that has full knowledge of all attached devices as well as the ability to dynamically detach the pull-ups. At idle and in early arbitration, the bus always uses the pull-up resistors in the traditional I<sup>2</sup>C manner. However, during addressing if the Main Master establishes that no legacy I<sup>2</sup>C devices are involved, it can detach the

pull-ups and switch to active drivers. While this (and some additional details in the I3C specification) does resolve the interoperability challenges, it still requires I3C member devices to include local high-speed clocks, just like Lee I $^2$ C. Indeed, the I3C specification suggests that it achieves an approximately  $10\times$  reduction in energy per bit over traditional I $^2$ C, with a best case around  $100\,\mathrm{pJ/bit}$ , which is very similar to Lee I $^2$ C's  $88\,\mathrm{pJ/bit}$ . If, however, a bus were to eliminate the need for local oscillators on each node, the active power can be reduced another full order of magnitude, a necessary energy savings for Smart Dust class devices.

Another interesting aspect of I3C is the partial support for power-conscious nodes and systems. The specification includes some considerations for behavior when system or node power states change, however "system power management" is explicitly listed as not in scope for I3C. Instead, the bus adds support for "Hot-Join", where nodes may dynamically leave or join the bus (including the master, which must delegate another master before powering off or possibly leave the bus inoperable until it powers back on). While this design allows nodes to power themselves off and on, it does not provide any in-band mechanism to remotely power on another node, which means that systems must provide additional I/O signaling if it is expected that one node be able to request that another node power on. In the extreme, full any-to-any power requests would require a complete parallel interconnect network solely for system power management. To support full flexibility in power management policies, it is necessary for system power management to be supported in something that connects all nodes, which means either that the system interconnect must support power management or its connectivity must be duplicated.

The other major change from I<sup>2</sup>C is the addition of dynamic addressing. As I3C retains the 7-bit address space from I<sup>2</sup>C, it resolves the potential address conflict problem by requiring that nodes use dynamic address assignment. While this is useful for systems where conflicts occur, the requirement to always use dynamic addressing introduces needless overhead in systems where pre-assigned addresses would not have conflicted. This overhead is particularly troublesome in conjunction with the Hot Join mechanism, as the specification requires that dynamic address assignment occur at every start-up event (and that full reassignment occur whenever the master node starts up).<sup>1</sup> In Smart Dust systems, whole nodes power off and on frequently to realize energy goals, which makes such a re-enumeration requirement poorly suited to these designs.

## Bus Designs from Other Disciplines

The original token ring protocol requires passing empty frames so that nodes can grab the token when they need it. Low-power systems rely on low duty cycles to remain efficient. Using tokens in place of arbitration either requires occasional empty frames to pass the token, with an inherent latency/energy tradeoff, or a sacrifice of in-band multi-master capability.

<sup>&</sup>lt;sup>1</sup>One positive aspect of this design is that it partially ameliorates one system power management challenge. By snooping, other nodes on the bus could know when a powered off node powers on. This is of limited use, however, as other nodes still have no way to request that a node powers on, simply the ability to observe that it has happened.

The Domestic Digital Bus (D2B) [58] is a ring topology, like MBus. D2B links are high-power fiber optics, targeting automobiles. D2B requires a separate electrical network to facilitate wakeup of the optical frontends and uses a centralized master that must know the complete topology in advance [59]. D2B is not easily adaptable to the micro-scale domain.

Some of the new network-on-chip (NoC) protocols that have been developed, such as Nehalem's QuickPath [60], include power-aware features like MBus. These buses seek to move large amounts of data often via wide parallel buses, within a siloed system rather than compose independently designed, modular components.

Recently, work in energy-efficient, short-reach data links has led to energy performance as low as 0.54 pJ/bit [61]. These designs target high-performance computing applications, however, utilizing complex transmit and receive circuitry with high-speed clocks [62] and add requirements such as a common substrate with carefully carved channels [61]. This limitation is not well suited to a platform bus, which aims to support a wider diversity of packages and physical interconnection technologies.

#### Power Savings Create Communication Problems

Smart Dust systems need to aggressively conserve power. Devices that are left on or in standby allow communication to occur on-demand. Ultra-low power systems, however, realize their power goals in part through aggressive duty-cycling. A power-gated node must be awakened before it can communicate, presenting interoperability (how to wake a node) and run-time (when to wake a node) challenges.

Lee et al. identify this wakeup issue and modify their protocol to include a wakeup signal: an I<sup>2</sup>C start bit followed shortly by a stop bit. This requires the sender to know the receiver's power state in advance or to unconditionally send the wakeup sequence before every message. Due to implementation choices, the minimum time between the start and stop bits of the wakeup sequence and the time until the chip is awake after the stop bit is received varies from chip to chip, which requires hand-tuning and conservative estimates. This design also requires each chip to implement a power-on circuit capable of self-starting.

In contrast, MBus takes over the power management of nodes, freeing designers from the burden of building complex self-start circuits. MBus guarantees delivery of messages, independent of the power state when a message is sent, eliminating requirements for distributed power state management.

## The Opportunities of Clean Slate Design

One lesson from the Lee I<sup>2</sup>C and I3C designs is that working from an existing standard can place limitations on design that are not required by the underlying system. For that reason, the next section takes a constructivist approach. It looks from the perspective of both a circuit designer and system designer at what properties an interconnect might provide to support Smart Dust systems. In the end, mapping those requirements back to these buses will find that no current design meets all the needs of Smart Dust.

|                                   | $I^2C$        | SPI            | UART                  | $\mathrm{Lee}\text{-}\mathrm{I}^2\mathrm{C}$ | I3C             | MBus            |

|-----------------------------------|---------------|----------------|-----------------------|----------------------------------------------|-----------------|-----------------|

| Driven by Physical Limits         |               |                |                       |                                              |                 |                 |

| Synthesizable                     | Yes           | Yes            | Yes                   | No                                           | Yes             | Yes             |

| I/O Pads $(n  nodes)$             | $2/4^\dagger$ | 3 + n          | $2 \times n$          | $2/4^{\dagger}$                              | $2/4^{\dagger}$ | <b>4</b>        |

| Global Unique Addresses           | 128           | _              |                       | 128                                          |                 | $2^{24}$        |

| Multi-Master (Interrupt)          | Yes           | No             | No                    | Yes                                          | Yes             | Yes             |

| Standby Power                     | Low           | $\mathbf{Low}$ | $\mathbf{Low}$        | $\mathbf{Low}$                               | $\mathbf{Low}$  | Low             |

| Active Power                      | High          | $\mathbf{Low}$ | Low                   | Moderate                                     | Moderate        | $\mathbf{Low}$  |

| Driven by Protocol                |               |                |                       |                                              |                 |                 |

| Data-Independent                  | Yes           | Yes            | Yes                   | Yes                                          | Yes             | Yes             |

| Robust Bus Reset                  | No            | Yes            | No                    | No                                           | No              | Yes             |

| Dynamic Address Option            | No            | _              |                       | No                                           | Yes             | Yes             |

| Hardware ACKs                     | Yes           | No             | No                    | Yes                                          | Yes             | Yes             |

| Broadcast Messages                | Option        | Option         | No                    | No                                           | Yes             | Yes             |

| Power Aware                       | No            | No             | No                    | No                                           | No              | Yes             |

| Bits Overhead $(n \text{ bytes})$ | 10 + n        | $2^{\ddagger}$ | $(2-3)^{\S} \times n$ | 10 + n                                       | 10 + n          | <b>19</b> , 43* |

<sup>†</sup> When wirebonding, a shared bus requires two pads/chip (or a much larger shared pad)

Table 2.1: **Feature comparison matrix.** Population-independent area, ultra-low power operation, synthesizability, an area-free global namespace, and interrupt support are fundamental requirements for a general purpose Smart Dust interconnect. Standby power is on the order of 100's of pW and active power ranges from 10's of  $\mu$ W to 10's of  $\mu$ W.

## 2.2 Interconnect Criteria

This section summarizes the requirements for the system interconnect of ultra-constrained systems. These requirements and guidelines are the product of several generations of experience in building such devices.<sup>2</sup> The requirements are divided into two major classifications. The first set describe requirements driven from physical-world realities that impose inviolable limits on the design space. The second set describe the needs of systems and inform direction within the allowed physical design space. Table 2.1 summarizes these requirements.

<sup>&</sup>lt;sup>‡</sup> Asserting and de-asserting the chip-select line

<sup>§</sup> Depending on the stop condition; assumes 8-bit frames and no parity

<sup>\*</sup> Depends on whether short (more common) or long addressing is in use

<sup>&</sup>lt;sup>2</sup>I wish to emphasize again here that this is a summation of a collective experience. I am extraordinarily grateful to all members of the Michigan Micro Mote team, especially David Blaauw, Prabal Dutta, ZhiYoong Foo, Benjamin Kempke, Ye-Sheng Kuo, and Yoonmyung Lee whose ideas and insights I sincerely hope to have represented well here. Additional thanks to the members of the Berkeley Wireless Research Center, the TerraSwarm Research Center, and the Stanford Internet of Things Project, who provided critical early and late-stage feedback.

#### Physical Constraints

Smart Dust is largely defined by being physically small. This means that there is limited surface area for the individual modules that make up a system and limited volume for the whole of a system. As a result, systems have limited energy and are restricted in their physical design. This section distills these physical realities into constraints on interconnect design.

#### Low, Fixed Wire Count