### EECS 427 VLSI Design

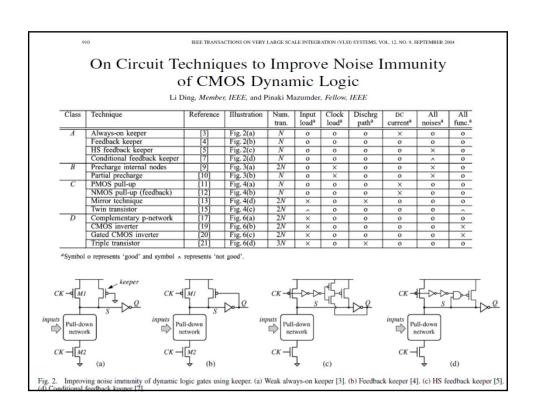

Lecture 11: Dynamic Logic Families

Prof. Pinaki Mazumder

Winter 2013

Adapted from Harris, Rabaey, Blaauw, Zhang, Sylvester, and others

#### Outline

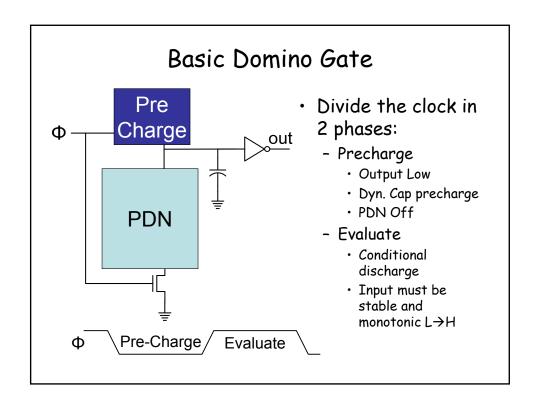

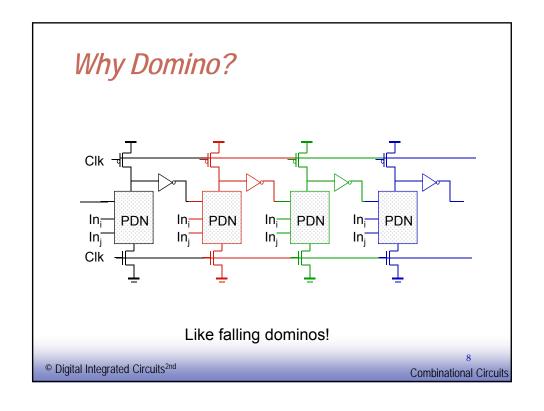

- · Basic domino gate

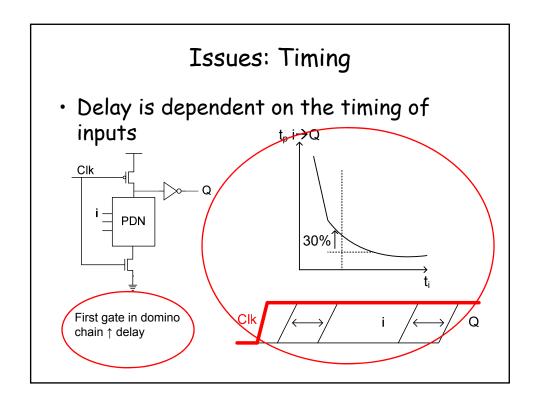

- Issues in dynamic gates

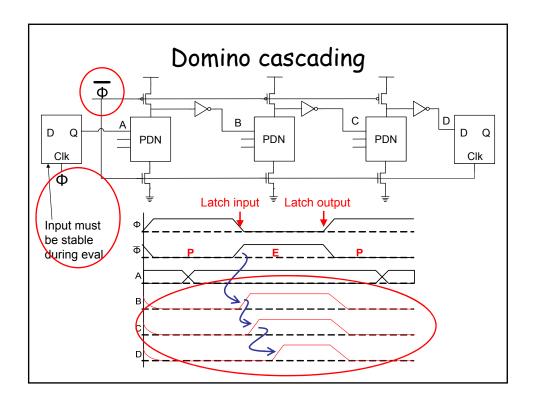

- · Domino cascading

- · Footless domino

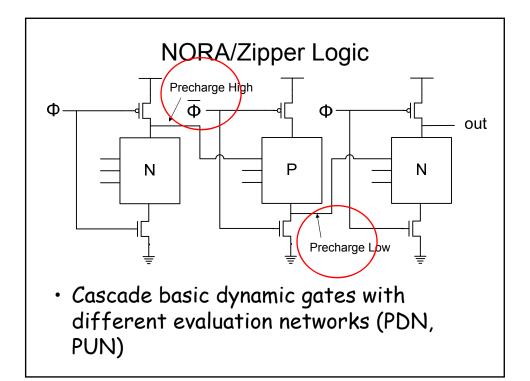

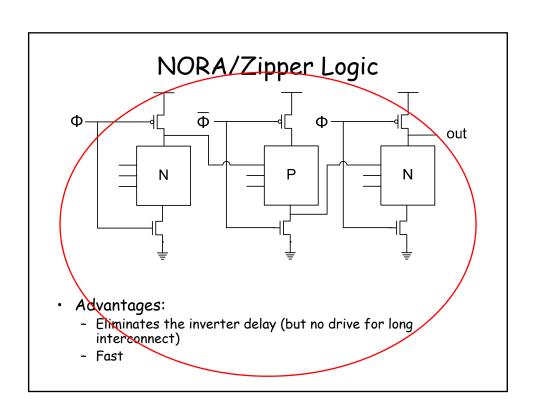

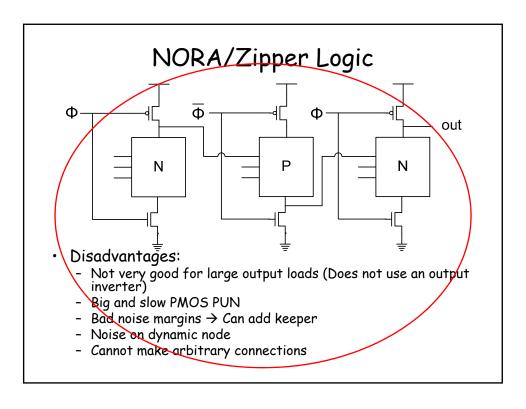

- NORA/Zipper logic

- Multiple-output domino logic

- · Compound domino

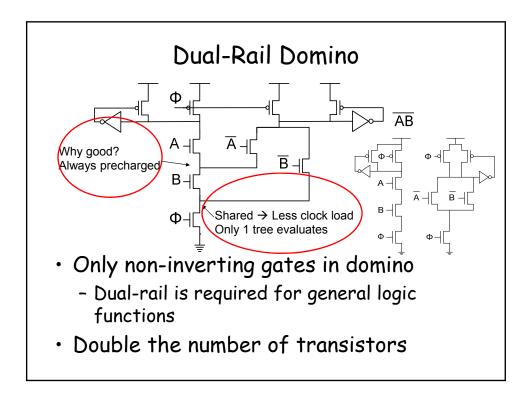

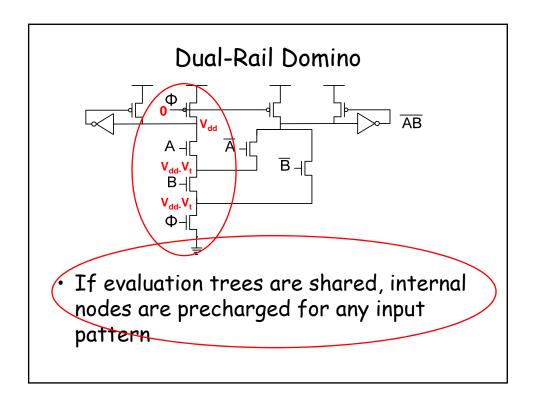

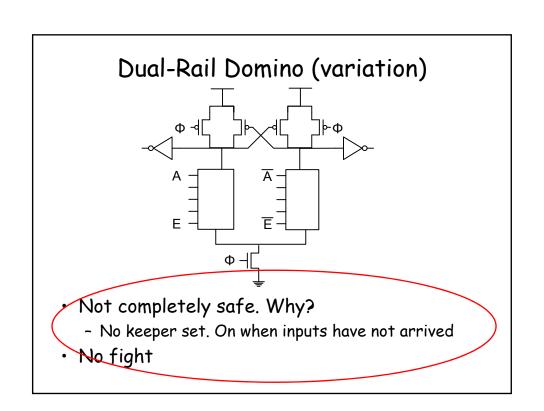

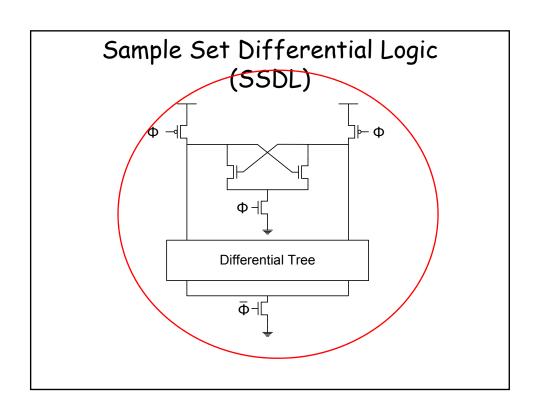

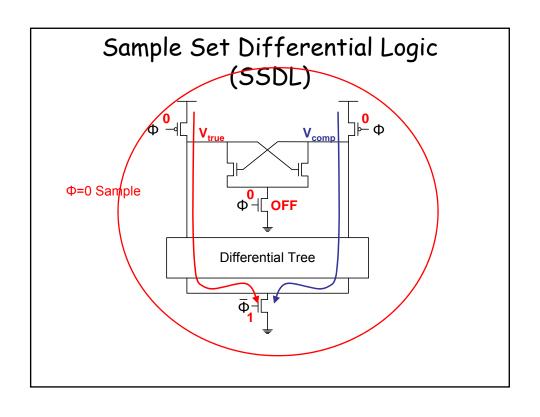

- · Dual-rail domino

- Self-reseting domino

- · Limited Switch dynamic logic

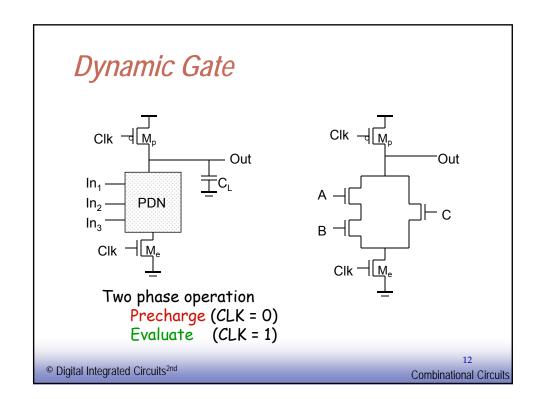

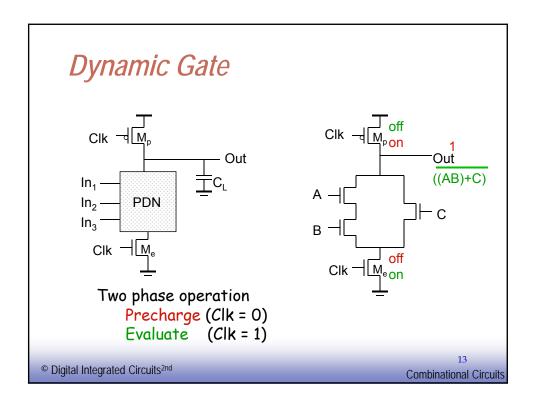

### Dynamic CMOS

- $\Box$  In static circuits at every point in time (except when switching) the output is connected to either GND or  $V_{DD}$  via a low resistance path.

- fan-in of n requires 2n(n N-type + n P-type) devices

- Dynamic circuits rely on the temporary storage of signal values on the capacitance of high impedance nodes.

- requires on n + 2 (n+1 N-type + 1 P-type) transistors

© Digital Integrated Circuits<sup>2nd</sup>

### Conditions on Output

- Once the output of a dynamic gate is discharged, it cannot be charged again until the next precharge operation.

- □ Inputs to the gate can make at most one transition during evaluation.

- $\Box$  Output can be in the high impedance state during and after evaluation (PDN off), state is stored on  $C_1$

© Digital Integrated Circuits<sup>2nd</sup>

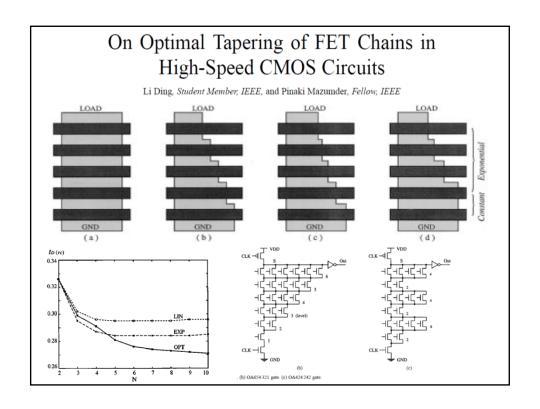

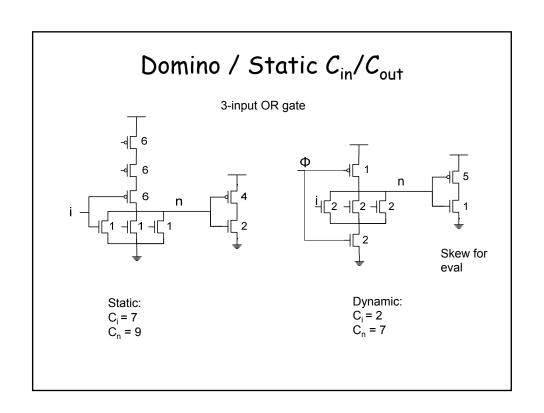

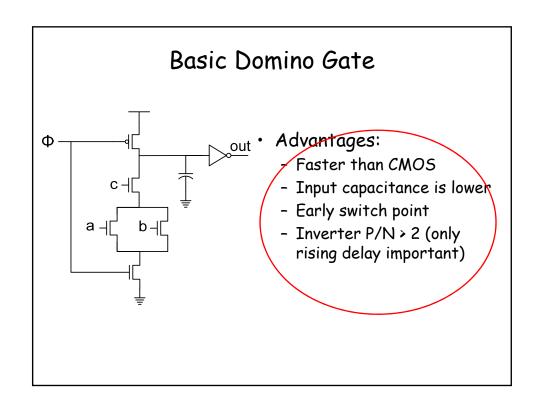

#### Properties of Dynamic Gates

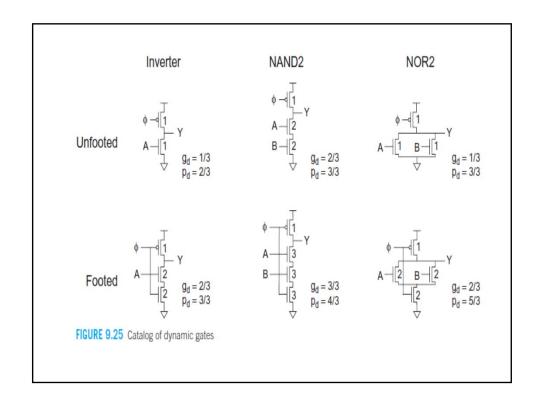

- □ Logic function is implemented by the PDN only

- number of transistors is N + 2 (versus 2N for static complementary CMOS)

- $\Box$  Full swing outputs ( $V_{OI} = GND$  and  $V_{OH} = V_{DD}$ )

- □ Non-ratioed sizing of the devices does not affect the logic levels

- □ Faster switching speeds

- reduced load capacitance due to lower input capacitance (C<sub>in</sub>)

- reduced load capacitance due to smaller output loading (Cout)

- no I<sub>sc</sub>, so all the current provided by PDN goes into discharging

© Digital Integrated Circuits<sup>2nd</sup>

**Combinational Circuits**

## Properties of Dynamic Gates

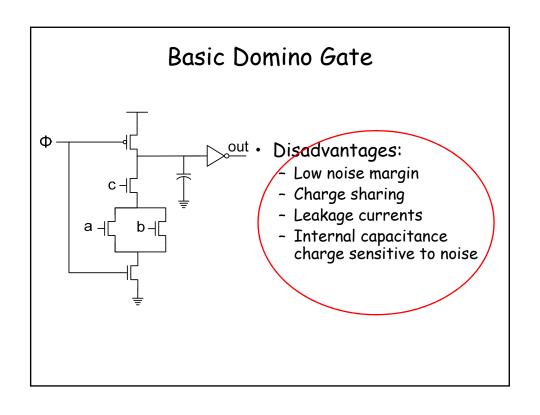

- Overall power dissipation usually higher than static CMOS

- no static current path ever exists between V<sub>DD</sub> and GND (including P<sub>sc</sub>)

- no glitching

- higher transition probabilities

- extra load on Clk

- □ PDN starts to work as soon as the input signals exceed  $V_{Tn}$ , so  $V_M$ ,  $V_{IH}$  and  $V_{IL}$  equal to  $V_{Tn}$

- low noise margin (NM<sub>1</sub>)

- □ Needs a precharge/evaluate clock

© Digital Integrated Circuits<sup>2nd</sup>

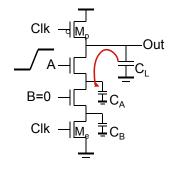

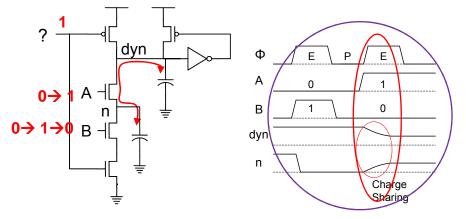

# Issues in Dynamic Design 2: Charge Sharing

Charge stored originally on  $C_L$  is redistributed (shared) over  $C_L$  and  $C_A$  leading to reduced robustness

© Digital Integrated Circuits<sup>2nd</sup>

Combinational Circuits

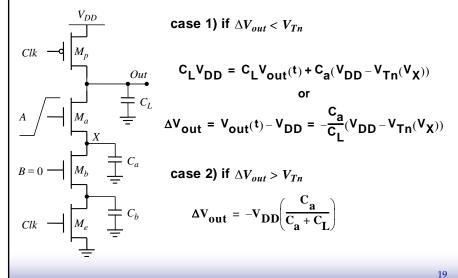

# Charge Sharing Example

© Digital Integrated Circuits<sup>2nd</sup>

© Digital Integrated Circuits<sup>2nd</sup>

Combinational Circuits

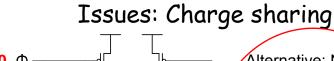

## Solution to Charge Redistribution

Precharge internal nodes using a clock-driven transistor (at the cost of increased area and power)

**Combinational Circuits**

© Digital Integrated Circuits<sup>2nd</sup>

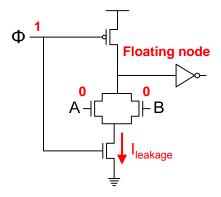

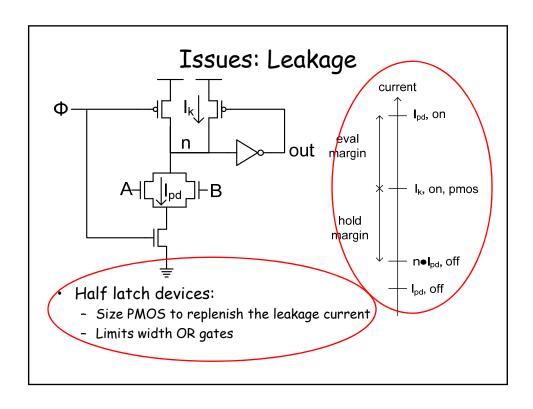

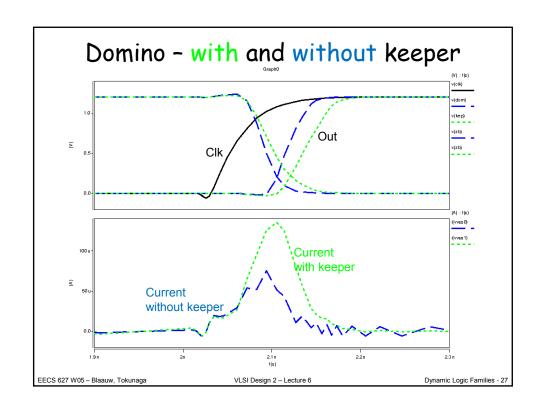

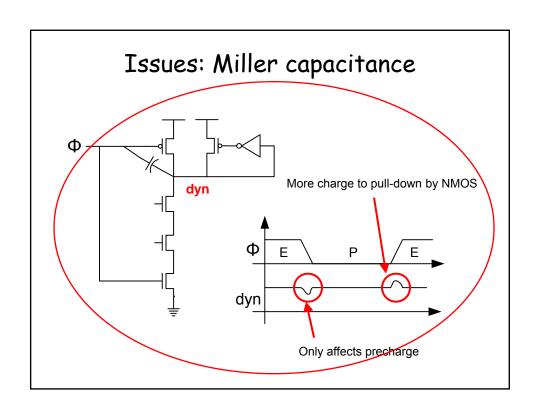

#### Issues: Leakage

- Dynamic node is floating during evaluation

- Leakage current of NMOS can discharge it

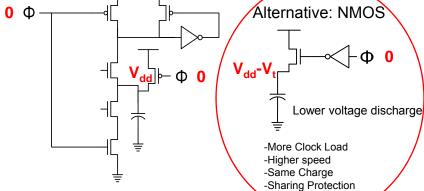

### Issues: Charge sharing

- In evaluate, dynamic node charge is shared with internal node caps

- Node was discharged in previous cycle

- Issues with precharging internal node:

- PDN becomes slower (more internal cap.)

- Higher voltage to discharge

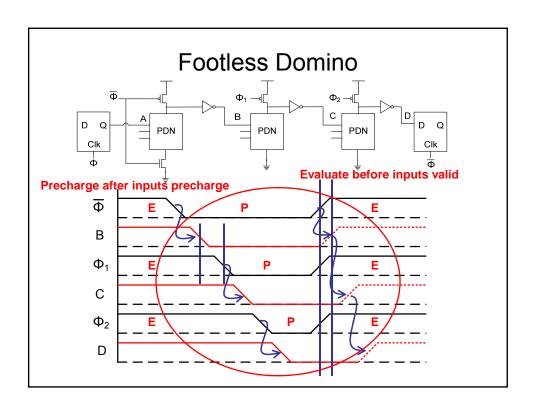

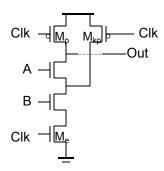

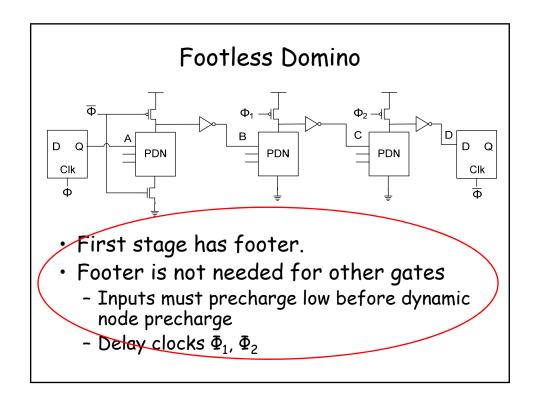

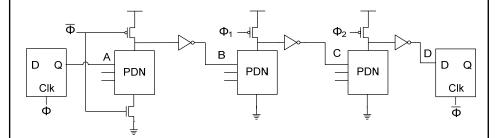

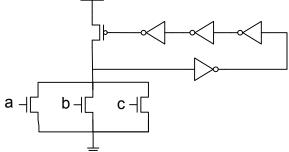

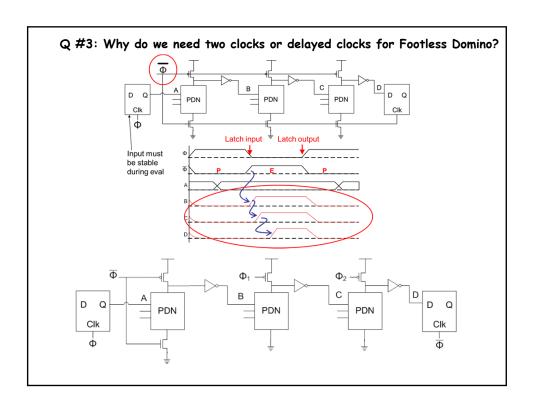

#### Footless Domino

- Advantages:

- Faster than classic domino → one less NMOS

- Why is footer necessary in the first stage?

- · Input not guaranteed during precharge

#### Footless Domino

- Disadvantages:

- Use of different clocks → Can not simply delay the clock (fast inputs during eval)

- Reduced precharge time for later stages

- Tradeoff of sizing up PMOS (increase dynamic cap.) vs 1 less NMOS in PDN (footless)

- But can use a footed stage after a footless stage to recover

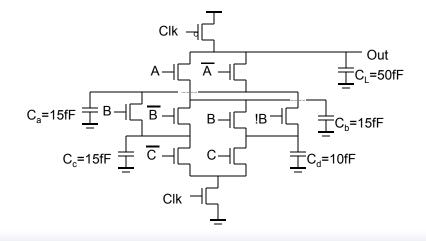

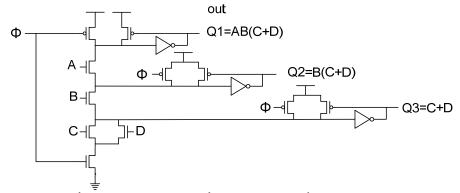

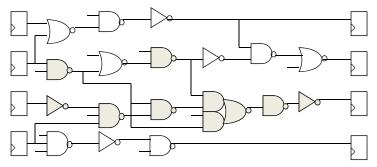

#### Multiple-Output Domino (MODL)

- · Implement more logic per domino stage

- Slowdown top output but more work done

- Very common

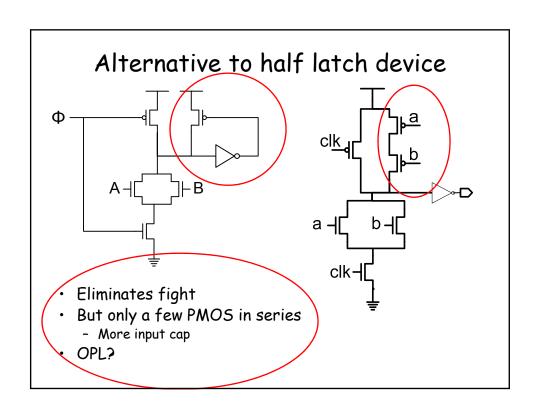

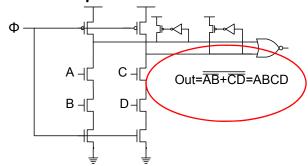

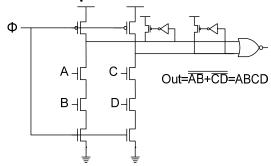

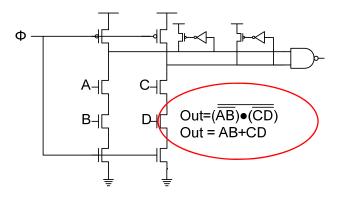

### Compound Domino

- · Add static gates to evaluate logic

- Need to add half latches to every output node

### Compound Domino

- Reduce the number of transistors in a stack (faster)

- Due to V<sub>dd</sub> scaling no more than 4 transistors in a stack (Vdd~4\*V<sub>dsat</sub>)

- But use two PMOS in NOR gate to drive output high

### Compound Domino

· What static gate can you add?

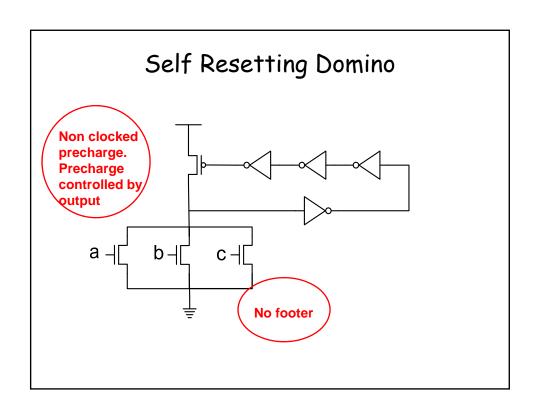

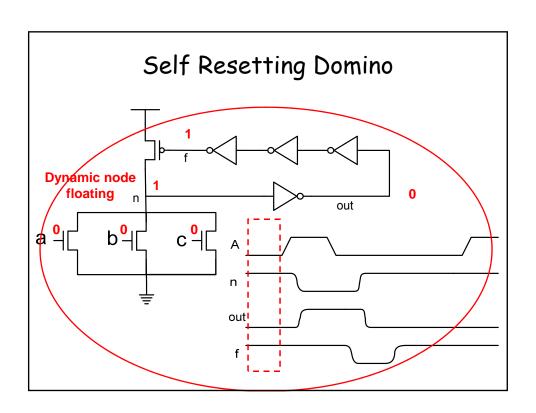

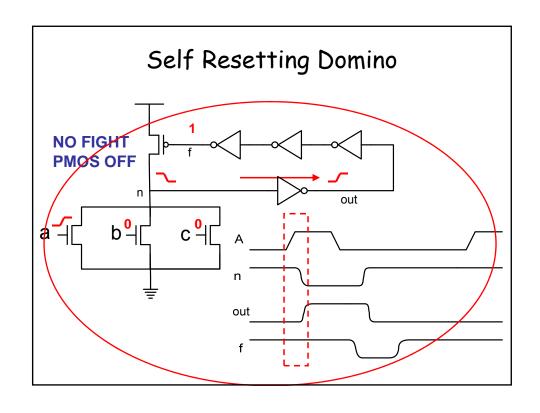

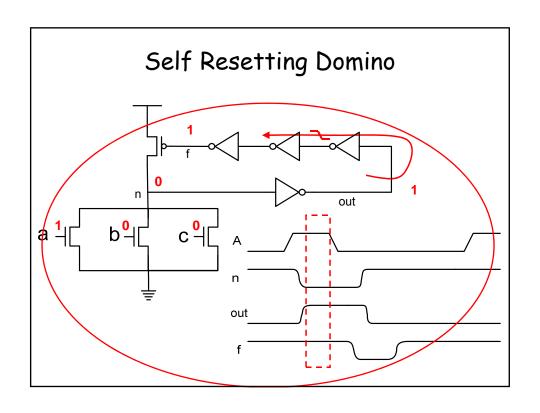

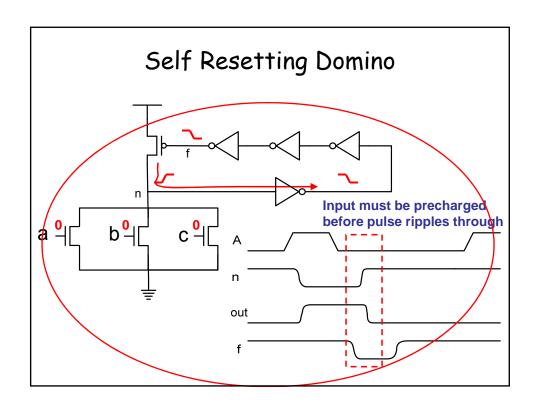

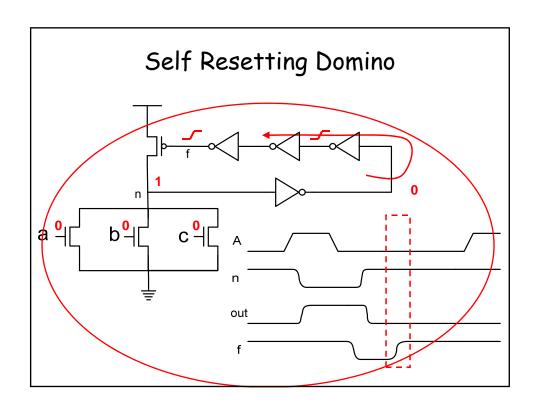

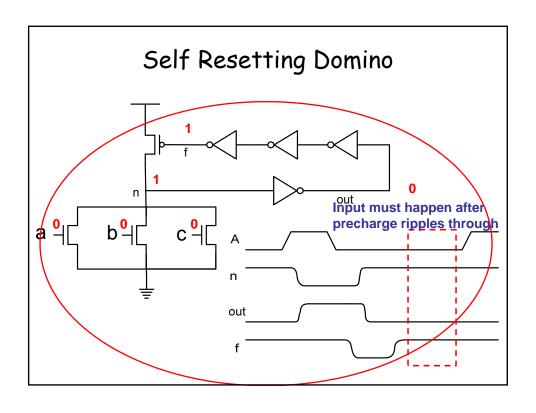

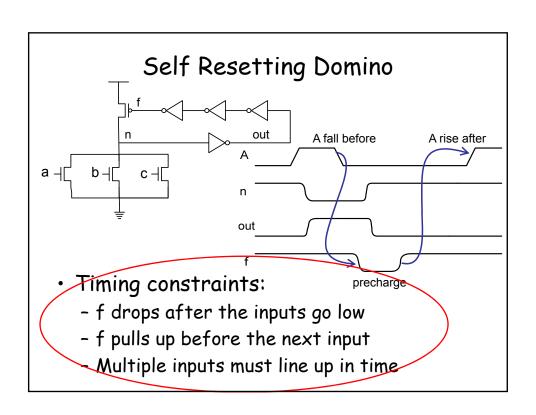

### Self Resetting Domino

- Advantages:

- No clock

- Fast eval because no footer

- More time for pre-charge than standard footless domino

#### Self Resetting Domino

- Disadvantages:

- Timing constraints

- Stability after precharge

- Sensitive to process variations

- Very difficult in practice -> pulse everything

#### Lecture 12 -Static Power

WH 5.3

Adapted from Weste & Harris, and Rabaey & Chandrakashan

Prof. Pinaki Mazumder

# **Topics**

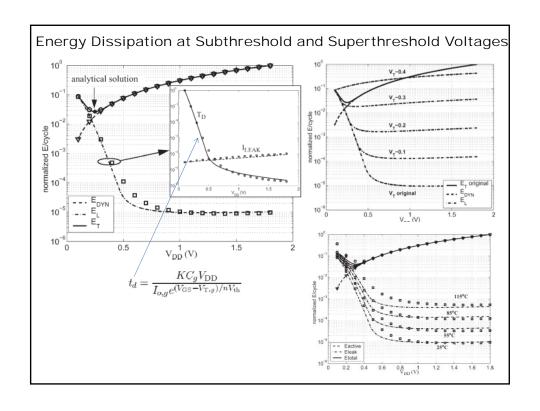

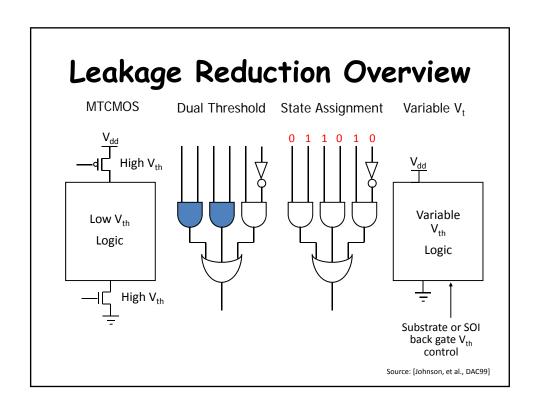

- Leakage mechanisms

- Subthreshold leakage

- Gate oxide leakage

- Leakage reduction methods

- State assignment

- MTCMOS

- Dual-Vth design

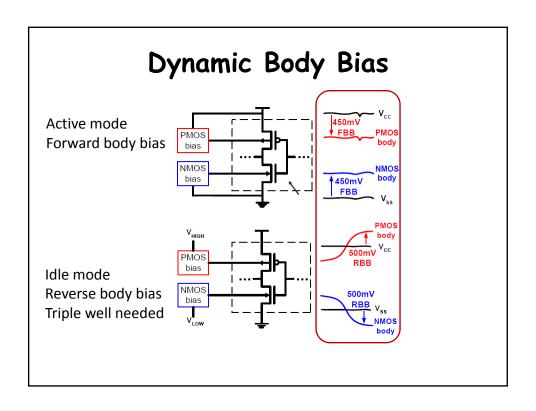

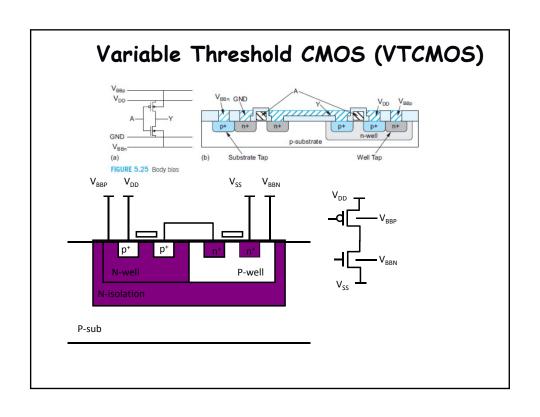

- VTCMOS

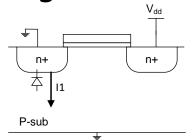

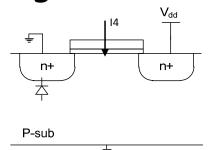

# Leakage mechanisms

- I1: Reverse-bias p-n junction

- Reverse-biased p-n junctions current:  $I_D = I_S \left( e^{v_T} 1 \right)$

- Typically < 1 fA/mm² (negligible)

- Depends on area and perimeter of diffusion regions

- Also: Band to Band tunneling (BTBT)

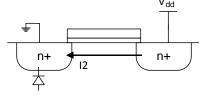

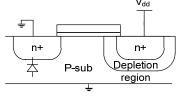

# Leakage mechanisms

P-sub

- I2: Weak inversion or subthreshold leakage current

- Increased voltage increases drain depletion extending to the source → lowers the potential barrier

- Dominant effect in modern devices

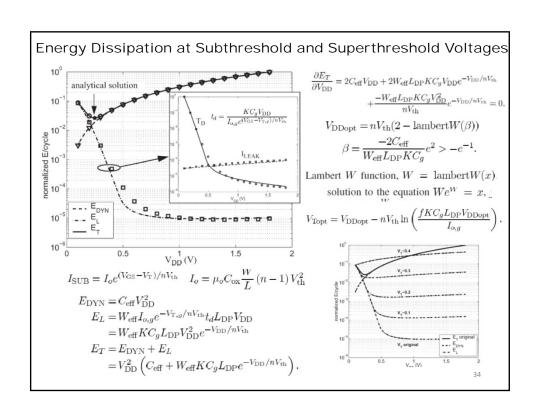

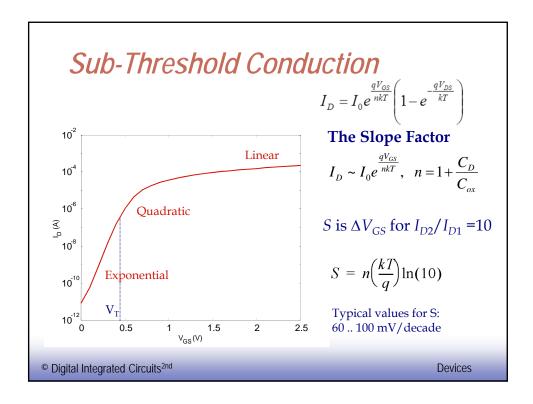

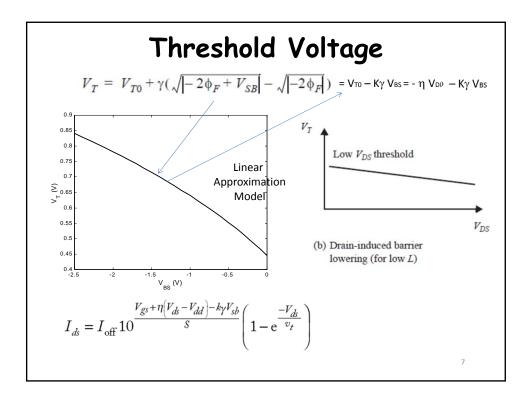

# Subthreshold Leakage

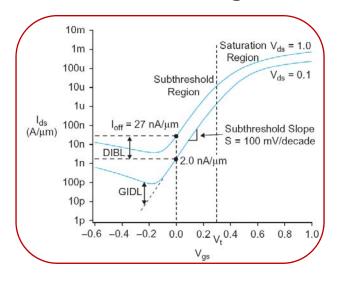

• Subthreshold leakage exponential with V<sub>gs</sub>

$$I_{ds} = I_{ds0} e^{\frac{V_{gs} - V_{t0} + \eta V_{ds} - k_{y} V_{sb}}{n v_{T}}} \left( 1 - e^{\frac{-V_{ds}}{v_{T}}} \right)$$

- n is process dependent - typically 1.3-1.7

$$- v_T = kT/q$$

See next page for explanation.

threshold voltage: V<sub>t0</sub>

$$I_{ds} = I_{\text{off}} 10^{\frac{V_{gs} + \eta \left(V_{ds} - V_{dd}\right) - k\gamma V_{sb}}{S}} \left(1 - e^{\frac{-V_{ds}}{v_t}}\right) S = \left[\frac{d\left(\log_{10} I_{ds}\right)}{dV_{gs}}\right]^{-1} = nv_T \ln 10$$

• S ≈ 100 mV/decade @ room temperature

The threshold voltage decreases with increasing  $V_{DS}$ . This effect, called the drain-induced barrier lowering, or DIBL, causes the threshold potential to be a function of  $V_{DS}$

#### Drain-Induced Barrier Lowering (DIBL)

$$I_{ds} = I_{\text{off}} 10^{\frac{V_{gs} + \eta \left(V_{ds} - V_{dd}\right) + k\gamma V_{sb}}{S}} \left(1 - e^{\frac{-V_{ds}}{v_t}}\right)$$

• Electric field from drain affects channel

- More pronounced in small transistors where drain to channel coupling is stronger

- Drain-Induced Barrier Lowering effectively reduces threshold voltage

- High drain voltage causes leakage to increase.  $V_t = V_t$

3

#### Body Coefficient / Vds Dependence

$$I_{ds} = I_{\text{off}} 10^{\frac{V_{gs} + \eta(V_{ds} - V_{dd}) + (k_{\gamma}V_{sb})}{S}} \left(1 - e^{\frac{-V_{ds}}{v_t}}\right)$$

$$V_T = V_{T0} + \gamma(\sqrt{|-2\phi_F + V_{SB}|} - \sqrt{|-2\phi_F|})$$

- For NMOS: lower body voltage relative to source voltage (reverse bias)

- Increases effective Vth

- Reduces leakage

- Vds dependence

- For Vds > 4 VT leakage current independent of Vds (other than DIBL)

- For Vds < 2 VT leakage current drops rapidly with lower Vds</li>

9

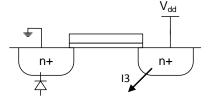

# Leakage Mechanisms

P-sub

- I3: GIDL Gate Induced Drain Leakage

- Negative gate / Positive drain

- Thins out drain depletion causing drain to well leakage near gate

- Generates a tunneling current

# Subthreshold Leakage Roundup

11

# Subthreshold Leakage

For V<sub>ds</sub> > 50 mV

$$I_{sub} \approx I_{off} 10^{\frac{V_{gs} + \eta(V_{ds} - V_{DD}) - k_{\gamma}V_{sb}}{S}} I_{off} = 100 \text{ nA/}\mu\text{m} @ V_{th} = 0.3 \text{ V} \\ I_{off} = 10 \text{ nA/}\mu\text{m} @ V_{th} = 0.4 \text{ V} \\ I_{off} = 1 \text{ nA/}\mu\text{m} @ V_{th} = 0.5 \text{ V}$$

Typical values in 65 nm

•  $I_{off}$  = leakage at  $V_{gs}$  = 0,  $V_{ds}$  =  $V_{DD}$

DIBL coefficient:  $\eta = 0.1$ Body effect coefficient:  $k_y = 0.1$ S = 100 mV/decade

# Leakage Mechanisms

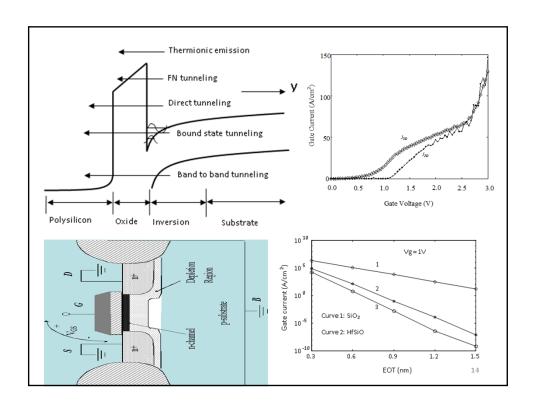

- I4: Gate Oxide tunneling

- Thinner oxides cause an increase tunneling

- Highly dependent on oxide material and thickness

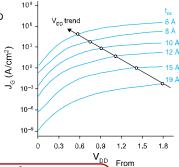

## Gate Leakage

- Carriers tunnel thorough very thin gate oxides

- Exponentially sensitive to t<sub>ox</sub> and V<sub>DD</sub>

$$I_{\text{gate}} = WA \left(\frac{V_{DD}}{t_{\text{ox}}}\right)^{2} e^{-B\frac{t_{\text{ox}}}{V_{DD}}}$$

- A and B are tech constants

- Greater for electrons

- So NMOS gates leak more

- Negligible for older processes (t<sub>ox</sub> > 30 Å)

- Critically important at 65 nm and below (t<sub>ox</sub> ≈ 12 Å)

- But: improved again with High-K metal gate transistors

15

[Song01]

#### Fundamental Leakage Levers

• Increase Vth: ~10x leakage reduction for every 100mV

– But: bad for delay

$$\tau \propto \frac{V_{dd}}{\left(V_{dd} - V_{t}\right)^{\alpha}}$$

- Reduce temperature: ~5.2X reduction / 10 degree C

- Stacking transistors

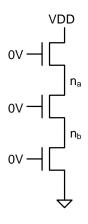

#### Stack Effect

- Series OFF transistors significantly reduce leakage

- $V_x > 0$ , so N2 has negative  $V_{gs}$

$$\begin{split} I_{\mathit{sub}} &= \underbrace{I_{\mathit{off}} \, 10^{\frac{\eta(V_x - V_{\mathit{DD}})}{S}}}_{N1} = \underbrace{I_{\mathit{off}} \, 10^{\frac{-V_x + \eta\left((V_{\mathit{DD}} - V_x) - V_{\mathit{DD}}\right) - k_y V_x}{S}}}_{N2} \quad \text{VDD} \\ V_x &= \frac{\eta V_{\mathit{DD}}}{1 + 2\eta + k_\gamma} \quad 0 - \begin{vmatrix} N_2 \\ \frac{-\eta V_{\mathit{DD}}\left(\frac{1 + \eta + k_y}{1 + 2\eta + k_y}\right)}{S} \\ = \underbrace{I_{\mathit{off}} \, 10^{\frac{-\eta V_{\mathit{DD}}}{S}}}_{S} \approx I_{\mathit{off}} \, 10^{\frac{-\eta V_{\mathit{DD}}}{S}} \\ - \text{ Leakage through 2-stack reduces $$^{\sim}$10x} \end{split}$$

17

## Stacking and Leakage

| # of stack<br>SVT | Leakage<br>current (pA) | Reduction |

|-------------------|-------------------------|-----------|

| 1                 | 258                     | X 1       |

| 2                 | 36.1                    | X 7.1     |

| 3                 | 19.8                    | X 13      |

| # of stack<br>HVT | Leakage current (pA) |       | Reduction | Reduction per HVT |  |

|-------------------|----------------------|-------|-----------|-------------------|--|

| 1                 |                      | 1.25  | X 206     | X 1               |  |

| 2                 |                      | 0.185 | X 1394    | X 6.8             |  |

| 3                 |                      | 0.122 | X 2115    | X 10.3            |  |

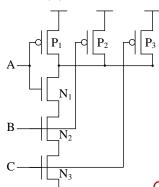

#### State Assignment

- · Only a few states have significant leakage

- Dominant leakage states have only one transistor OFF in any path from  $V_{\text{dd}}$  to Gnd

| Α | В | С | Leakage Current | Leaking Transistors |

|---|---|---|-----------------|---------------------|

| 0 | 0 | 0 | 10.537          | N1, N2, N3          |

| 0 | 0 | 1 | 18.534          | N1, N2              |

| 0 | 1 | 0 | 18.234          | N1, N3              |

| 0 | 1 | 1 | 135.772         | N1                  |

| 1 | 0 | 0 | 20.350          | N2, N3              |

| 1 | 0 | 1 | 102.672         | N2                  |

| 1 | 1 | 0 | 100.970         | N3                  |

| 1 | 1 | 1 | 192.174         | P1, P2, P3          |

Leakage currents in pA. NMOS width = 480nm PMOS width = 320nm

#### State Dependence of Leakage

- Circuit state is partially unknown in sleep state

- Leakage variation is less for entire circuit than for individual gates

|         | Lea    | Leakage Current (nA) |        |           |

|---------|--------|----------------------|--------|-----------|

|         | Min    | Mean                 | Max    | Max / Min |

| Adder1  | 256.8  | 283.1                | 309.8  | 1.2       |

| Control | 33.8   | 45.97                | 60.23  | 1.78      |

| Decoder | 1702.5 | 1914.3               | 2122.1 | 1.25      |

| Nand4   | 0.07   | 0.76                 | 7.1    | 101.4     |

| OAI21   | 0.84   | 7.73                 | 17.78  | 21.2      |

| Tinv    | 0.37   | 1.89                 | 5.76   | 15.6      |

| AOI21   | 2.44   | 8.51                 | 17.23  | 7.1       |

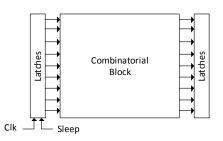

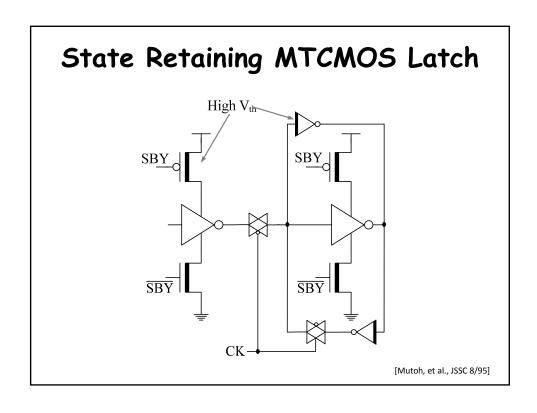

#### State Assignment

- Since the leakage of a logic gate depends on its input, find the input to a combinational circuit that minimizes leakage

- 30%-40% leakage variation depending on input vector

- Modify latches

- Sleep signal moves pre-determined values as inputs into combinational circuit

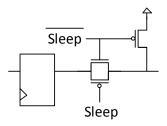

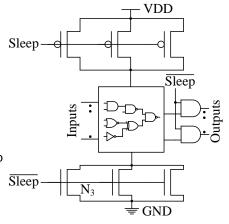

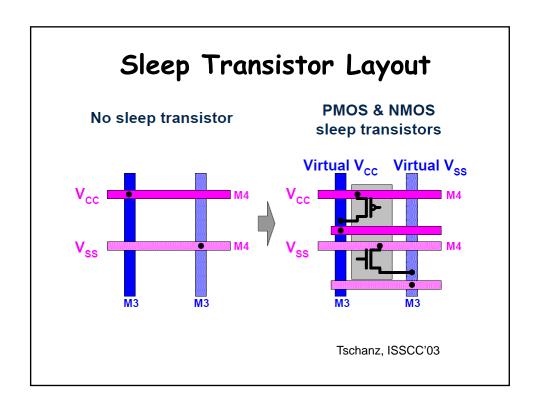

# Power Gating - aka MTCMOS

- Turn OFF power to blocks when they are idle

- Use virtual  $\rm V_{\rm DD}$  and Gnd

- "Gate" outputs to prevent invalid logic levels at next block

- Use HVT header/footer

- Voltage drop across sleep transistor during normal operation

- Size the transistor wide enough to minimize impact

- Switching sleep transistor costs dynamic power

- Only justified when circuit sleeps long enough

22

#### Dual-Thresholds Inside a Logic Block

- Minimum energy consumption is achieved if all logic paths are critical (have the same delay)

- Use lower threshold on timing-critical paths

- Assignment can be done on a per gate or transistor basis; no clustering of logic is needed

- No level converters needed

# V<sub>th</sub> Assignment Granularity

- V<sub>th</sub> assignment can be performed at different levels of granularity

- Gate level assignment

- Pull up network / Pull down network based assignment (half gate)

- Single V<sub>th</sub> in pull up or pull down networks

- Stack based assignment

- Single V<sub>th</sub> in series connected transistors

- Individually assignment within transistor stacks

- Possible area penalty (see right)

Design rule constraint for different V<sub>t</sub> assignment

- Number of library cells increases with finer control

- Better leakage / delay trade-off

- Harder for synthesis tools to handle

| Power | and | Energy | Design | Space |

|-------|-----|--------|--------|-------|

|-------|-----|--------|--------|-------|

|         | Constant<br>Throughput/Latency        |                                                                         | Variable<br>Throughput/Latency             |

|---------|---------------------------------------|-------------------------------------------------------------------------|--------------------------------------------|

| Energy  | Design Time                           | Non-active<br>Modules                                                   | Run Time/Adaptive                          |

| Active  | Logic Design Sizing Low C circuits    | Clock Gating                                                            | DVFS<br>(Dynamic Freq,<br>Voltage Scaling) |

| Leakage | Multi-V <sub>th</sub><br>Stack effect | Sleep<br>Transistors<br>State<br>assignment<br>Variable V <sub>th</sub> | Variable V <sub>th</sub>                   |

#### **Conclusions**

- Lots of recent work on circuit and technology techniques to reduce static power

- Standby mode leakage reduction can be orders of magnitude, may lose state, takes time to switch in and out of standby mode

- Active mode leakage reduction is a tougher problem, smaller savings (<50% typically), must be ready for inputs to toggle at any time