#### **Competitors/Partners**

PartnerS: Cadence, Magma Design Automation, Avanti, Mentor Graphics, Synopsys, Monterey Design Systems, InChip, VLSI Technology, etc.

**Competitors:** Artisan Components, Virage Logic, Virtual Silicon Technology, Nurlogic Design, Duet Technology, Legend Design Technology

University of Michigan

#### BisramGen -

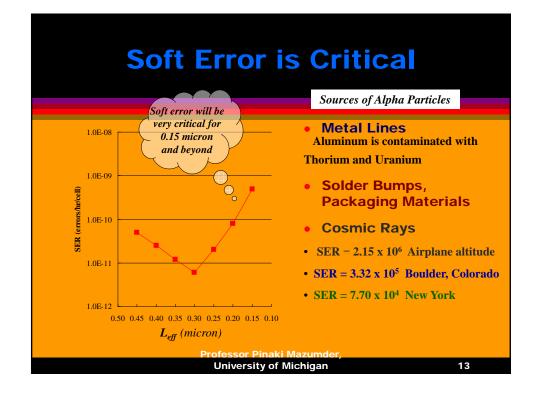

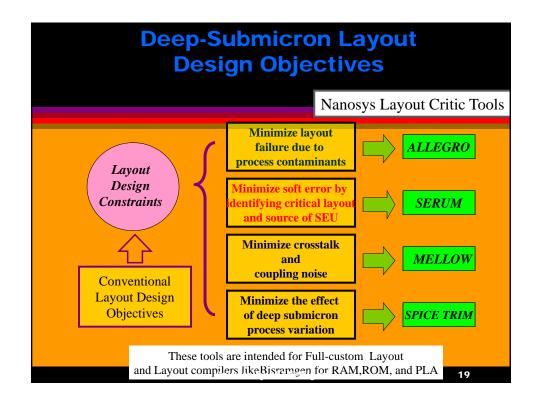

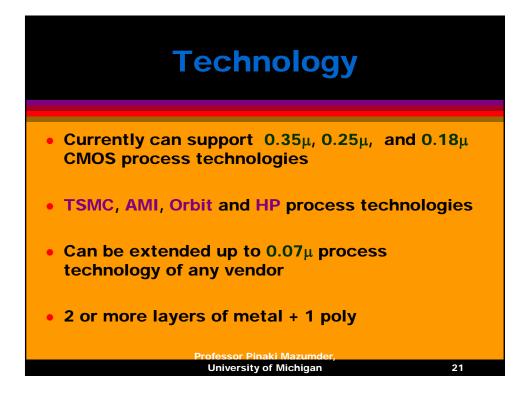

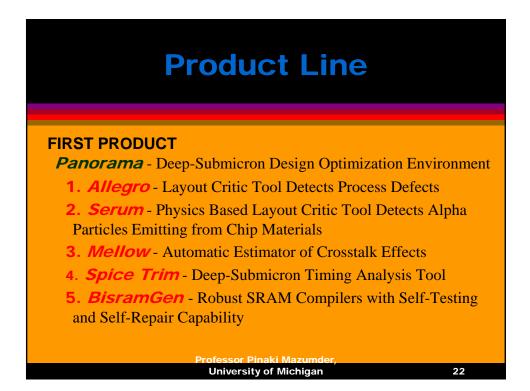

1. Robust SRAM compilers with self-testing and self-repair capability; 2. On-line timing analysis by *Spice Trim* for deep-submicron process parameter scattering and device stress analysis; 3. Cell layout criticing by *Allegro* to eliminate defects resulting from process contaminants; 4. Early estimation of alpha particle induced soft errors and layout refinement by *Serum*; 5. Bit-line coupling and power-bus noise estimation by *Mellow*; 6. VHDL/Verilog Model; 7. GDS and CIF layout output files.

University of Michigan

24

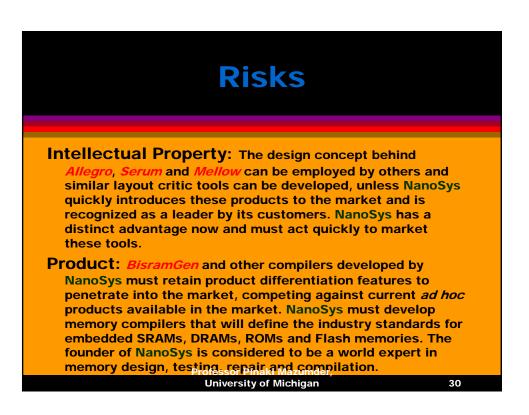

## **Risks**

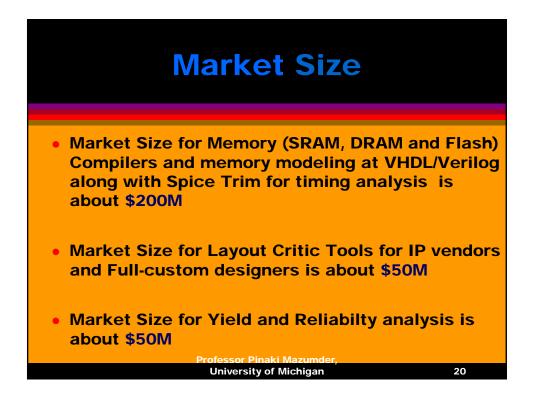

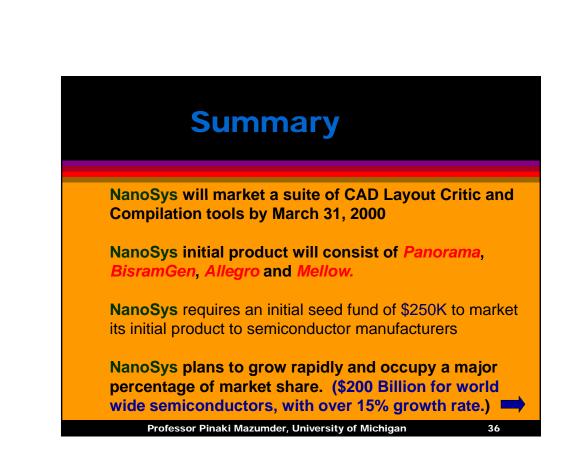

Market: The usefulness of *Panorama* will depend on how effective *Allegro, Serum* and *Mellow* are in improving the reliability and yield of deep-submicron VLSI chips.Though NanoSys tools will be superior to existing tools like memory compilers, the overall market size of these tools will to a great extent depend on whether NanoSys layout critic tools can also be used for improving the quality of ASIC and highperformance layout tools

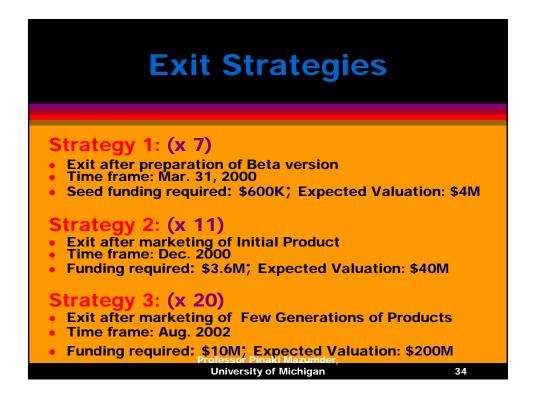

**Funding:** Seed funding will be required to market the initial product. In order to grow rapidly, VC funding of a few million dollars will be needed. The success of NanoSys will not only depend on the quality of its tools, but also on its marketing crew who must develop appropriate marketing strategies to tie up these tools with its partners and to directly reach to the IP core users.

**University of Michigan**

## Mazumder Group Research Team

Research Team Members who have Worked on BISRAMGen and Other CAD Tools: 1. Prof. P. Mazumder, 2. Dr. M. Bhattacharya, Ph.D.; 3. Dr. S. Kulkarni, Ph.D.; 4. Dr. A. Gonzalez, Ph.D.; 5. Mr. V. Warraich, M.S.; 6. Mr. L. Ding, M.S.; 7. S. Mohan, Ph.D. (working at Xilinx for 5 years); 8. K. Chakraborty, Ph.D. (working at IBM for 3 years); 9. J. S.Yih, Ph.D. (working at IBM for 9 years); 10. H. Esbensen, Ph.D. (working at Avanti for 4 years); 11. V. Ramachandran, Ph.D. (working at Cadence for 5 years); 12. A. Gupta; 13. H. Chan, M.S. (working in Intel for 10 years); 14. M. D. Smith, M.S. (working at Intel for 5 years);

University of Michigan

# **Semiconductor Industry Growth**

|                                   | <u>1995</u> | <u>2030</u>                |

|-----------------------------------|-------------|----------------------------|

| Semiconductor as % of Electronics | 17%         | 35%                        |

| Electronics as % of GWP           | 4%          | 8%                         |

| Semiconductors as % of GWP        | 0.7%        | 3%                         |

| CMOS Technology                   | 0.35µm      | 0.05µm                     |

| World Semiconductor Sales         | \$140B      | \$12,000B                  |

| Annual Growth Rate                | 16%         | 8%                         |

| Professor Pinaki                  |             | ming Hu, UC Berkeley, 1996 |

| University of I                   |             | 37                         |

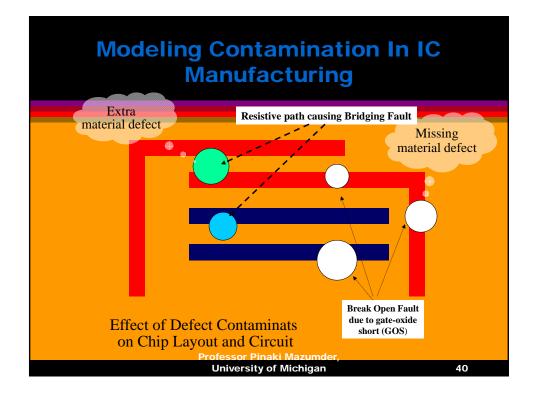

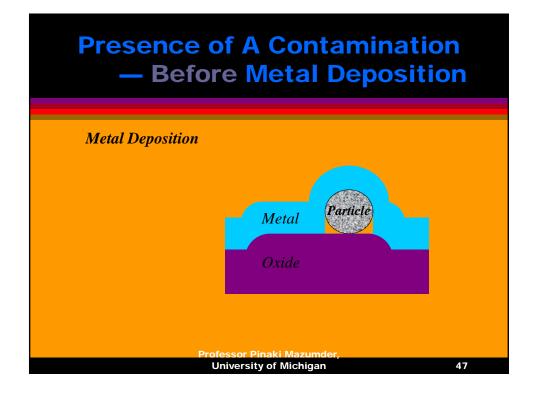

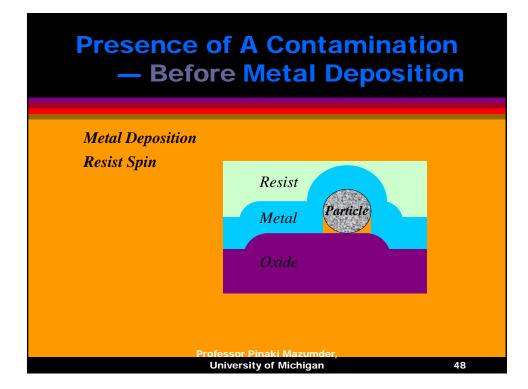

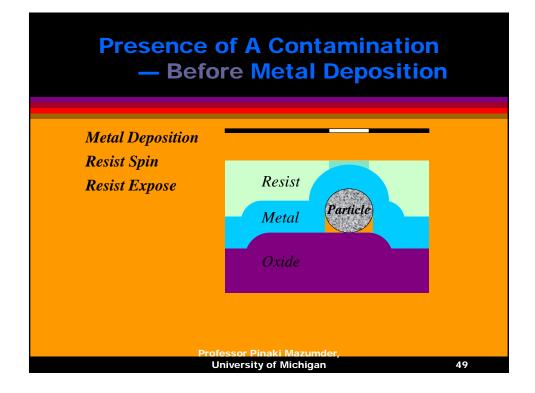

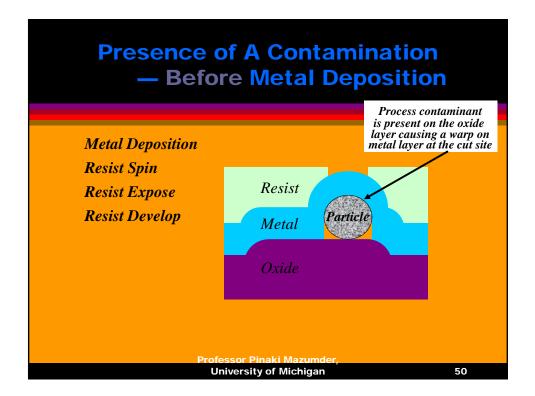

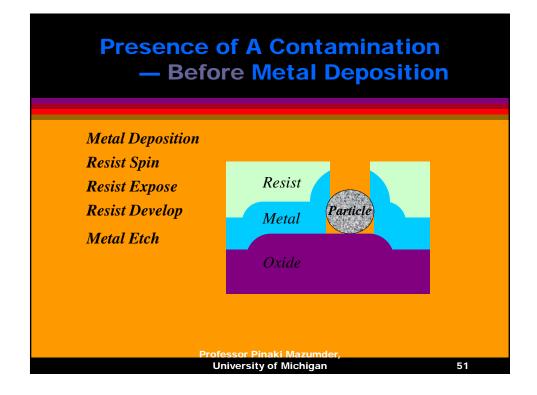

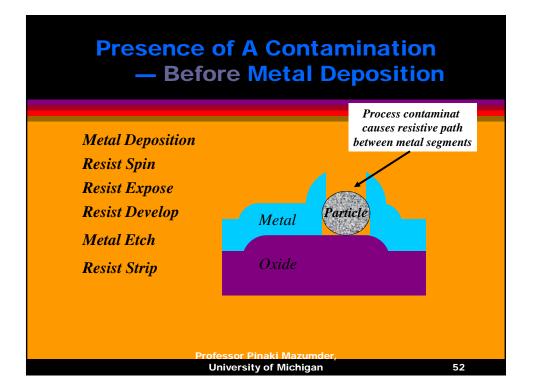

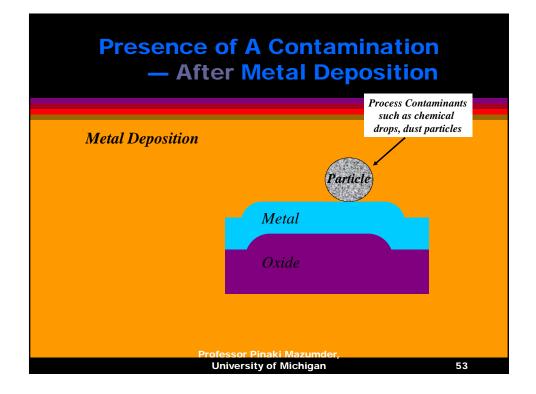

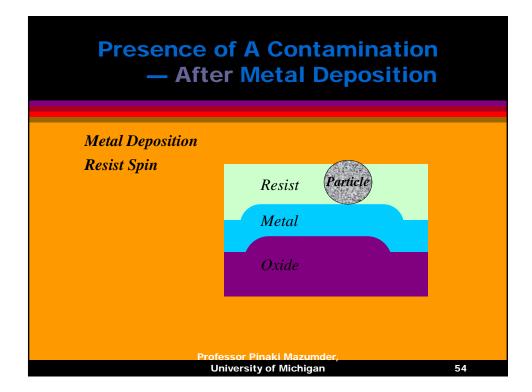

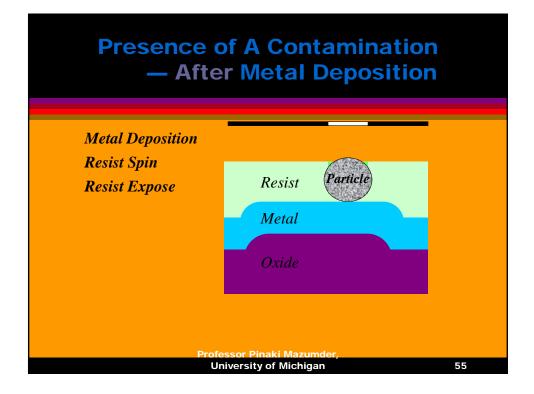

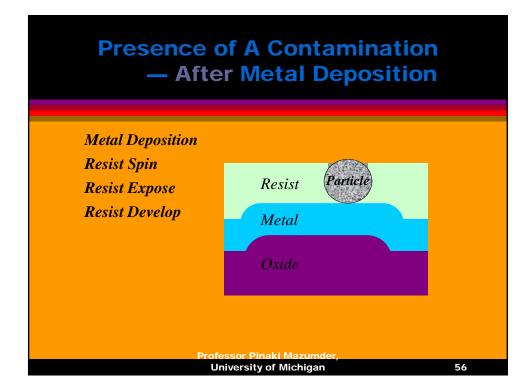

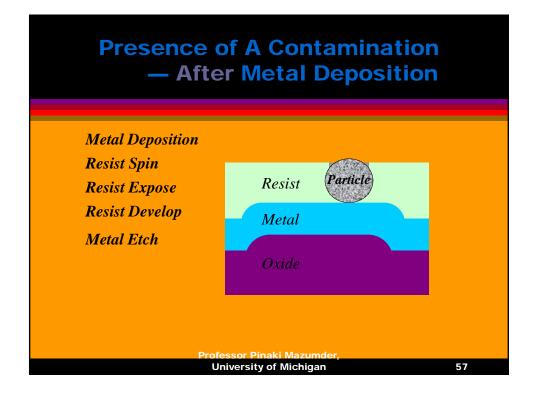

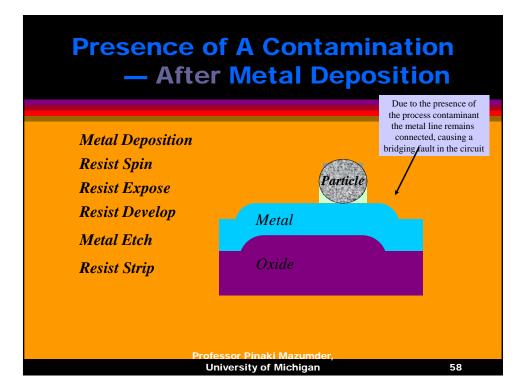

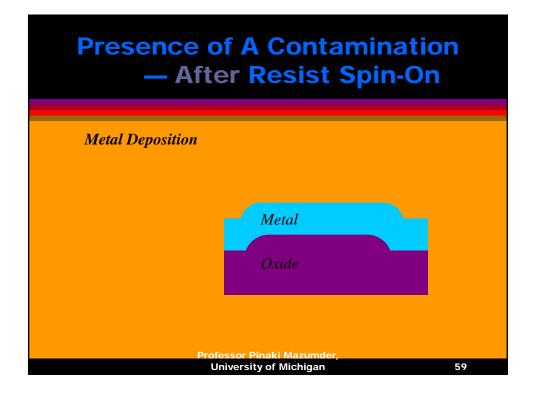

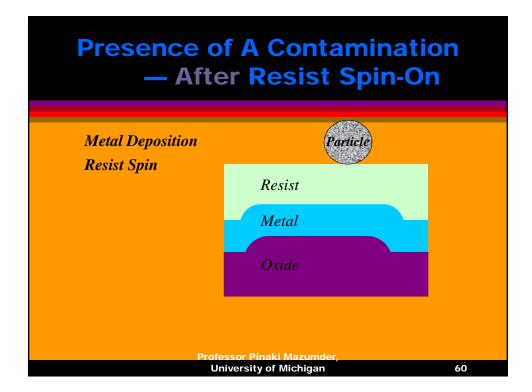

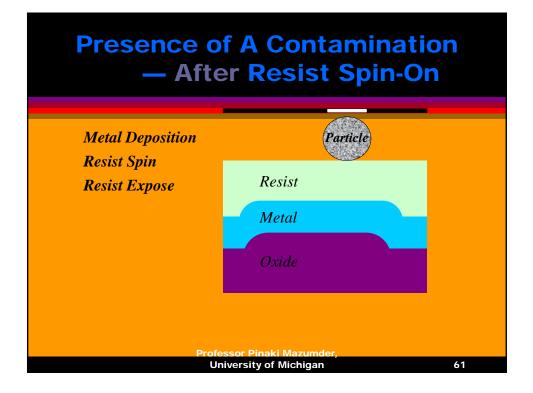

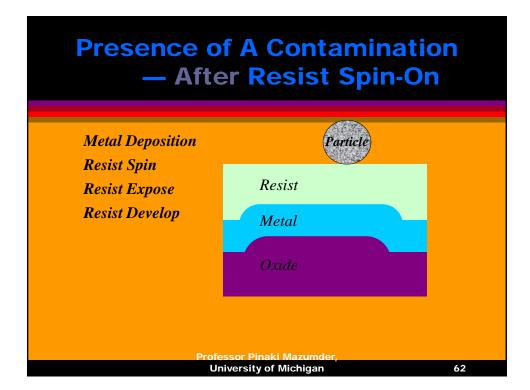

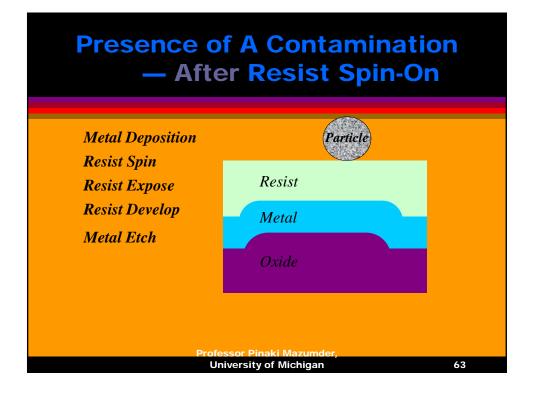

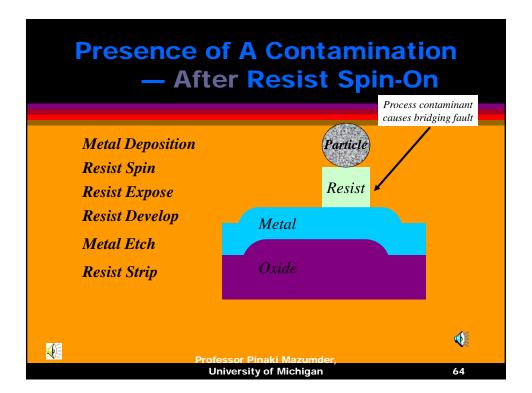

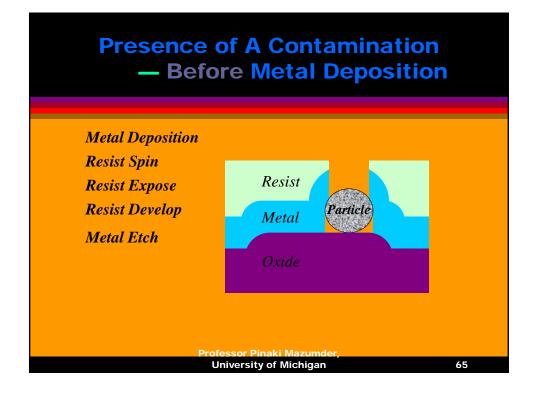

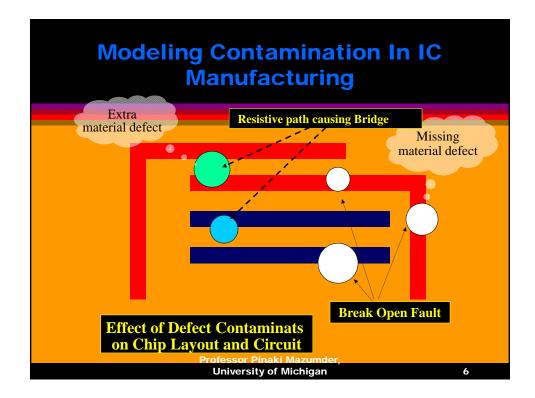

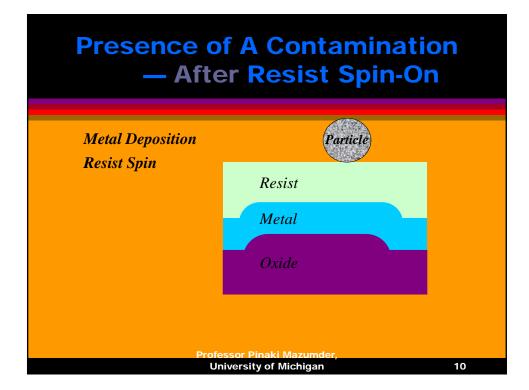

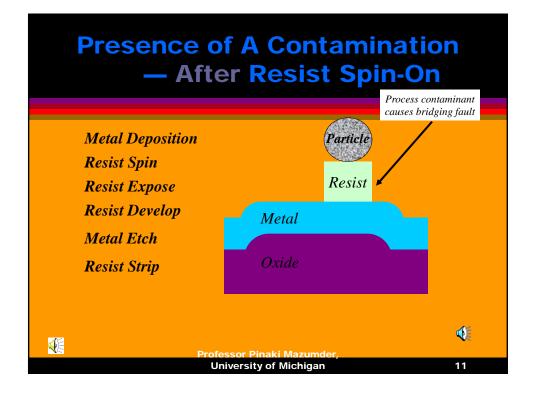

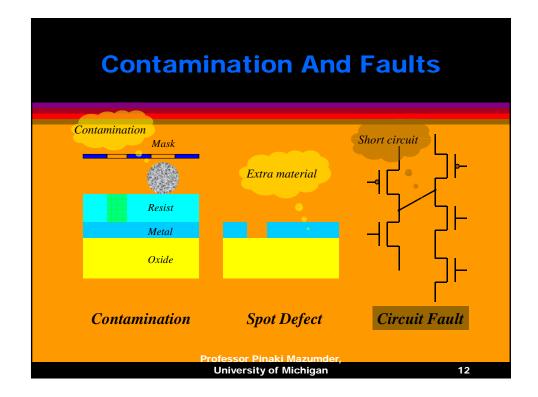

#### Modeling Contamination In IC Manufacturing

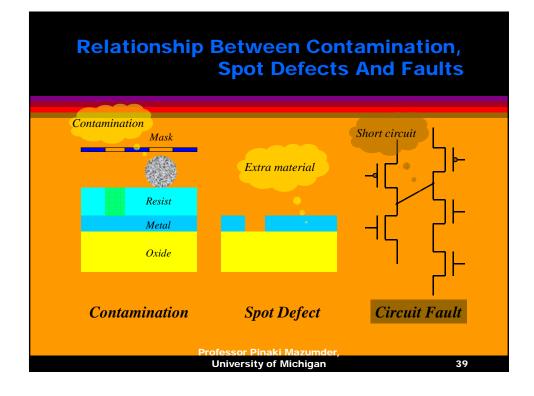

#### Terminology

*Contamination*: any particle or liquid droplet that deposits on the IC during the manufacturing process.

*Spot defect*: any contamination occurring at appropriate places on the IC that leads to deformation of IC layers.

*Fault*: A change in the functionality of the IC due to the existence of spot defects.

University of Michigan