# MPC5553

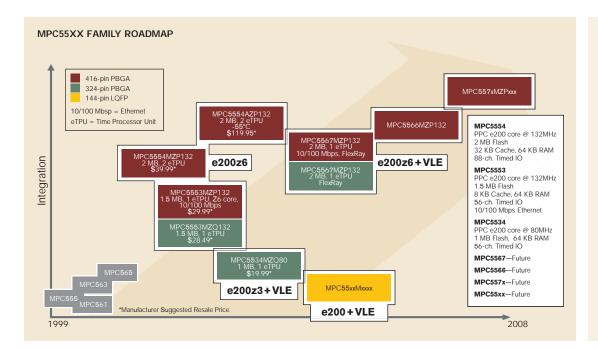

The MPC5553 32-bit embedded controller is the first device from Freescale Semiconductor's MPC55xx Family to offer an on-chip Fast Ethernet Controller (FEC). Containing the Book E compliant PowerPC™ core, the MPC5553 is ideal for any application that requires complex, real-time control and can conveniently be networked with the rest of the world. It offers system performance of up to five times that of its MPC500 predecessors, while bringing you the reliability and familiarity of the proven PowerPC architecture. The MPC5553 helps you face the dual pressures of controlling costs while designing for increasingly complex applications. This high-performance MCU delivers more on-chip functionality than the current MPC500 Family; a large block of embedded Flash; enhanced timer systems and a peripheral set specifically tailored for automotive and industrial applications. The MPC5553 offers a migration path from the market-leading MPC500 Family of 32-bit MCUs, facilitating reuse of legacy software architectures.

# **Applications**

- > Multipoint fuel injection control

- > Electronically controlled transmissions

- > Direct diesel injection (DDI)

- > Gasoline direct injection (GDI)

- > Avionics

- > Robotics

- > Motion control

- > Turbine control

- > Utilities/power management

- > Alternative energies

- > Autonomous vehicles

#### **Features**

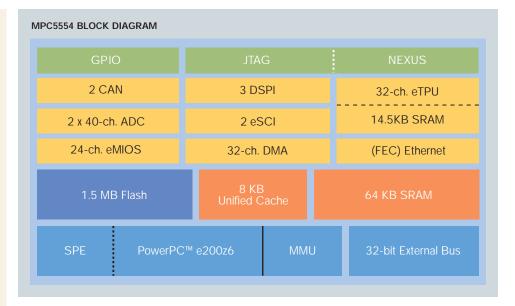

## Freescale's e200z6 Core

- > High-performance 132 MHz 32-bit PowerPC Book E-compliant core

- > Memory management unit (MMU) with 32-entry fully associative translation lookaside buffer (TLB)

- Signal processing extension (SPE):DSP, SIMD and floating point capabilities

#### Memory

- > 1.5 MB of embedded Flash memory with Error Correction Coding (ECC) and Read While Write capability (RWW)

- > 64 KB on-chip static RAM with ECC

- > 8 KB of cache (with line-locking) that can be configured as additional RAM

# System

> An enhanced time processor unit (eTPU) with 32 I/O channels and 14.5 KB of designated SRAM

- > 32-ch. eDMA (Enhanced Direct Memory Access) controller

- Interrupt controller (INTC) capable of handling 210 selectable-priority interrupt sources

- > Frequency modulated phase-locked loop (FMPLL) to assist in electromagnetic interference (EMI) management

- > MPC500 compatible external bus interface

- > Nexus IEEE-ISTO 5001™ Class 3+ multicore debug capabilities

- > 5/3.3V IO, 5V ADC, 3.3V/1.8V bus, 1.5V core

- > 416-pin PBGA or 324 pin PBGA package

- > Temperature range: -40 to 125°C

- > Optional temperature range: -55 to 125°C

Except for historical information, all of the expectations and assumptions contained in the foregoing are forward-looking statements involving risk and uncertainties. Important factors that could cause actual results to differ materially from such forward-looking statements include, but are not limited to, the competitive environment for our products, changes of rates of all related services, and legislation that may affect the industry. For additional information regarding these and other risks associated with the Company's business, refer to the Company's reports with the SEC.

#### 1/0

- > 40 ch. dual Enhanced queued analog-todigital converter (eQADC—up to 12-bit resolution and up to 1.25ms conversions, six queues with triggering and DMA support

- > Three deserial serial peripheral interface (DSPI) modules—16 bits wide up to six chip selects each

- > Two controller area network (CAN) modules with 64 buffers each

- > Two enhanced serial communication interface (eSCI) modules

- > 24-ch. enhanced multiple I/O system (EMIOS) with unified channels

#### Benefits

#### Excellent system performance:

Book E superscalar compliant with the PowerPC core includes integrated DSP features and upgraded interrupt control

#### Cost-effectiveness:

Integrates more functionality on-chip. Functions previously performed in external analog hardware have been moved into software.

### Flexibility:

Supports multiple protocols and customer requirements through intelligent subsystems

#### Scalability and compatibility:

Core- and platform-based architecture enables simple derivative development. Leverages past engineering investments and existing PowerPC architecture knowledge to create a solid migration path for MPC500 users.

### Ease of use:

5V interfaces to allow use of legacy sensor and I/O systems

# **Development Support**

A comprehensive suite of hardware and software development tools for the MPC5553 is available to help simplify and speed system design. Development support is available through leading independent tools vendors providing compilers, debuggers, simulation environments, as well as other more advanced or specific development tools. In addition to the standard evaluation kit

which comes with the CodeWarrior™ compiler offering, Green Hills Software and iSYSTEM both provide individual evaluation kits to offer a uniquely catered out-of-box experience.

#### Committed to You for the Long Run

Freescale understands your top priority:

Design higher performance products in less time and at a reduced total cost. The MPC5500 Family enables you to buy as much or as little performance as you need to help meet your product development goals. Its migration path from the MPC500 Family means time and resources already invested in the PowerPC instruction-set architecture won't be wasted.

#### Learn More

For more information about the MPC5554, the MPC55xx Family and the services and support available for them, visit us at www.freescale.com/mcu.

For more information, please contact your local Freescale sales office.

Learn More: For more information about Freescale products, please visit www.freescale.com.