|          | EECS 312<br><i>igital Integrated Circuits</i>                               |   |

|----------|-----------------------------------------------------------------------------|---|

|          | Instructor's Name:                                                          |   |

|          | Prof. Pinaki Mazumder<br><u>mazum@eecs.umich.edu</u><br>T,Th 3:00 - 4:30 pm |   |

| EECS 312 | Lecture 1                                                                   | 1 |

| Lecture | Date | Topic                             | Text         | Homework |

|---------|------|-----------------------------------|--------------|----------|

| 1       | 1/05 | Course intro, digital IC overview | 1.1, 1.2     |          |

| 2       | 1/10 | Overview of CMOS circuits         | notes        |          |

| 3       | 1/12 | PN junction & MOSFET Theory I     | 3.3          |          |

| 4       | 1/17 | MOSFET Theory II                  | 3.3          |          |

| 5       | 1/19 | CMOS fabrication                  | 3.3, notes   | HW #1    |

| 6       | 1/24 | Device fab (cont.), scaling,      | 2.2, 2.3     |          |

|         |      | SPICE models notes                |              |          |

| 7       | 1/26 | CMOS inverter, VTC                | 5.1-5.3      |          |

| 8       | 1/31 | CMOS inverter, delay analysis     | 5.4          | HW #2    |

| 9       | 2/2  | CMOS inverter, power analysis     | 5.5.1        |          |

| 10      | 2/7  | CMOS gates, delay                 | 6.1, 6.2.1   |          |

| 11      | 2/9  | CMOS gates, power                 | 6.2.1        | HW #3    |

| 12      | 2/14 | Scaling intro + PVT; process      | 3.4, 5.6     |          |

|         |      | corners notes                     |              |          |

| 13      | 2/16 | Dynamic logic, pass-transistor    | 6.2.3        |          |

| 14      | 2/21 | Dynamic logic, domino, np-cmos    | 6.3, 6.4.1   | HW #4    |

| 15      | 2/23 | Comparisons between dynamic       | notes        |          |

|         |      | and CMO5                          |              |          |

| 16      | 3/07 | Low-power design techniques       | 6.4.2,       |          |

|         |      |                                   | notes        |          |

| 17      | 3/09 | Wire parasitics                   | 4.3, 4.4     | HW #5    |

| 18      | 3/14 | Interconnect issues; noise, RC    | 9.2, 9.3     |          |

|         |      | delay                             | notes        |          |

| 19      | 3/16 | Interconnect issues: repeaters    | 9.3, notes   |          |

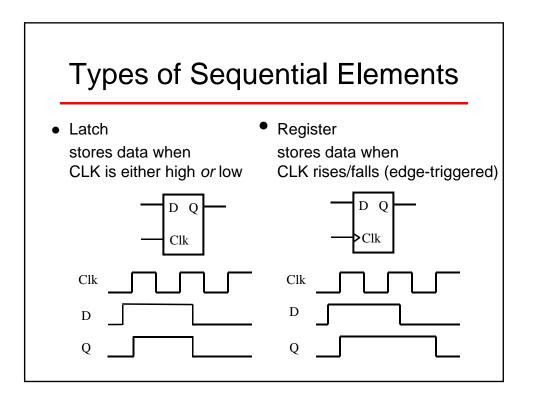

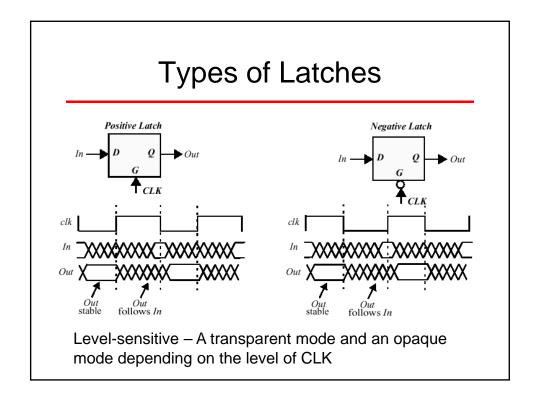

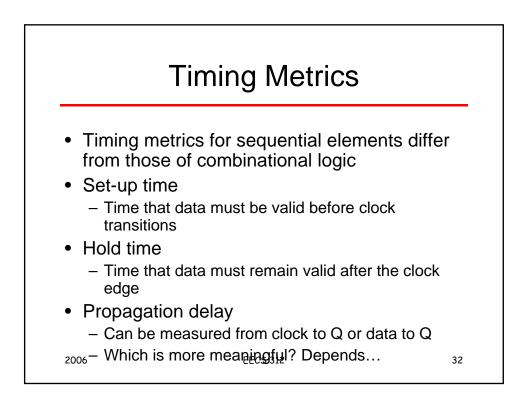

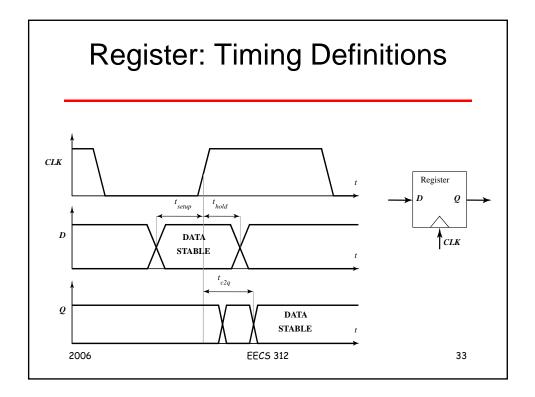

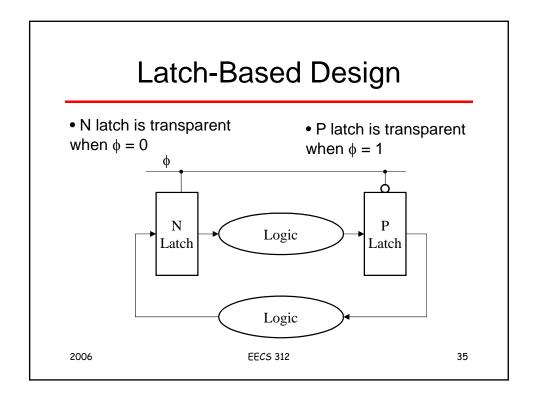

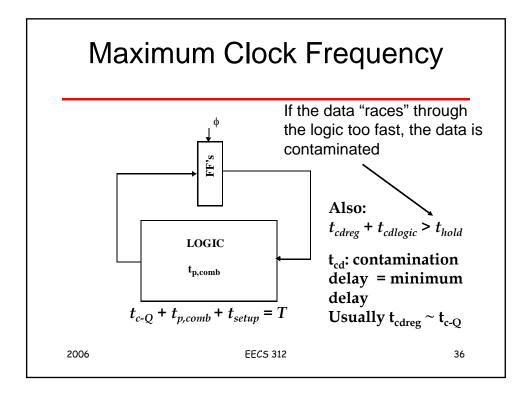

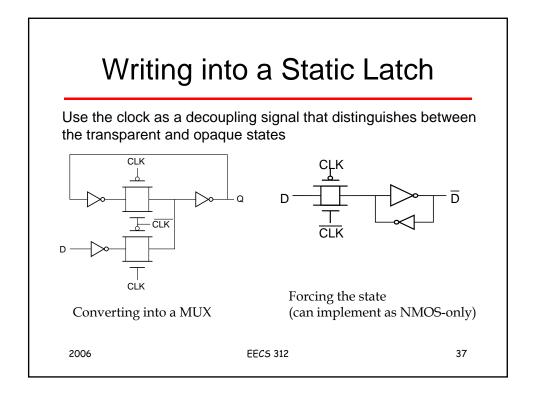

| 20      | 3/21 | Sequential elements: latches      | 7.1, 7.2.1,  | HW #6    |

|         |      |                                   | 7.2.2        |          |

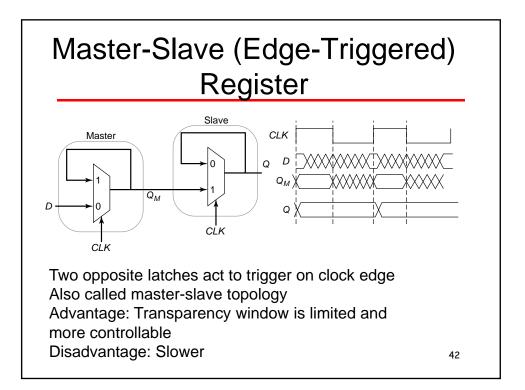

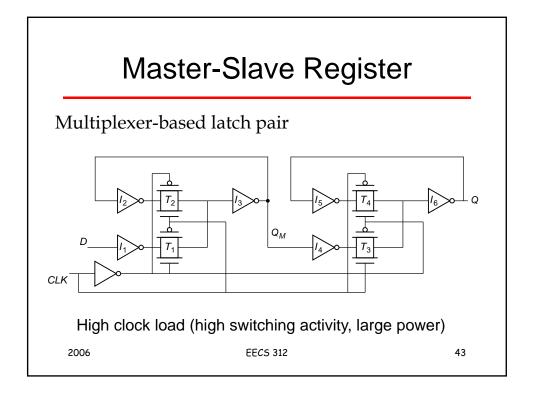

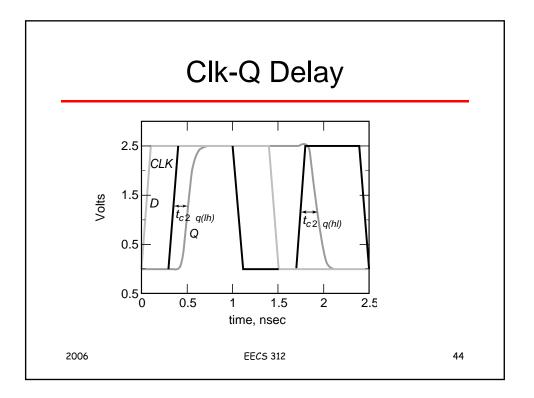

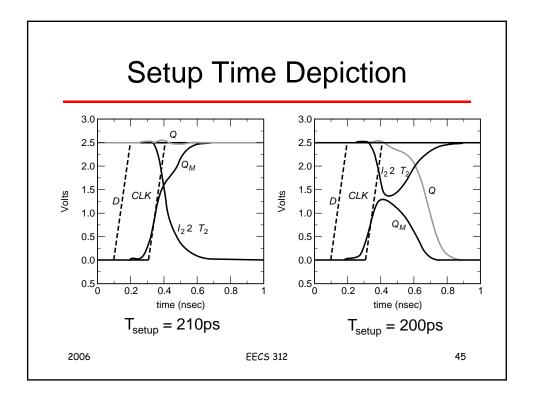

| 21      | 3/23 | Sequential elements: flip-flops   | 7.2.3, 7.2.5 |          |

| 22      | 3/28 | Other sequential elements         | 7.3.2, 7.5,  |          |

|         |      |                                   | 7.6          |          |

| 23      | 3/30 | More Sequential Elements          | notes        | HW #7    |

| 24      | 4/04 | Memories, ROMs                    | 12.1, 12.2.1 |          |

| 25      | 4/06 | Memories, SRAM                    | 12.2.3       |          |

| 26      | 4/11 | Memories, DRAM                    | 12.2.3       | HW #8    |

| 27      | 4/13 | Course review                     |              |          |

| Merg     | ing of Technologies |   |

|----------|---------------------|---|

| Compu    | iters               |   |

| Emt      | bedded Processors   |   |

| Mic      | rocontrollers       |   |

| Commu    | unication           |   |

| Cell     | l Phone             |   |

| Int      | ernet Voice Service |   |

| Consur   | mer Electronics     |   |

| Vid      | eo Camera           |   |

| Per      | sonal Organizer     |   |

| Gan      | •                   | 8 |

| EECS 312 | Lecture 1           |   |

| Some History                                                                        | /    | and |

|-------------------------------------------------------------------------------------|------|-----------------------------------------|

| Invention of the transistor (BJT)<br>Shockley, Bardeen, Brattain – Bell Labs        | 1947 | and the second                          |

| Single-transistor integrated circuit<br>Jack Kilby – Texas Instruments              | 1958 |                                         |

| Invention of CMOS logic gates<br>Wanlass & Sah – Fairchild Semiconductor            | 1963 |                                         |

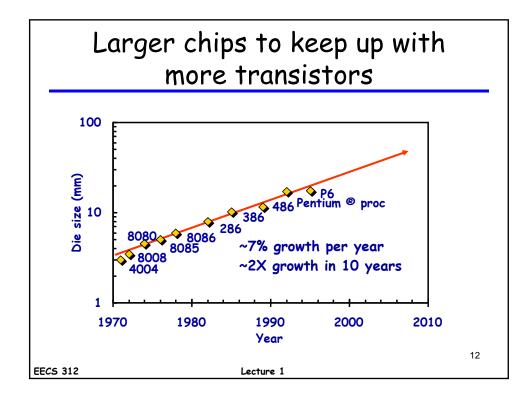

| First microprocessor (Intel 4004)<br>2,300 MOS transistors, 740 kHz clock frequency | 1970 |                                         |

| Very Large Scale Integration<br>Chips with more than ~20,000 devices                | 1978 |                                         |

| EECS 312 Lecture 1                                                                  |      | 11                                      |

| Integ                                                   | ration, Inte            | egratior    | n, and Integration       |

|---------------------------------------------------------|-------------------------|-------------|--------------------------|

|                                                         | Year of<br>Introduction | Transistors | 450000000                |

| 4004                                                    | 1971                    | 2,250       | 45000000                 |

| 8008                                                    | 1972                    | 2,500       | 40000000                 |

| 8080                                                    | 1974                    | 5,000       |                          |

| 8086                                                    | 1978                    | 29,000      | 350000000                |

| 286                                                     | 1982                    | 120,000     |                          |

| Intel386™<br>processor                                  | 1985                    | 275,000     | 30000000                 |

| Intel486™<br>processor                                  | 1989                    | 1,180,000   | 250000000 - 1982         |

| Intel <sup>®</sup> Pentium <sup>®</sup><br>processor    | 1993                    | 3,100,000   | 200000000 → 1989 → 2000  |

| Intel <sup>®</sup> Pentium <sup>®</sup><br>II processor | 1997                    | 7,500,000   | 150000000                |

| Intel® Pentium®<br>III processor                        | 1999                    | 24,000,000  | 100000000                |

| Intel <sup>®</sup> Pentium <sup>®</sup><br>4 processor  | 2000                    | 42,000,000  | 50000000                 |

| Intel <sup>®</sup> Itanium <sup>®</sup><br>processor    | 2002                    | 220,000,000 |                          |

| Intel <sup>®</sup> Itanium <sup>®</sup><br>2 processor  | 2003                    | 410,000,000 | 1971 1982 1989 2000 2003 |

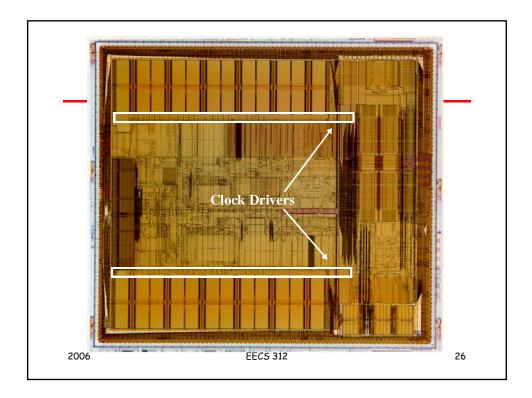

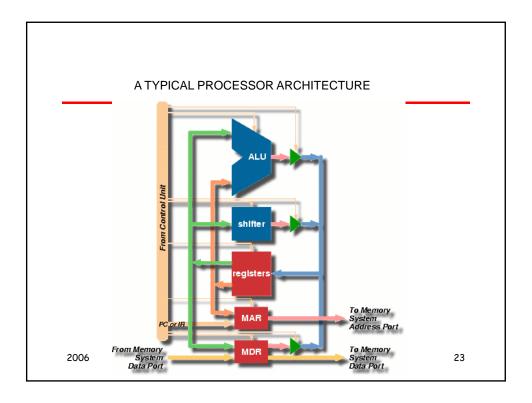

|               | 16-bit EECS 427<br>ISA Processor |

|---------------|----------------------------------|

|               | ALU                              |

|               |                                  |

|               | Shifter                          |

| 2006 EECS 312 | 24                               |

|                                                        | 16-bit EECS 427<br>ISA Processor |

|--------------------------------------------------------|----------------------------------|

| ग्रेत्वनितेष्यनित्वनित्वनित्वनित्वनित्वनित्वनित्वनित्व | Program Counter                  |

|                                                        | Register File                    |

|                                                        | 25                               |